为了确保在指定的 40 V 输出上进行安全可靠的测试,选择组件时要考虑各种操作。为了实现更大的电压测试,并展示飞跨电容器多电平转换器 (FCMFC) 如何利用与反激式转换器相同的组件更有效地执行, 本研究中未使用飞跨电容器结构带来的较低额定电压。这表明后续几代产品将通过使用 额定值较低的半导体进一步提高效率。

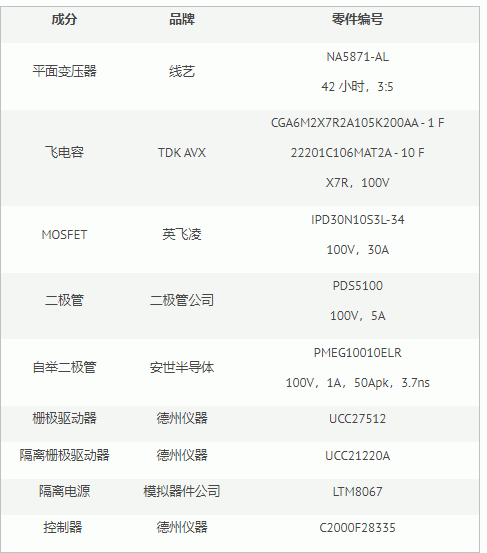

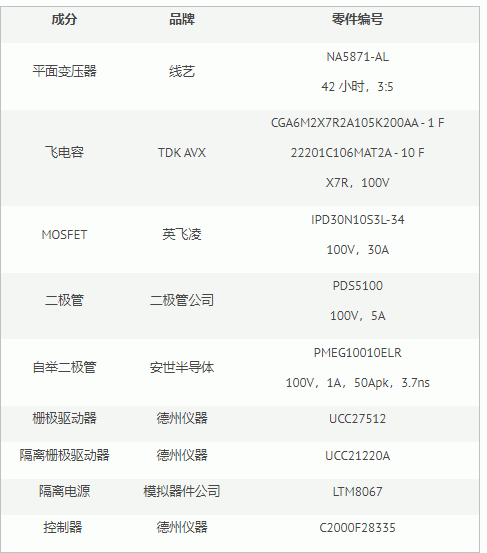

为了测试前面提到的工作原理,使用相同的组件创建了三个硬件原型,如表 1 所示。将使用反激转换器作为基准对这两个 FCMFC 进行比较。反激式配置被视为 N2 FCMFC。开发的 N3 和 N4 转换器在次级分别包含 2 个和 3 个电容器级。

控制传感

初级 FET 的相移脉冲宽度调制 (PSPWM) 控制信号和转换器次级上飞跨电容器的浮动 FET 信号由 Texas Instruments C2000 F28335 Delfino 控制开发板发送。该板由 PLEC 的编码器编程。初级 FET 设置了软启动功能,可缓慢开启双绕电感,避免因输出电容未充电而产生高浪涌电流。该计划可防止磁饱和并保护使用额定电压较低的 FET 的未来版本。每次测试试验都使用开环控制以固定占空比运行 FET。

隔离辅助电源、浮栅驱动、自举

晶体管源极节点处的浮动电压是多级结构中的一个问题。对于 FCMFC,由于需要保持初级和次级电路电气隔离,这个问题变得更加严重。幸运的是,FCMFC 不需要先进的引导技术。选择 Analog Devices 的 LTM8067 隔离

电源芯片来为自举电路提供额外的电源。该芯片被设置为将 5 V 电源升压至 8 V 并驱动次级侧的 MOSFET。

该芯片是反激式转换器,因此它保持主转换器的初级到次级隔离,额定电压为 2 kV。它具有一个电压输出,如果需要,可以使用电阻器进行调节,以在更高的电压下驱动 FET。对于这项工作,英飞凌 FET 可以使用 8 V 和 12 V 电压,该 FET 只能处理 20 V 栅极驱动。为了获得良好的电压调节,输入和输出处的电容分别为 2 F 和 30 F。

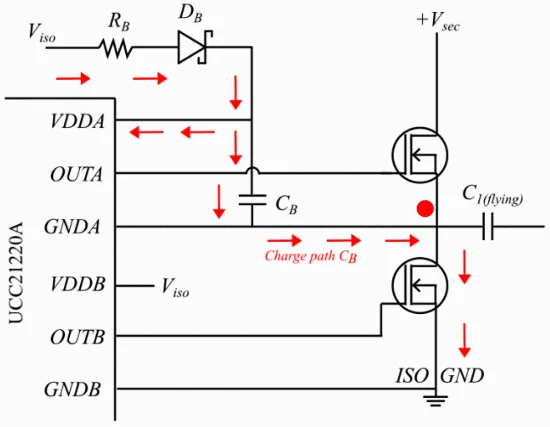

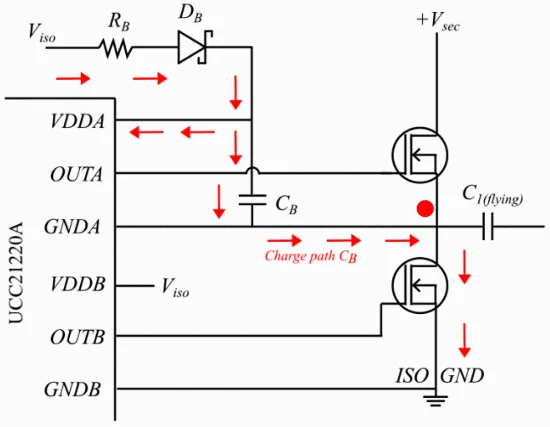

一个 20 m 的电阻器与辅助转换器的输入串联,以防止电源电感和输入电容之间可能出现谐振回路。通过选择 Texas Instruments UCC21220A 隔离栅极驱动器芯片,将浮动电压节点用作虚拟地。它们还在逻辑电平控制器输入侧和驱动飞跨电容器 MOSFET 的次级高压侧之间提供 4 kV 隔离。

每个浮动电压节点都需要一个自举,这与飞跨电容器相同。 N3 FCMFC 有一个自举电路,而 N4 转换器有两个。每个自举电路由电阻器(RB)、二极管(DB)和电容器(CB)组成。隔离的 8 V DC 电源为电阻器供电,该电阻器与二极管串联,然后与电容器串联。然后,该电容器连接到浮动源极节点,该节点是飞跨电容器 C1 的负极。这在自举电路图的图 1 中用红点表示。

图 1 . N3 的自举电路。图片由IEEE Open Journal of Power Electronics提供

CB 的正极性连接到隔离驱动芯片的输入电压节点。在此设置中,自举电路使用隔离电源对变压器的第二个接地进行充电,并且 FC 网络的所有后一个开关均打开。当后一个开关关闭时,CB 两端的电压现在为 Viso - VDB + VC1。这使得浮动 FET 栅极到源极之间的电压等于隔离电源的电压减去自举二极管两端的压降。

自举电容器足够大,可以快速充电并存储足够的能量,以保持 FET 每个周期所需的导通时间。对于更别的转换器,例如本研究中的 N4,个自举电容器(靠近

线圈)将必须通过多个 FET 充电。需要设置 PSPWM,以便自举电容器有足够的时间充电。当改变开关频率时,就像在这项工作中一样,自举电路的充电和放电时间必须平衡。

所选自举二极管的反向恢复时间为 3.7 ns,小于 FET 的有效导通时间。这样做是为了防止电流过大而损坏辅助电源。 FET 的有效导通时间包括栅极充电后漏极至源极电压下降所需的时间以及栅极电压开始时漏极至源极电压开始下降所需的时间上升。

选择自举二极管是为了在电容器充电时处理平均电流,这种情况发生在初级占空比(50%)时。二极管可以处理启动期间的峰值电流,即电源电压减去二极管的压降除以自举电阻,约为 2A。

印刷电路板布局和电容器设计

在图 2 中,三个转换器的输入位于左侧,输出位于右侧。三个转换器均位于一块 4 层 PCB 上。从上到下分别是N4、N3、N2(反激式)。黄线是 14 AWG 电流跳线,用于测量初级和次级电流的电流互感器测试探头。三个转换器之间没有电气连接。每个有源器件都有用于缓冲电路的 RC 焊盘。根据分析,飞跨电容器和输出电容器选择在 20-30 F 之间,以获得 2.5% 的纹波。添加了更多焊盘(1 F 和 10 F),以根据设备的工作情况和实验来微调电容。

图2 .印刷电路板 N2(底部)、N3(中)和 N4(顶部)。图片由IEEE Open Journal of Power Electronics提供

缓冲电路

初级 FET 中有两个缓冲电路。齐纳缓冲器电路阻止开关节点处的电压过高,该电压由于关断时存在漏感能量而增加。为了保护 FET,齐纳二极管设置为 27V。图 3 显示,齐纳钳位将电压降至 32.03V,然后稳定在稳压电压(远低于 100V FET 额定值)。电压刻度为 5 V/p,时间刻度为 2 s/p。初级 FET 和其他有源器件具有串联 RC 缓冲器,以减少电压振铃。它们可以在很宽的频率范围内的所有情况下工作。例如,图 3 在 500 kHz 时几乎没有可见的振铃。

图3 .带齐纳缓冲器钳位的初级 FET 开关节点电压。图片由IEEE Open Journal of Power Electronics提供

隔离飞跨电容多电平转换器硬件设计要点

本文讨论了隔离飞跨电容多电平转换器的硬件设计。以下是一些要点。

该研究提供了有关硬件设计和组件选择的详细信息,包括缓冲电路和微调电容的使用。

原型设计旨在确保在指定的 40 V 输出上进行安全可靠的测试,同时考虑到各种操作。

本研究并未利用飞跨电容器结构实现的较低额定电压来实现更安全的测试,但未来几代人可以使用较低额定值的半导体来提高效率。

与传统转换器相比,隔离飞跨电容器多电平转换器具有提高效率和降低额定电压的潜力,使其成为电力

电子应用的有前途的替代品。

本研究开发的 N3 和 N4 转换器在次级分别包含 2 个和 3 个电容器级,展示了通过使用飞跨电容器结构提高效率的潜力。