为什么 SiC 功率芯片更小?

功率芯片的大小直接由单位面积的导通电阻决定,而导通电阻主要由作为功能层的外延层的电阻主导。为了化器件的导通电阻,必须增加外延层中的掺杂剂浓度(即降低电阻率)或减少层厚度,但这些也会导致击穿电压下降。这意味着芯片设计人员必须很好地权衡导通电阻和击穿电压。

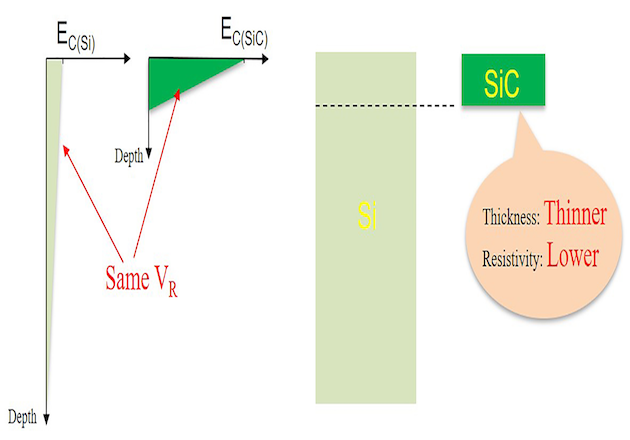

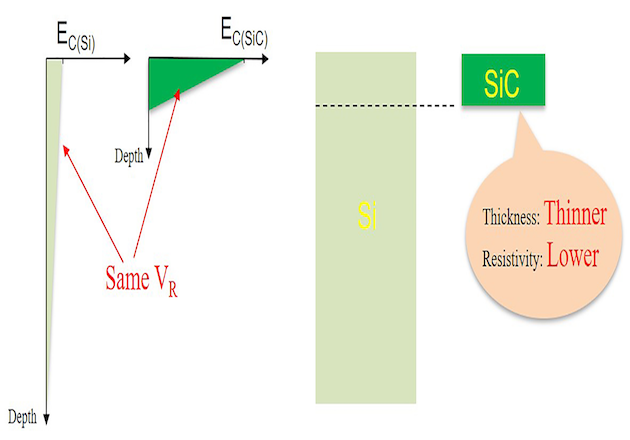

图 1:相同阻塞时 SiC 和 Si 器件的电场分布比较

根据泊松方程,器件击穿电压与击穿电场 (VB∝B 2) 的平方成正比。由于击穿电场比硅高近 10 倍,因此 SiC 器件表现出比硅器件更“友好”(即电阻更低)的外延层规格范围,以实现相同的击穿电压额定值。以 600V 肖特基二极管为例,厚度为 5um、掺杂浓度为 1016cm-3 的外延层对于 SiC 二极管来说已经足够了。但对于硅二极管,对外延层规格的要求要“更严格”(即更高的电阻),至少需要 50μm 的厚度和 1015cm-3 的掺杂浓度。毫无疑问,要避免外延层电阻的进一步增加,的办法就是扩大芯片尺寸。因此,由于具有强大的正向电流传导能力,SiC 功率器件可以设计成更小的芯片尺寸。

为什么 SiC 功率芯片在高温下性能更好?

Si 的本征载流子浓度约为 1010cm-3,而 SiC 仅具有 10-9cm-3,这两个值都是在室温下达到的。本征载流子浓度显着的特征是,当温度线性升高时,它会呈指数级增加。由此可见,当结温达到 200°C 时,硅的本征载流子浓度将超过 1014cm-3,该值与正常的 PN 结浓度相当,这往往会不可逆转地诱发工作中的硅器件失效。由于超低的本征载流子浓度,SiC 功率器件将安全地承受更高的温度,甚至超过 600°C。

这就是 SiC 器件能够承受高温的主要原因。然而,由于封装技术和应用的限制,常见的商用碳化硅产品在产品手册中只显示了 175°C 的结温。尽管如此,由于导热系数是硅的三倍,因此 SiC 功率器件仍然表现出更好的热性能。

为什么 SiC 二极管具有更好的开关性能?

我们在市场上谈到的大多数 SiC 二极管都是肖特基二极管。作为单极器件,肖特基二极管的反向恢复时间接近于零,这意味着硅肖特基二极管也能够实现类似的性能。但正如我们之前提到的,高压硅肖特基二极管也会表现出巨大的导通电阻,这将商用硅肖特基二极管的额定电压限制在 200V 以下。相比之下,对于 SiC,650V/1200V/1700V SiC 肖特基二极管已经投放市场很长时间了。

传统的高压硅二极管是一种 PiN 二极管,其中使用高电阻率和厚外延层来承受高反向电压。可以通过从 P 区域注入少数载流子(即电导率调制)来降低导通电阻,这是获得高压 Si 二极管的常见设计。但是这个 PiN 型二极管需要花费额外的时间来去除少数载流子,并在器件关闭时产生反向恢复电流。更糟糕的是,由于少数载流子的特性,当温度升高时,反向电流会更大。

鉴于肖特基结构的性质,SiC 二极管的反向恢复行为将与温度无关。总之,由于优异的物理性能,肖特基结构可用于高压 SiC 二极管设计,因此 SiC 二极管具有更好的开关性能。

图 2:Si PiN 二极管和 SiC 二极管在 125°C 时的反向恢复行为

在过去的几十年里,SiC 器件制造商一直在努力将其性能与硅器件进行比较,结果众所周知。然而,SiC 器件设计人员不能仅仅满足于 SiC 器件于 Si 器件,这实际上主要是由材料优势贡献的。即使配备相同的 SiC 材料,由于不同的工艺能力和芯片设计参与,不同的制造商也可能表现出不同的性能。设计人员应尽努力实现 SiC 器件,该器件不仅性能优于硅器件,而且在所有 SiC 厂商的器件中也是的。

设计

WeEn 拥有 50 多年的历史,在功率半导体器件设计方面拥有丰富的经验。设计过程包括:根据客户需求设定设计目标,使用 EDA 工具进行器件和工艺仿真,但基于代工厂产能、掩模和工艺设计、代工厂制造、组装、可靠性测试。经过多轮试验、优化、寿命测试、应用测试,终实现具有设计的合格产品。

过程模拟

由于强大的 Si-C 键合强度,在 SiC 中采用高注入能量形成 PN 结。由于大多数注入的杂质(例如 Al+)即使在注入后退火期间在 SiC 中的扩散也很少,因此必须设计注入能量和剂量以实现目标掺杂曲线,这通常通过几个步骤实现,因此在注入工艺设计中需要进行模拟。设计人员可以在仿真中使用 Monte Carlo 模型来设计注入配方以达到他们的目标。还需要使用二次离子质谱 (SIMS) 方法来测量植入后退火后的实际杂质分布。仿真结果和测量值之间的校正是芯片设计和制造中的一个重要步骤,尤其是在配方发生变化或引入新工艺设备时。

图 3:不同植入物能量的模拟杂质分布和 SIMS 杂质分布(图 Capture 自 Silvaco)

芯片架构设计

为了追求的器件性能,所有 WeEn SiC 肖特基二极管都设计了一种合并的 PN 肖特基 (MPS) 结构,其中 PN 结的内置电压将比传统的 JBS 结构在高正向电流下更早地被克服。然后,将少数电荷载流子注入漂移区域,导致导通电阻显着降低,从而使器件能够承受更高的浪涌电流。但是增加 PN 面积会导致肖特基面积减小,当双极模式未导通时,标称正向电流的导通电阻会增加。

因此,在正常的正向传导能力和浪涌电流处理之间需要权衡。凭借特殊的 P+ 岛布局设计和独特的欧姆触点工艺,WeEn SiC MPS 二极管设计了特殊的浪涌电流传导路径,表现出卓越的浪涌电流处理能力,而不会损失任何标称电流传导能力。

图 4:WeEn SiC MPS 二极管的横截面示意图和电流分布

图 5:650V MPS 二极管 WeEn NXPSC04650 4A 与其他公司的 JBS 二极管在 25°C 时的转发 I-V 特性比较

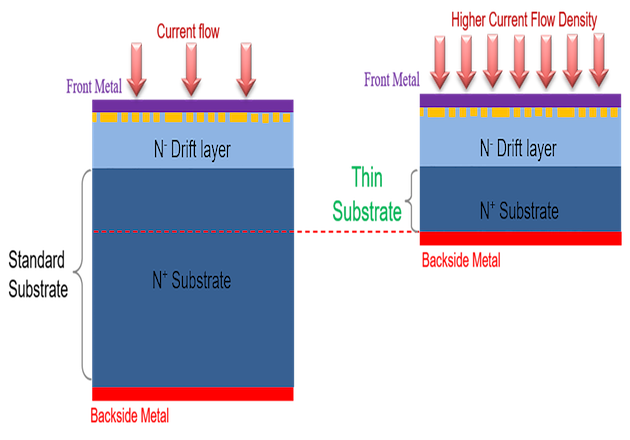

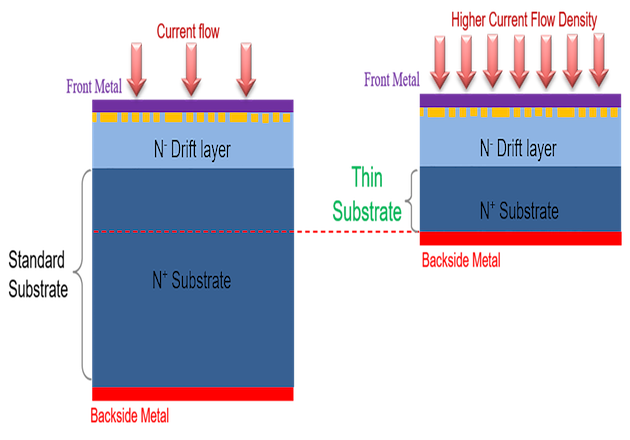

晶圆厚度设计

适合功率器件的 SiC 晶片由两层组成:厚衬底层和生长在其上的薄外延层。由于衬底层较厚,SiC 晶片,尤其是大尺寸晶片,表现出更好的机械稳定性,这在半导体工艺或运输中非常重要。但正如我们之前所说,由于整个阻断电压都由外延层承受,因此衬底层除了作为更像串联电阻的电流路径外,没有任何电气功能。

由于市售的 SiC 衬底不能具有高掺杂浓度,因此衬底电阻很明显,尤其是对于 650V SiC 器件,其外延层电阻低于高压器件。由此产生的功率耗散是不希望的,为了解决这个问题,考虑研磨衬底层。

但就 SiC 材料的硬度而言,制造商面临一些挑战,包括可能的裂纹、表面粗糙度和研磨后的厚度均匀性。由于的制造工艺和卓越的质量控制,瑞能SiC产品均采用薄晶圆设计,衬底厚度仅为市场上标准产品的1/3。得益于薄晶圆设计的优势,WeEn SiC 二极管具有更好的正向电流传导能力和更低的热阻。

图 6:WeEn 薄型 SiC 产品与其他公司标准产品的比较