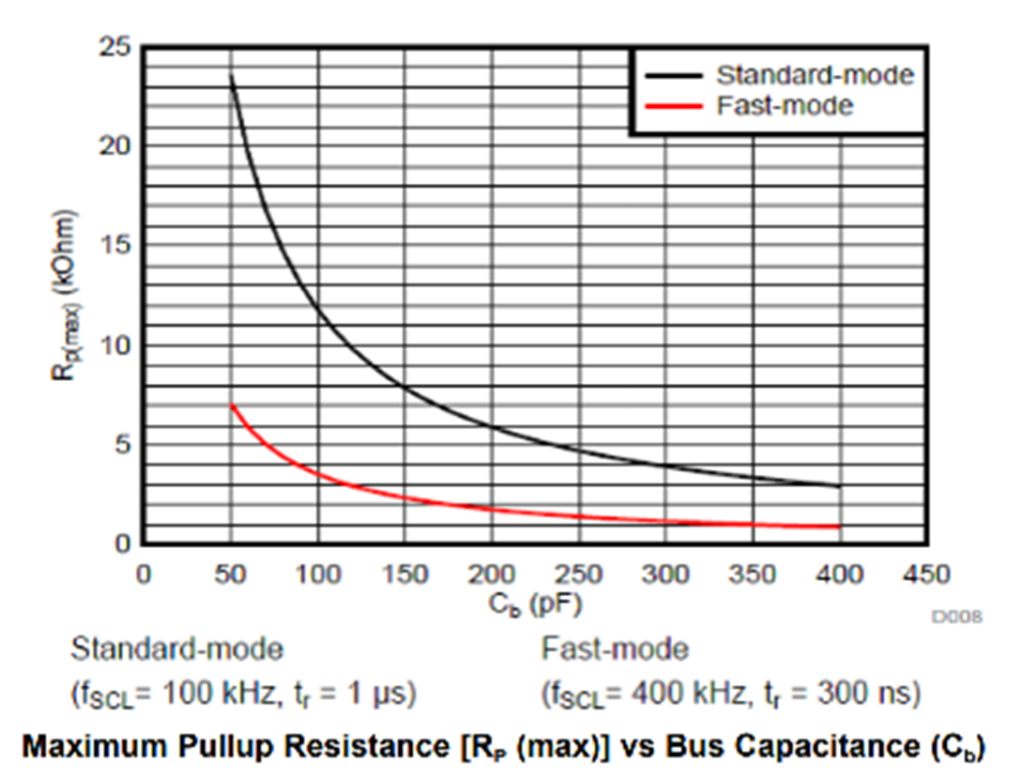

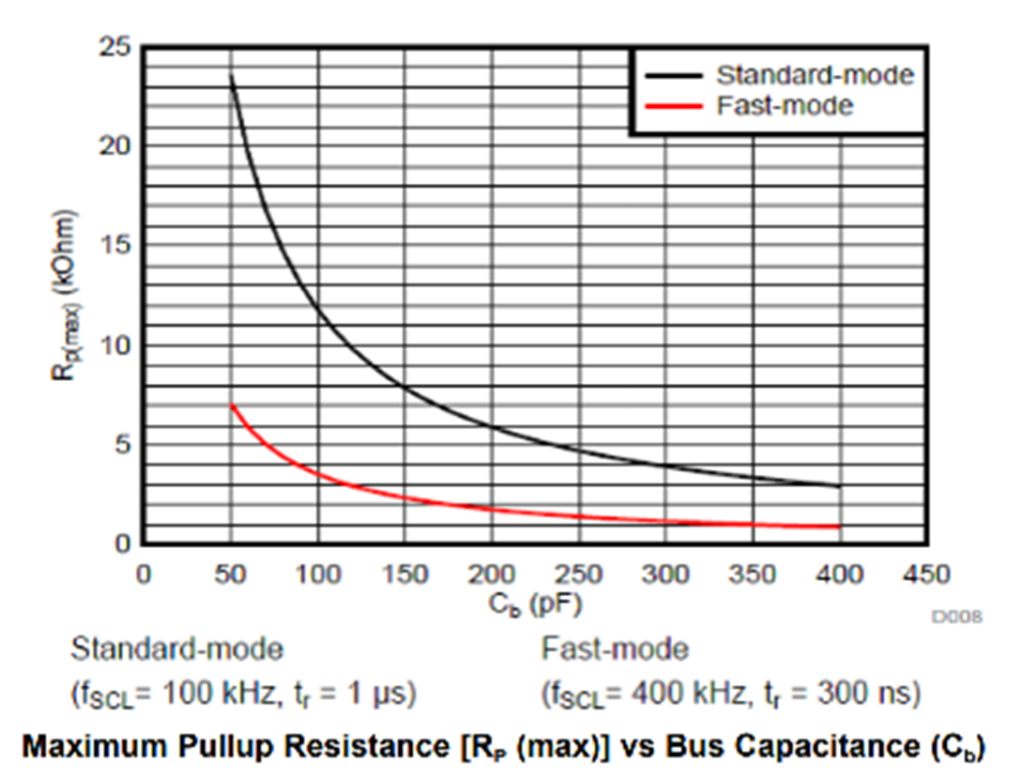

流行的 I 2 C 通信标准仅使用一条非常简单的两针总线(SCL 和 SDA)即可实现灵活的串行 I/O。它通过双向时序和数据流实现了这一技巧。双向流有利于节省引脚,但由于使用无源上拉电阻,因此不太适合节省功率。总线上拉电阻必须选择得足够低(从而通过足够的电流),以便以所选数据速率决定的速度对寄生总线电容进行充电。图 1说明了这种不方便的算法。

图 1 I 2 C 总线速度与有效上拉电阻成反比。德州

仪器应用 SLVA689

被动“上拉”过程中消耗的V/R电流量和V 2 /R功率取决于总线电容、上拉电压和占空比;如图 1 所示,对于快速模式 400 kHz、V = 5 V 和 Cb = 400 pF,消耗的电流量可能高达5V/1k = 5 mA和5 2 /1k = 25 mW。这很容易占到整个系统功耗的很大一部分。

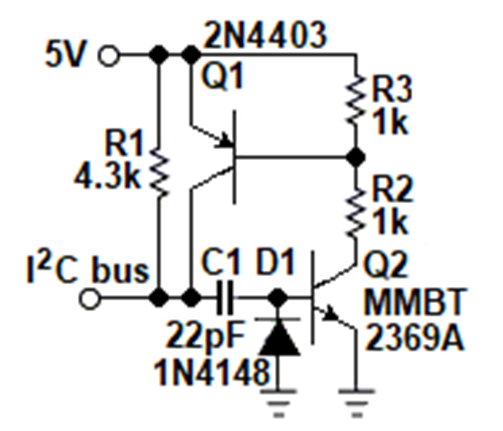

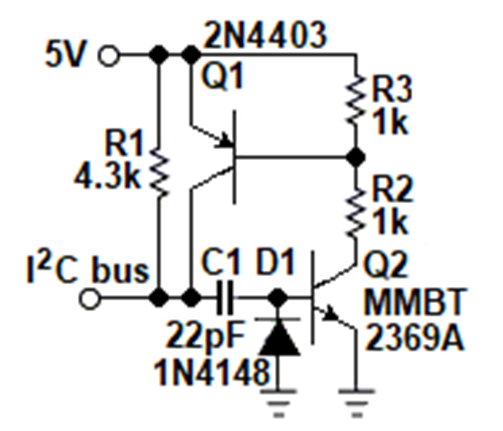

那么如何节省一些多余的电流和功率呢?图 2显示了一种方法:有源上拉,其值选择为图 1 中所示的坏情况组合,即高速 (400 kHz) 和高电容 (400 pF)。

图 2再生有源上拉电路(需要两个电路之一),其值是根据图 1 所示的坏情况组合选择的。

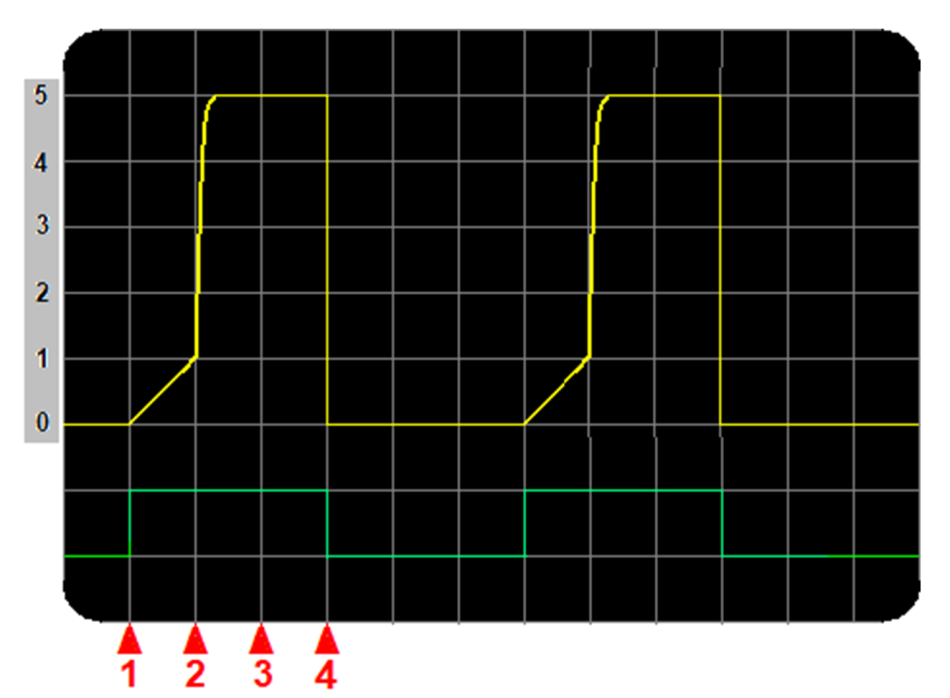

这种简单的电路拓扑结构,虽然宣称其目的是为了节省上拉功率,但其起点并不高:无源上拉电阻 R1。整个电路的工作原理如图3所示。

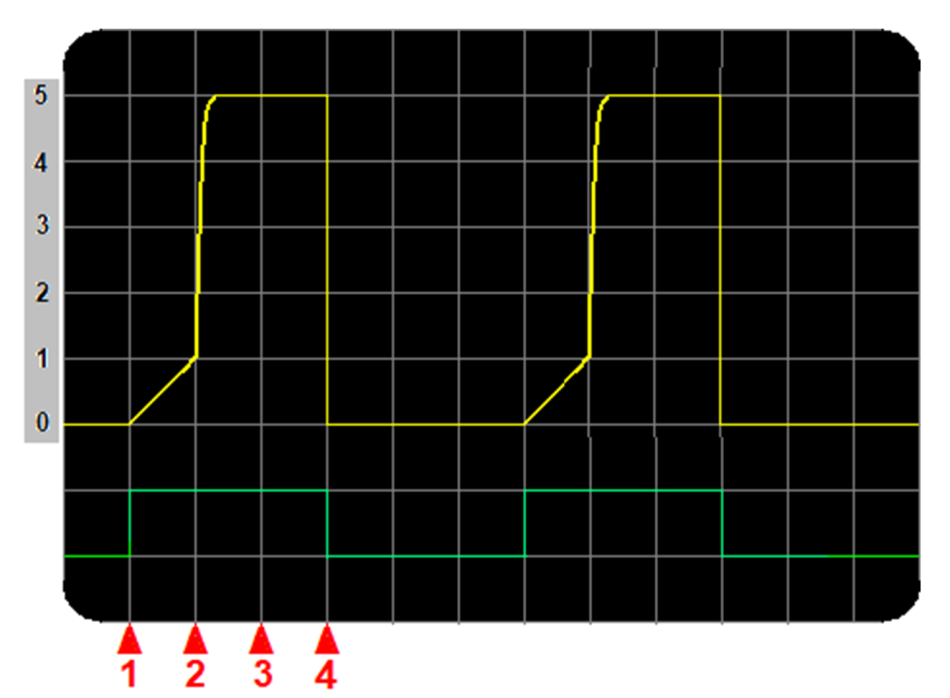

图 3图像内标记的有源上拉波形和 4 步序列。

有源上拉过程分为四个步骤。

释放相关总线

信号线(即 SCL 或 SDA)可使 R1 开始被动上拉并开始为总线电容充电。由此产生的电压上升很慢,因为 R1 比图 1 中按需要计算的 1k 大 4 倍多。显然,它永远无法足够快地完成上升时间!

但请稍等:产生的信号由 C1 耦合到 Q2 的基极。因此,在过程的第 2 步,Q2 导通,带动 Q1 导通,并启动一个非常快速的正反馈回路,该回路驱动两个

晶体管进入饱和状态,并在数十纳秒内完成总线电容充电;消除 R1 上的压降并结束其功耗。

22 pF C1 的时间常数非常短,它作用于 Q2 的基极阻抗,使 C1 放电并终止晶体管的驱动,从而使它们开始关闭并结束有源上拉。这为 Q1 和 Q2 提供了从饱和状态恢复的时间。

下拉开始总线活动的下一个周期并通过 D1 对 C1 重新充电,这也可以保护 Q2 有限的(仅 4.5 V)反向 Vbe 额定值。