功率转换器中使用的氮化镓 (GaN) 器件具有多种优势,包括更高的效率、功率密度和高频

开关。横向 GaN 高

电子迁移率

晶体管 (HEMT) 功率器件在此类应用中实现了强劲的市场增长。这种本质上为耗尽模式的器件的栅极驱动具有挑战性,有许多解决方案可以将其转变为稳健的增强模式操作。在本文中,我们总结了美国弗吉尼亚理工大学CPES的 Bixuan Wang 和一个包括来自英国剑桥 GaN 器件的员工在内的团队在 APEC 2024 会议上的演讲。在这项工作中,研究了具有集成栅极接口和保护功能的 p 栅极 GaN HEMT 的栅极过压稳定性。

p 栅极 GaN HEMT 面临的一些挑战

在创建增强型 GaN 技术的各种选项中,p 栅极 GaN HEMT 已成为一种流行的器件选择。在栅极金属下添加掺杂镁的 p 型层有助于将带隙以及器件的阈值电压 V th移至正范围。该器件的肖特基金属势垒版本 (SP-HEMT) 已被许多器件制造商和代工厂商业化,电压等级范围从 15 到 650 V。该器件的 V th通常低于 2V。这种低 Vth 会使器件更容易受到噪声的影响,尤其是这些器件能够进行的高频、高压摆率切换产生的瞬变。

器件的寄生开启是漏极-栅极米勒电容耦合的风险。这种风险通常需要使用负关断状态栅极电压 (V GS ) 驱动。另一个限制来自开启时使用更高电压栅极驱动所造成的可靠性问题。栅极

触点通常在 V GS > 7 V 时开始导通。陷阱相关效应会产生阈值电压变化,热载流子也会导致动态导通电阻 (RDSon) 增加。这为导通状态 V GS创造了一个上限窗口,通常在 6.5 V 左右。

导通状态 Vgs 的下限窗口可由 RDSon 设置,通常需要 > 4V 左右才能达到饱和低电平。因此,整体操作窗口可能很小(4V – 6.5V)。因此,栅极过驱动的裕度非常有限(大约 1 V)。基于驱动 Si MOSFET 的标准栅极驱动器无法轻松使用,需要多个外部组件,因此会增加转换器电路板的复杂性和成本。电路板设计和布局对于保持电感路径较小至关重要,而使用噪声裕度低且需要许多外部组件与栅极驱动器接口的 GaN 器件会增加这种复杂性 集成式 GaN 解决方案

Cambridge GaN Devices 是一家无晶圆厂半导体公司,开发了一系列额定电压为 650 V 的硅基 GaN 功率器件。一种称为 ICeGaN 的新型栅极接口以及感测和保护电路被单片集成到单个芯片解决方案中。图 1 显示了 ICeGaN 电路的示意框图。主功率 HEMT 是肖特基 p 栅极 GaN HEMT,额定电压为 650V,V th约为 1.6V。

辅助低压 GaN HEMT 与电流源和电压限制器一起负责吸收大部分外部施加的栅极电压。因此,功率 HEMT 器件栅极上的电压(在图 1 中称为内栅极或 V Gi)受到严格控制。该电路确保功率 HEMT 不会在外部栅极电压 V G达到约 2.7 V(这是集成器件 V th)之前开启,此时 V Gi约为 1.6 V。对于高于此值的电压,当 V G < 7 V 时,V Gi遵循辅助 HEMT 栅极电压 V G,aux ,公式为 V Gi = V G,aux – V GS,aux。当 V G > 7V 时,V G, aux被钳位在一个恒定电压上,因此 V Gi被限制在 5.5 V 左右。

图 1:ICeGaN 电路原理框图(Cambridge GaN Devices)

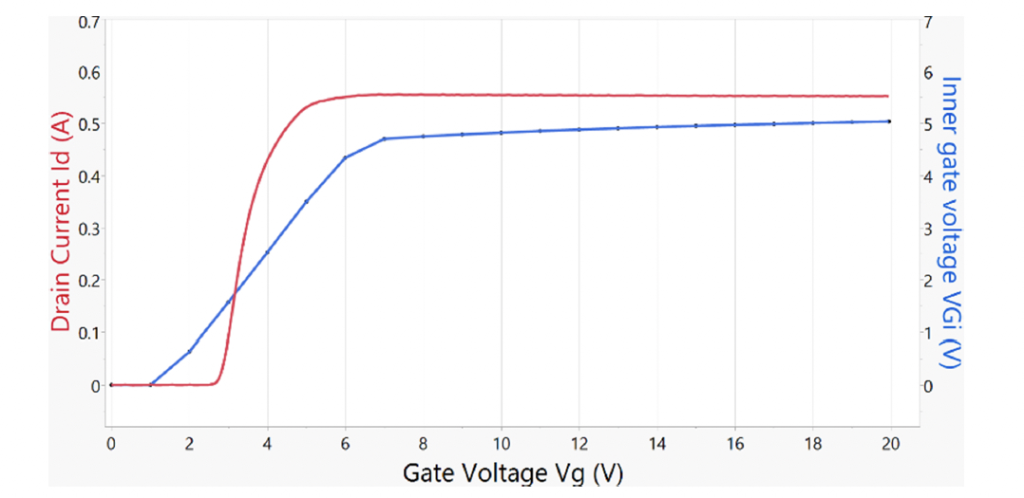

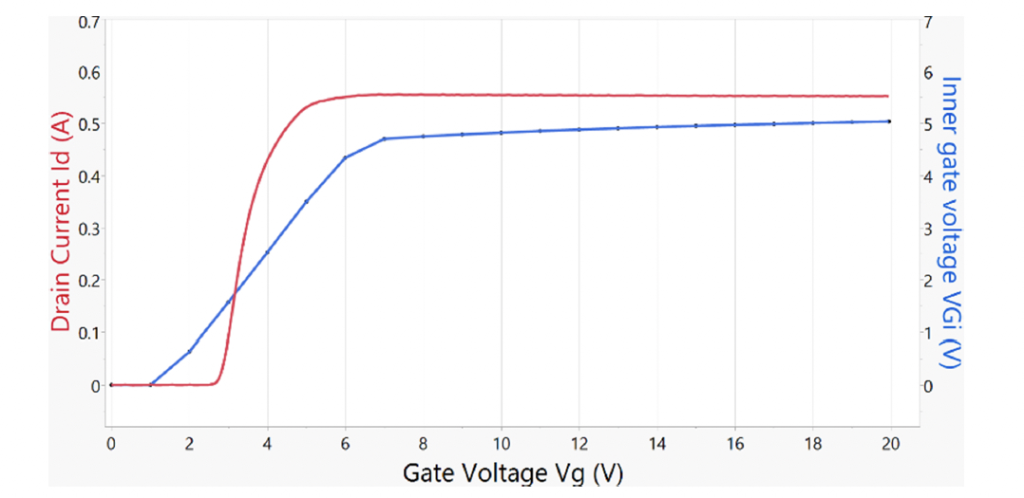

图 2 显示了 V G和 V Gi之间的关系。因此,标准栅极驱动器可用于外部 V G 。ICeGaN 接口的另一个优点是,相对于高温,钳位电路在低温下高 V G值时会降低 V Gi ,从而限度地减少了 GaN HEMT 1中出现的退化机制之一。

米勒箝位是动态操作下的重要保护装置。该装置具有可调状态,因此当功率 GaN 开启时,它在正常条件下处于高阻抗关闭状态。在关闭时,它能够将 V Gi强力拉至 0 V,加速关闭并限度地减少栅极电荷。米勒箝位还可在外部瞬变和快速开关事件期间提供强大的抗寄生开启能力。

图 2: ICeGaN 电路中V G和 V Gi的关系( 1)

栅极过压稳定性

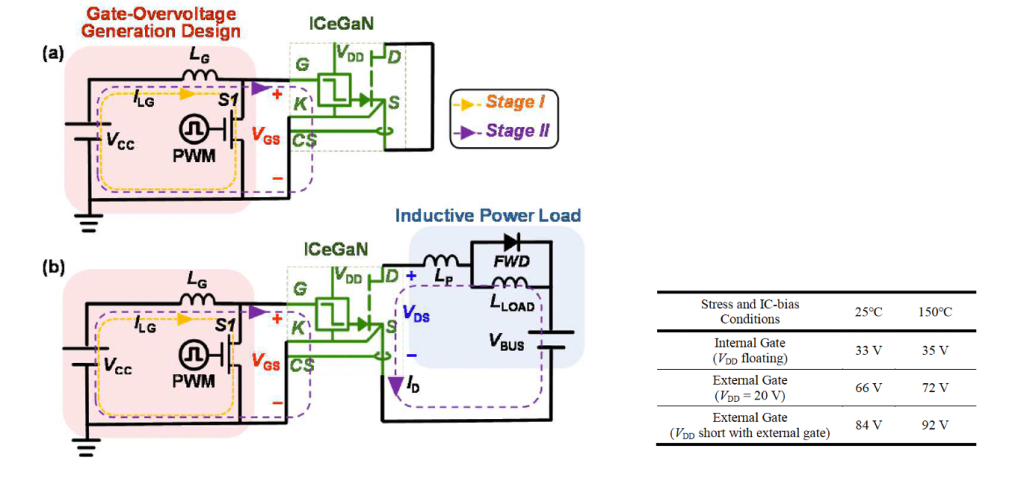

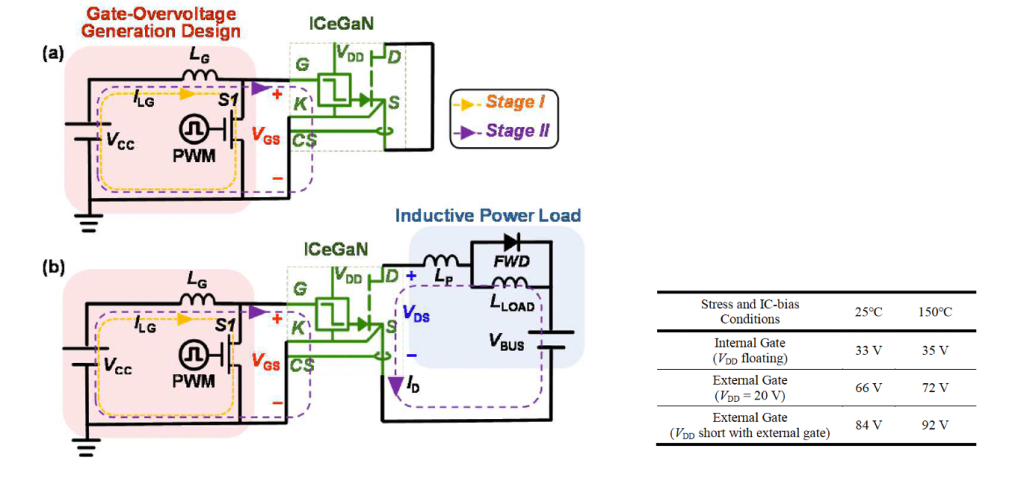

在王教授及其团队进行的这项研究中,研究了 ICeGaN 的动态栅极过压边界。使用 650V/130 mΩ ICeGaN 产品。智能接口由外部 12 – 20 VV DD电压供电,如图 1 所示。在 V G或 V Gi处产生谐振电压过冲,模拟功率转换器中可见的栅极过冲。测试在静态条件下进行,其中功率 GaN 漏极-源极接地(称为 DSG,V DS = 0V),模拟零电压开关情况,以及在 400 V 总线电压和电感负载下的硬开关 (HSW) 条件。测试平台原理图如图 3 所示。

图 3:用于栅极过压稳定性的测试平台及总结结果(Wang 等,APEC 2024)

该测试电路通过在栅极环路电感器 L G中积聚能量来产生过冲,该电感器由 0.5 VV CC电源电压充电。开关 S1 是低压 GaN HEMT。当 S1 关闭时,L G中的能量会产生谐振过冲,谐振由 L G以及 ICeGaN 的输入电容与 S1 的输出电容之和产生。过冲的脉冲宽度可由 L G值调制,过冲可由 S1 的导通时间调制。本工作中使用的宽度为 20 ns。这些器件在 25 o C 和 150 o C 下进行了测试。使用的另一个变量是 ICeGaN 芯片的 V DD电源。在一种情况下,它被设置为 20 V,而在另一种情况下,它与外部栅极电源相连。后一种情况可消除 ESD 保护电路中的过压应力。

动态栅极过压稳定性通过参数 BV G, DYN来衡量,该参数表示部件发生故障前的栅极过应力电压。获得的结果如图 3 中的表格所示。当过压直接施加到内部栅极时,可获得 33-35 V 的 BV G, DYN值,而当应力施加到 ICeGaN 的外部栅极引脚且 V DD为 20 V 时,该值会增加到 66 -72 V。当 V DD引脚短路至外部栅极时,BV G, DYN会进一步增加到 84 -92 V。在 VDD 由外部 20 V 电源驱动的情况下进行的故障分析表明,ICeGaN 芯片中的 ESD 保护模块可能是故障模块。故障时的参数特性显示栅极-源极短路。在 VDD 短路至外部栅极的情况下发生的故障在故障后显示出传输特性的变化。此处的故障归因于米勒钳位的退化,导致软故障。

BV G, DYN中显示的显著提升表明 ICeGaN 栅极接口提供了出色的栅极保护。通过集成解决方案提高栅极稳健性对于在

电源转换器应用中使用 ICeGaN 器件而言是一项重要优势。