从快速充电器和旅行

适配器到

扬声器和智能家居助理的电源,各种应用都依赖于低功耗(低于 100 W)AC/DC 转换。选择电源转换架构时的一个基本点是其提供零电压开关 (ZVS) 的程度,因为这对效率、EMI 性能和可靠性具有重大影响。并非所有传统拓扑都能够实现 ZVS,而且目前还没有一种拓扑能够在轻负载下提供 ZVS。

任何插入墙壁插座的

电子设备都需要某种形式的交流/直流转换器来整流电压并将其降低到设备所需的较低水平。我们在家庭和办公室发现的许多现代设备都属于低功耗类别,需要的功率低于 100 W。事实上,除了电器之外,我们家中的大多数设备都可能被归类为低功耗设备。

在某些情况下,例如计算机显示器或电池充电器,AC/DC 转换器将嵌入在产品本身中。然而,许多设备使用专用的外部电源——包括智能家居助手和磁盘驱动器等计算机外围设备,所有这些设备在使用时都需要电源。此外,AC/DC 转换是用于为手机、平板电脑和其他便携式设备充电的适配器的基础。

虽然这些应用的低功耗特性可能意味着效率并不是一个大问题,但事实却并非如此。鉴于这些设备有数十亿台正在使用,并且通常每周 7 天、24 小时都处于接通状态,因此对能源消耗和后续排放的影响是巨大的。因此,提高交流/直流转换器的效率是电力工程师设计议程的首要任务。

低功耗 AC/DC 转换的拓扑和技术

额定功率低于 75 W 的低功率 AC/DC 转换器通常不受功率因数校正 (PFC) 要求的影响,因为它们对主电网的影响被认为是的。这简化了设计并减少了元件数量——这两者都是这些微型电源解决方案的理想选择。

反激式拓扑由于其多功能性、性能和简单性而在低功耗设计中极为流行。这种拓扑已经使用了 70 多年,通常由初级侧 MOSFET、输出(次级)整流

二极管、输出电容器和反激变压器以及其他一些小型组件组成。

电源设计人员不断寻求改进拓扑,以提高效率或性能,或者理想情况下两者兼而有之。因此,准谐振 (QR) 反激架构由于能够降低开关损耗而变得非常流行。这是通过在导通脉冲之前降低初级 MOSFET 的漏极-源极电压来实现的,这具有降低峰值电流和开关频率的效果,确保 MOSFET 在个“波谷”导通。

QR 操作的效率增益主要在满负载条件下实现。然而,这种拓扑的硬开关特性意味着在轻负载时,效率通常要低得多。

通过零电压开关 (ZVS) 的实施可以进一步改进 QR 反激式设计。在正常的 QR 反激式设计中,MOSFET 在“谷”中切换,这意味着漏源电压 (VDS) 处于值,但不一定为零。通过实施 ZVS(或软开关),VDS 在 MOSFET 切换之前降至零(而不仅仅是值),从而消除了电压和电流之间的任何重叠,从而限度地减少损耗。这还可以降低 EMI,这是一个额外的好处,可以让设计人员更轻松地满足严格的 EMC 法规。

进一步的发展是有源钳位反激式 (ACF) 拓扑,它与传统反激式设计的不同之处在于,它重新利用了变压器漏感中存储的能量,而这些能量本来会在无源钳位缓冲电阻中耗散。向负载提供这种“回收”能量可提高转换器效率,并显着降低关断期间 MOSFET 上的峰值电压。

此外,ACF 设计中的 QR“谷”明显较低,通常可实现近 ZVS 操作,从而降低开关损耗并增强 EMI。

改进和扩展 ZVS 性能

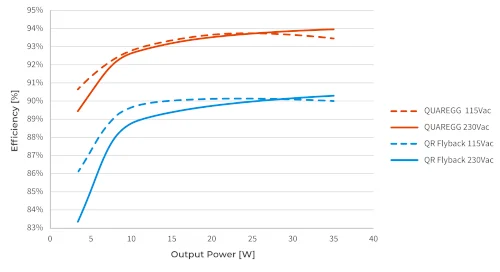

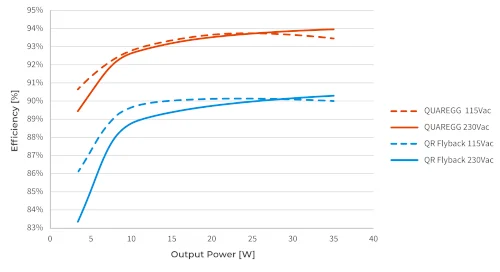

QuarEgg? 是一种新的反激式转换方法,能够进一步提高性能、效率和可靠性,这是一种由 Eggtronic 开发的创新型专有电源架构,专门用于低于 100 W 的交流/直流设计。这种新架构显着提高了效率并减小了通常基于 ACF 和 QR 反激拓扑的 AC/DC 转换器的尺寸。与其他方法不同,该架构在所有负载条件下均采用 ZVS 运行,从而提供非常平坦的效率曲线。满负载时的典型效率高达 95%,轻负载时的效率高达 92%,并且在待机模式下,基于 QuarEgg 的设计功耗低于 18 mW。

图 1.QuarEgg 显示在整个负载范围内效率比通用 QR 反激转换器显着提高。图片由 Bodo's Power Systems提供

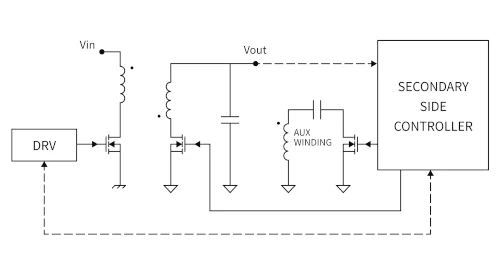

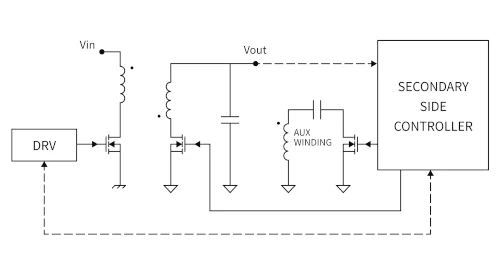

图 2.QuarEgg 拓扑的简化示意图。图片由 Bodo's Power Systems提供

与通用 QR 反激拓扑相比,新方法在主变压器上添加了一个辅助绕组,以及一个飞跨电容器和一个以正向配置连接在低侧的低压、低成本 MOSFET。然而,取消高压、高侧钳位 MOSFET 可以减少总体元件数量并提高可靠性。主QuarEgg控制器位于转换器的次级侧,以增强对输出电压的调节。

辅助 MOSFET 主要是作为在所有负载条件下主动强制主功率 MOSFET 达到 ZVS 条件的一种手段。当转换器进行开关时,次级侧控制器通过辅助绕组感测初级 MOSFET 的 VDS。当每个波峰出现时,辅助 MOSFET 导通并对漏极节点放电,使 VDS 变为零,从而确保主 MOSFET 的 ZVS 导通。

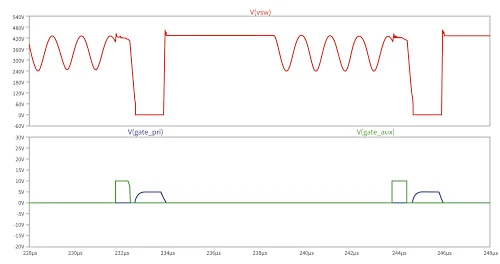

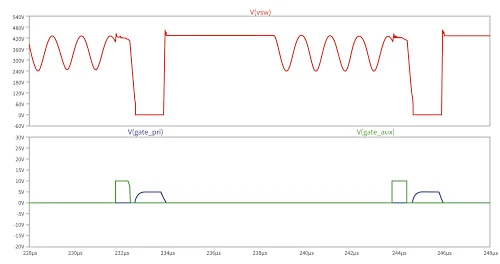

相应的波形如下所示。

新方法适用于所有类型的 MOSFET 开关器件,包括传统硅和宽带隙 (WBG) 材料,例如氮化镓 (GaN) 和碳化硅 (SiC)。与传统的 ACF 和 QR 拓扑相比,基于 QuarEgg 的电源转换器的性能得到了改进,与传统硅转换器相比,效率提高了 7 倍,尺寸缩小了 3 倍,而与高性能 GaN 转换器相比,效率提高了 3 倍,尺寸缩小了 2 倍。

为了支持设计人员使用 Eggtronic 技术,我们提供了一系列开发板、集成电源控制器和专有磁性元件以及详细的技术支持。

图 3.QuarEgg 拓扑的波形。红色:初级MOSFET的VDS;绿色:辅助MOSFET的Vg;蓝色:初级 MOSFET 的 Vg。图片由 Bodo's Power Systems提供

概括

对于低功率 AC/DC 电源、充电器和适配器来说,从空载到满载的效率越来越重要,因为这些电源、充电器和适配器可能每周 7 天、每天 24 小时都处于接通状态。到目前为止,许多设计都是基于已经使用了几十年的反激拓扑,尽管近有了 QR、ACF 和 ZVS 等增强功能。

作为 Eggtronic EcoVoltas? 系列的一员,QuarEgg 专为提供更小、更高效率的电源转换而开发,并帮助工程师实现性能、成本、尺寸、重量和可持续性目标。

通过主动强制 ZVS 运行,新架构不仅提高了效率,而且使效率曲线变得平坦,以解决轻负载时性能不佳的问题。该技术还可以减少组件,进一步提高功率密度和可靠性。