由于多种原因,与受控对象 (OUC) 的链接可能会无意中变得不可靠:接触不良、短路、温度应力或组件上的蒸汽冷凝物。有时,只需探索

芯片本身提供的可能性,就可以与流行的桥接芯片建立更好的链接。

用您独特的设计让工程界惊叹: 设计理念提交指南

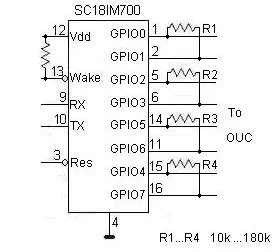

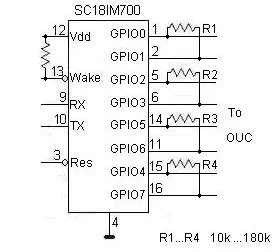

桥接器,例如

NXP的SC18IM700,通常会提供一定数量的GPIO,可以方便地实现测试。这些 GPIO 保留其所有功能,并且在测试后可以照常使用。

为了使测试成为可能,芯片必须具有多个 GPIO。这样,他们就可以配对,为配对的成员提供互相投票的机会。

由于测试期间 GPIO 的活动可能会损害 OUC 的正常功能,因此可以选择其中一个 GPIO 引脚暂时禁止这些功能。很多时候,当这个物体具有相当大的惯性时,这个禁止可以被忽略。

图 1显示了如何在 SC18IM700 UART-I2C 桥的情况下实现这一想法。

图 1:使用 SC18IM70pytho0 UART-I2C 桥进行自测试 GPIO。

电阻器 R1…R4 的值必须足够大,以免产生不可接受的大电流;另一方面,它们应该为输入上的逻辑“1”提供足够的电压。图 1 中显示的值适用于大多数应用,但可能需要调整。

仅在准双向输出配置中可能会出现一些困难,因为在该配置中,当端口输出逻辑高电平时,它的驱动较弱。当相应的 OUC 输入电阻太低时,可能会出现此问题。

如果在测试过程中UART输出的数据速率对于对OUC相关

电容的适当充电来说太高,则可以降低该数据速率,或者可以减小相应的电阻值。