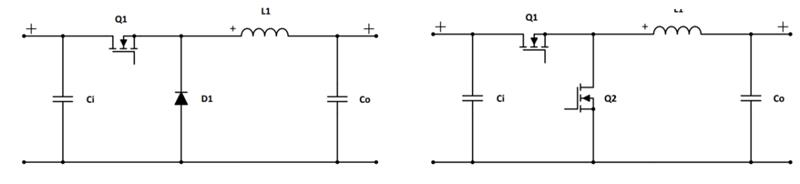

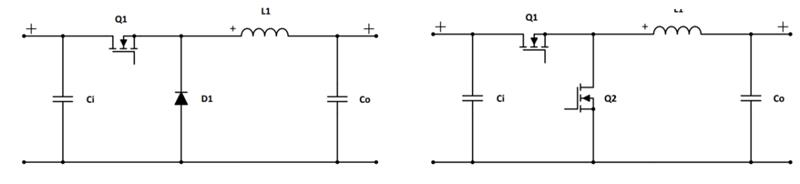

下图分别是(左)异步BUCK与 (右)同步BUCK电路示意图。

DPDK(Data Plane Development Kit)是一种用于高性能数据包处理的开源软件开发工具集。它通过绕过操作系统内核,直接在用户空间进行数据包处理,以提供低延迟和高吞吐量的网络数据处理能力。下面是DPDK技术的一般原理:

用户态驱动:

DPDK在用户态运行,不依赖于操作系统内核进行数据包处理。相比于传统的内核态驱动,用户态驱动能够减少系统调用和上下文切换的开销,从而提高数据包处理的效率。

零拷贝操作:

DPDK采用了零拷贝(Zero-Copy)技术,避免了在数据包传输过程中的多次内存拷贝。通过使用共享内存或直接内存访问(Direct Memory Access,DMA),数据包可以直接在内存中进行处理,减少了数据包处理过程中的数据拷贝和内存访问的开销。

事件驱动模型:

DPDK使用事件驱动的模型来处理网络数据包。它通过轮询或异步事件回调等方式,实时监听和处理数据包到达的事件。这种模型可以降低处理延迟,并充分利用多核处理器的并行能力。

锁与同步机制:

由于DPDK在用户态运行,处理多个线程同时访问共享数据时可能会引发竞争条件。为了确保数据的一致性和正确性,DPDK提供了各种锁和同步机制,如自旋锁、互斥锁和原子操作等。

硬件加速:

DPDK充分利用现代网络接口卡(NIC)中的硬件功能来加速数据包处理。它支持网卡的多队列和RSS(Receive Side Scaling)等技术,可以在多个上并行处理数据包,提高处理能力。

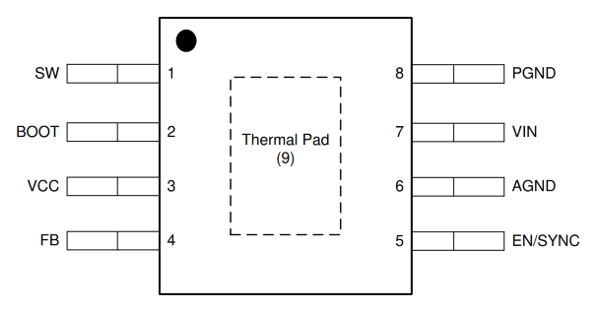

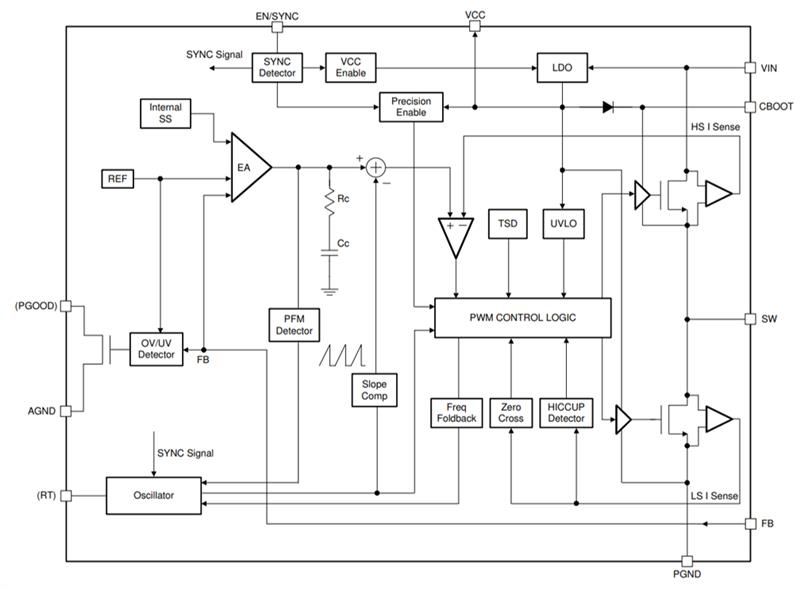

接下来我们以TI的一个36V/3A的同步BUCK -LMR23630 为例 一步步带大家了解BUCK的设计过程。

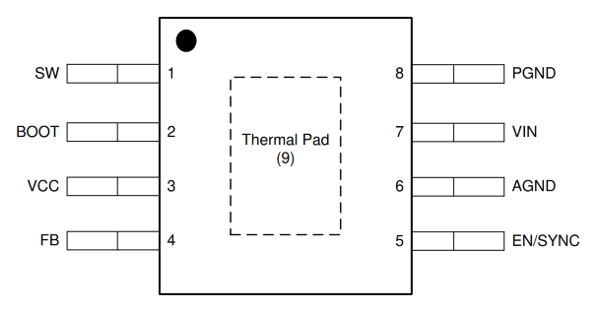

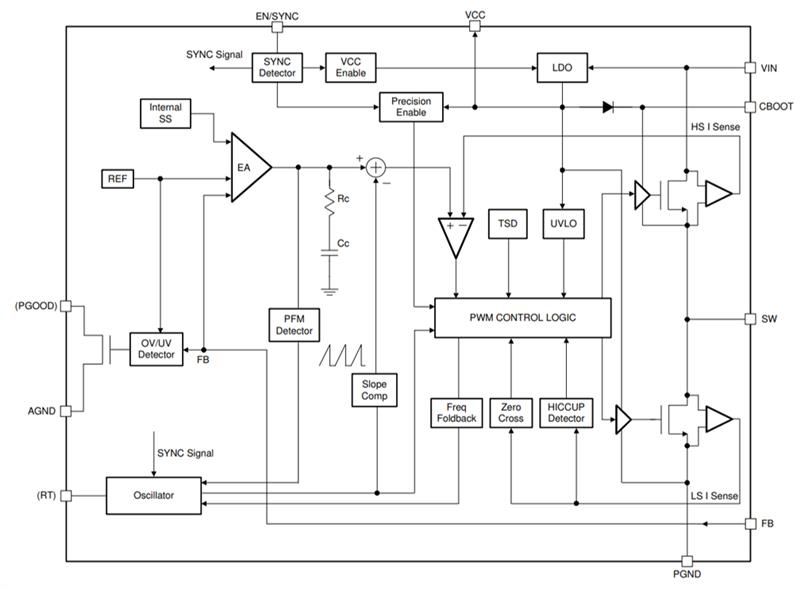

Step 1---简单看看BUCK数据手册:了解LMR23630芯片基本功能。

我们看SOIC-8封装左侧的四个引脚: SW、 BOOT、 VCC、 FB:

Pin1 SW:上管和下管的中点,SW接输出

滤波电感后接输出电容。 一般排查BUCK工作是否OK需要看SW波形是否正常switching。

Pin2 BOOT:用来给上管关断时,DS两端提供稳定电压。 当下管断开,SW浮地,驱动打开上管需要上管的driver供电与上管DS通过CBOOT(自举电容)建立VCC的电压。 别迷糊,从block可以看到,VIN通过芯片内部LDO给上下管的driver供电,同时钳位上管DS电压,也即是说当上管的DS电压稳定后,给上管栅极一个驱动电压Vgs大于零后,上管才能打开。

Pin3 VCC:就是给内部逻辑和driver供电的LDO输出的引脚,需要加电容对地。

Pin4 FB:反馈脚,通过上篇BUCK控制模式中的PCM控制阅读后,(BUCK控制 加连接)我们知道FB是误差

放大器的输入,把输出电压反馈给EA做闭环控制,因此一般BUCK在正常工作的时候,FB电压等于内部基准电压,输出电压也通过FB电压进行分压计算。

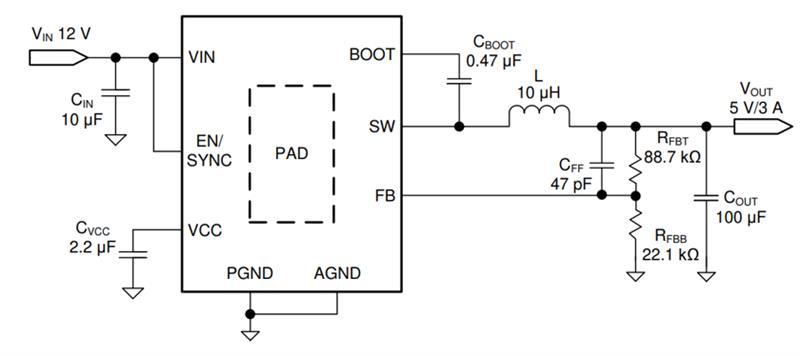

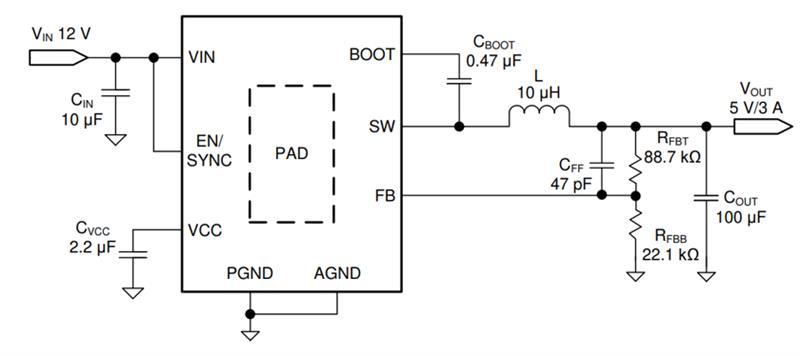

Step 2---根据典型推荐电路设计外围参数

1.输入电容CIN:

a.输入电容决定输入电压纹波ΔVin。

CIN=Iout/(4ΔVinfsw),ΔVin一般取10%Vin

b.由输入电流有效值公式:Icin_rms=Iout[D(1-D)]^0.5 可知,D=0.5时,输入电容电流的纹波:Icin_rms(max)=0.5Iout

因此对于CIN 选择RMS额定电流值大于0.5Iout即可。

实际探讨:对于建议输入电容值较大(22uF/47uF)的应用,建议采用多个输入

陶瓷电容并联会让输入电容整体ESR更小,从而减小热损耗。