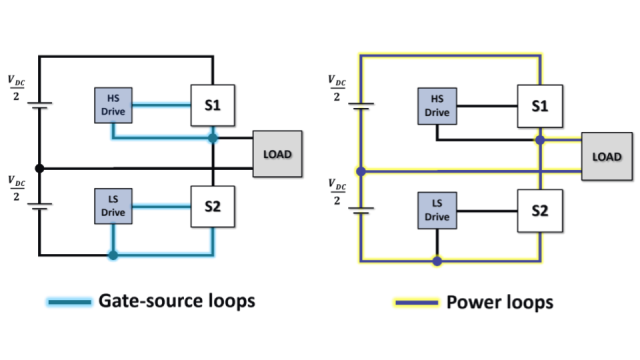

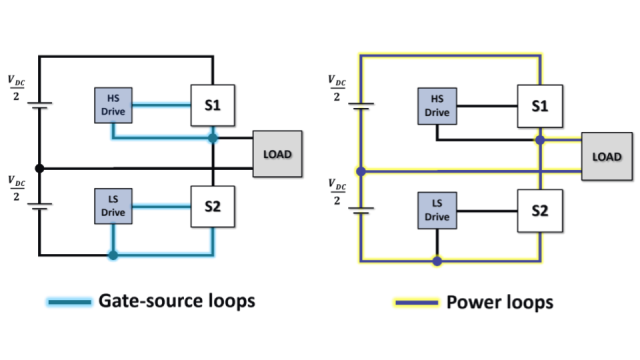

电力系统是一个由电气元件组成的复杂网络,用于向各种负载产生、传输和分配电力。栅源环路和电源环路是构成电源系统的两个主要环路。为

开关器件(例如 IGBT 或碳化硅 MOSFET)供电的控制电路称为栅源环路。栅极

驱动器、栅极电阻、栅极电容和栅极

电感构成栅源环路,器件的性能和开关速度由栅源环路设置。

传输负载电压和电流的初级电路是功率环路。该环路由电源、开关器件、负载和封装电感、PCB走线电感和杂散电感等寄生元件组成。因此,电力系统的可靠性和效率受到电力环路的影响。

电力系统中的回路相互联系并相互影响。电源环路和栅源环路都会影响器件的开关方式,在电源系统环路中,寄生电感可能会导致多种问题,包括开关损耗、意外导通、电压过冲和开关过程中的振荡。为了降低寄生电感并充分利用SiC器件,改进电源系统环路的设计和架构至关重要。

电源系统电路中的栅源环路和电源环路(Microchip Technology)

感应效应的来源和后果

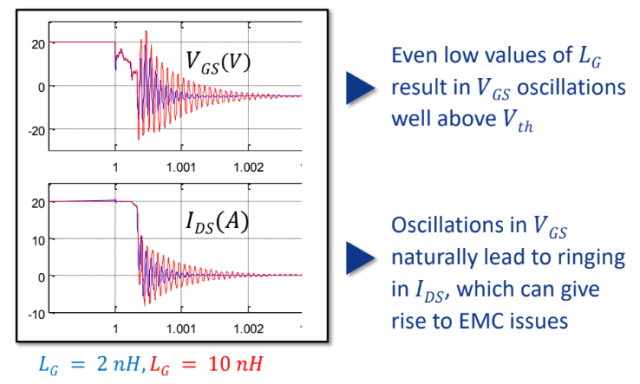

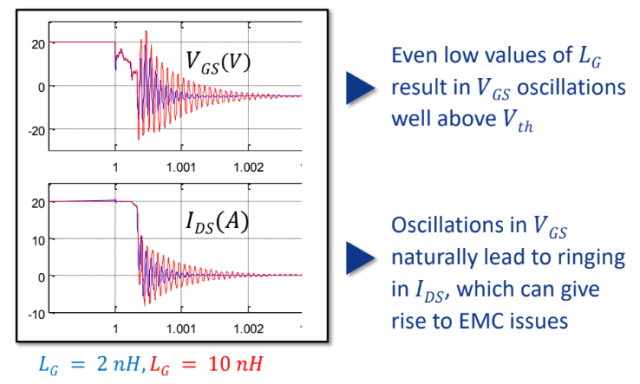

在电源系统环路中,电感效应是由元件和布局的寄生电感引起的。寄生电感是任何物理导体中固有的不需要的电感。它们由导体的几何形状、长度和接近程度决定。寄生电感会对电源系统的性能和可靠性产生负面影响。感应效应的一些常见后果是:

电压过冲:当开关器件关断时,由于寄生电感的影响,功率环路中的电流不能瞬时改变。寄生电感会导致器件上出现电压尖峰,该电压尖峰可能会超过其击穿电压并损坏器件。

开关振荡:寄生电感和器件电容形成谐振电路,会在开关节点引起振铃。振铃会增加开关损耗、电磁干扰和噪声敏感性。

无意开启:电压尖峰和振铃可通过米勒电容耦合至栅源环路,并导致器件误开启。这可能导致短路和直通电流。

开关损耗:寄生电感会减慢开关速度并增加开关时间。当电压和电流都很高时,这会延长过渡期,从而导致更高的开关损耗。

断电期间电压过冲问题。

断电期间的电压过冲问题(Microchip Technology)

因此,有必要降低电力系统回路中的寄生电感,以避免这些问题,提高电力系统的效率和可靠性。

利用 Microchip SP6LI 封装的 SiC 功能

与传统硅器件相比,SiC 器件具有许多优势,例如更高的击穿电压、更低的导通电阻、更快的开关速度和更高的工作温度。然而,要充分发挥SiC器件的潜力,需要有合适的封装来满足电源系统的大电流、高频和高效率要求。

Microchip 的 SP6LI 封装是一种新颖的解决方案,旨在降低寄生电感并释放 SiC 器件的性能。SP6LI 封装是一个相脚模块,由半桥配置中的两个 SiC MOSFET 和两个 SiC肖特基

二极管组成。SP6LI 封装具有 2.9 nH 的极低杂散电感,这是通过使用对称布局、直接键合铜基板和低环路面积实现的。

SP6LI 封装为电源系统提供了多项优势,例如:

更低的电压过冲:SP6LI 封装的低电感可降低关断期间器件上的电压尖峰,从而保护器件免受过压应力并提高可靠性。

更快的开关速度:SP6LI封装的低电感可实现更快的开关转换和更高的开关频率,从而降低开关损耗并提高功率密度。

更高的效率:SP6LI封装的低电感限度地减少了开关损耗和传导损耗,从而提高了电源系统的效率和热性能。

更高的功率密度:SP6LI封装具有紧凑的外形尺寸和高额定电流,允许并联较少数量的模块来实现完整的系统,这有助于设计人员进一步缩小设备尺寸。

降低电感并说明长期节能

为了证明 SP6LI 封装的电感降低,Microchip 在相同条件下与传统 D3 封装进行了比较测试。测试结果表明,SP6LI封装在开关节点处的电压过冲和振铃明显低于D3封装,表明寄生电感更低。与D3封装相比,SP6LI封装还具有更短的开关时间和更低的开关损耗,从而实现更高的开关频率和更高的效率。