由于G和G在电路中的作用完全相同,所以习惯上将电路画成图5.2.1(b)所示的对称形式。Q 和Q′称为输出端,并且定义Q=1,Q′=0为锁存器的1状态,、Q=0、Q′=1为锁存器的0状态。S称为置位端或置1输入端,R称为复位端或置0输入端。

当、SD=1、Rv=0时,。Q=1,Q′=0。在S=1信号消失以后(即S回到0),由于有 Q端的高电平接回到(G的另一个输入端,因而电路的1状态得以保持。

当、S=0、R=1时,、。Q=0、Q′=1。在R=1信号消失以后,电路保持0状态不变。当S=R=0时,电路维持原来的状态不变。

当S=R=1时,Q=Q′=0,这既不是定义的1状态,也不是定义的0状态。

而且,在S和R同时回到0以后无法断定锁存器将回到1 状态还是0 状态。因此,在正常工作时输入信号应遵守SR=0的约束条件,亦即不允许输入S=R=1的信号。

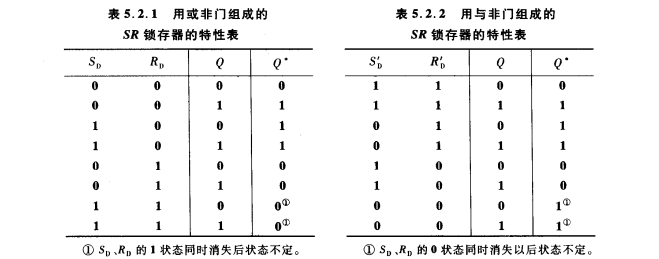

将上述逻辑关系列成真值表,就得到表5.2.1。因为锁存器新的状态(Q(也称为次态)不仅与输入状态有关,而且与锁存器原来的状态Q(也称为初态)有关,所以将Q 也作为一个变量列入了真值表,并将Q 称为状态变量,将这种含有状态变量的真值表称为锁存器的特性表(或功能表)。

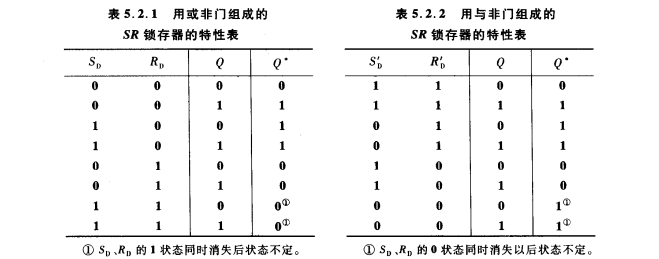

SR锁存器也可以用与非门构成,如图5.2.2所示。这个电路是以低电平作为输入信号的,所以用。SD′和R′分别表示置1 输入端和置0 输入端。在图5.2.2(b)所示的图形符号上,用输入端的小圆圈表示用低电平作输入信号,或者称低电平有效。表5.2.2是它的特性表。

由于G和G在电路中的作用完全相同,所以习惯上将电路画成图5.2.1(b)所示的对称形式。Q 和Q′称为输出端,并且定义Q=1,Q′=0为锁存器的1状态,、Q=0、Q′=1为锁存器的0状态。S称为置位端或置1输入端,R称为复位端或置0输入端。

当、SD=1、Rv=0时,。Q=1,Q′=0。在S=1信号消失以后(即S回到0),由于有 Q端的高电平接回到(G的另一个输入端,因而电路的1状态得以保持。

当、S=0、R=1时,、。Q=0、Q′=1。在R=1信号消失以后,电路保持0状态不变。当S=R=0时,电路维持原来的状态不变。

当S=R=1时,Q=Q′=0,这既不是定义的1状态,也不是定义的0状态。

而且,在S和R同时回到0以后无法断定锁存器将回到1 状态还是0 状态。因此,在正常工作时输入信号应遵守SR=0的约束条件,亦即不允许输入S=R=1的信号。

将上述逻辑关系列成真值表,就得到表5.2.1。因为锁存器新的状态(Q(也称为次态)不仅与输入状态有关,而且与锁存器原来的状态Q(也称为初态)有关,所以将Q 也作为一个变量列入了真值表,并将Q 称为状态变量,将这种含有状态变量的真值表称为锁存器的特性表(或功能表)。

SR锁存器也可以用与非门构成,如图5.2.2所示。这个电路是以低电平作为输入信号的,所以用。SD′和R′分别表示置1 输入端和置0 输入端。在图5.2.2(b)所示的图形符号上,用输入端的小圆圈表示用低电平作输入信号,或者称低电平有效。表5.2.2是它的特性表。

由于

SDI=RD′=0时出现非定义的(Q=Q′=1状态,而且当S′和R′,同时回到高电平以后锁存器的状态难以确定,所以在正常工作时同样应当遵守SR=0的约束条件,即不应加以SD′=RD′=0的输入信号。由图5.2.1(b)和图5.2.2(a)中可见,在 SR 锁存器中,输入信号直接加在输出门上,所以输入信号在全部作用时间里(即S或R为1的全部时间),都能直接改变输出端 Q 和Q′的状态。正是由于这个缘故,也将S(S′)称为直接置位端,将R(R′)称为直接复位端,并且将这个电路称为直接置位、复位锁存器。(SetResetLatch)。