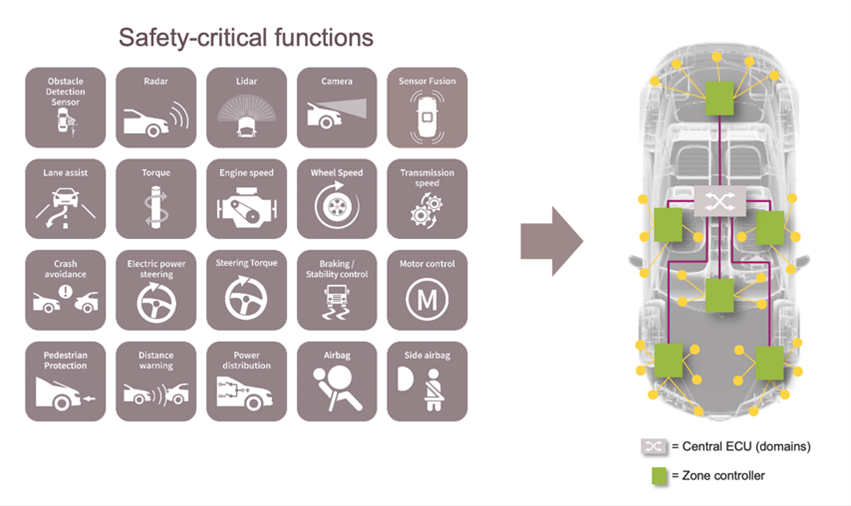

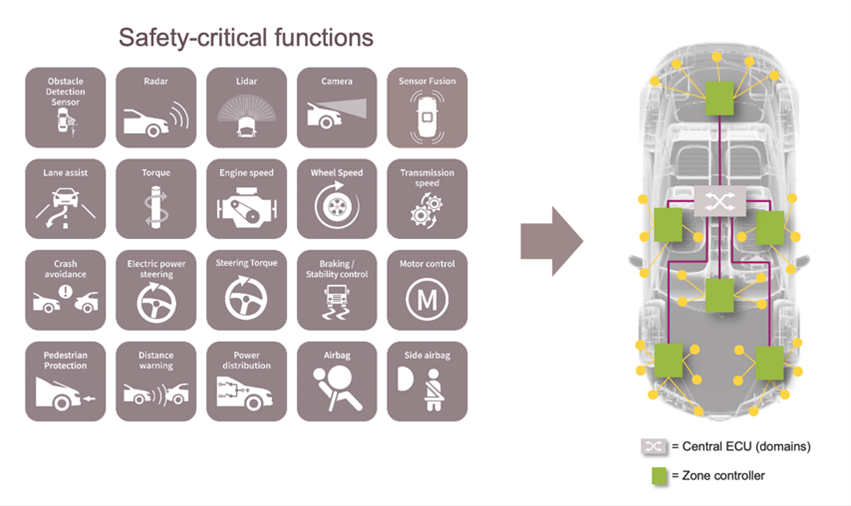

这种新功能和先进功能的结合正在对传统汽车 E/E 架构的能力造成压力(见图1)。为了满足这一需求,原始设备制造商正在通过采用域/区域架构方法将更多功能整合到更少的系统中。这些系统通常需要比集成到处理器中的嵌入式闪存更多的非易失性存储器来存储代码。

图 1域/区域架构方法整合了许多安全关键功能,并且必须能够实时处理大量数据并存储更大的代码映像。英飞凌

此外,许多此类整合系统都对安全至关重要,必须消除性能和

内存访问瓶颈,以满足实时性能的期限。,汽车系统需要能够在各种恶劣环境下运行,包括极端温度。

为软件定义车辆提供更多代码存储

汽车架构的演变和整合正在推动行业走向软件定义汽车。中央汽车计算机将连接到云端,但也需要有足够的集中处理能力,以便完全独立于云端进行关键的驾驶操作。从功能角度来看,汽车功能将转向更加以服务为导向,并保持更高水平的安全保障。

OEM 面临的部分挑战是需要l更多的代码存储,因为所有这些增加的功能和连接性反过来又需要更复杂的软件。软件存储在非易失性存储器中,因此可以现场更新。理想情况下,当处理器上有足够的嵌入式闪存来容纳所有软件时,处理器会在称为就地执行 (XiP) 的过程中直接从片上闪存执行代码。这提供了的执行性能,同时保持系统灵活性。

然而,当没有足够的嵌入式片上闪存时,软件必须存储在外部闪存中。但闪存

总线延迟和有限的吞吐量阻碍了外部闪存快速访问 XiP 的片上系统 (SoC)。因此,软件从闪存复制到更快的 DRAM 以获得必要的性能,这种方法称为“影子代码”。

但影子代码方法的代价是需要额外的 DRAM 内存以及相关的板空间来存储软件的副本。此外,系统启动时间较长,这会对用户体验产生负面影响,甚至影响操作安全。

对于下一代汽车系统,这两种方法都不够。具体来说,为了满足整合域或区域的实时要求,需要更高性能、高度集成的SoC处理器。为了实现这样的集成度,这些 SoC 必须利用更小的制造工艺节点。

这使得 SoC 能够以经济高效的方式通过单个芯片提供所有集成功能。然而,随着制造工艺节点缩小到 22 nm 及以下,以所需的密度集成嵌入式闪存变得昂贵。因此,需要一种替代 XiP 嵌入式闪存的方案。

克服外部内存瓶颈_ _

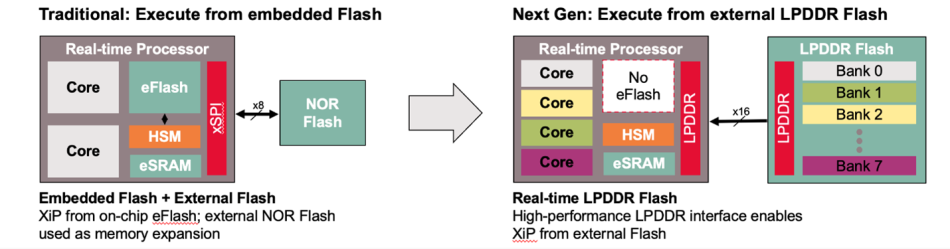

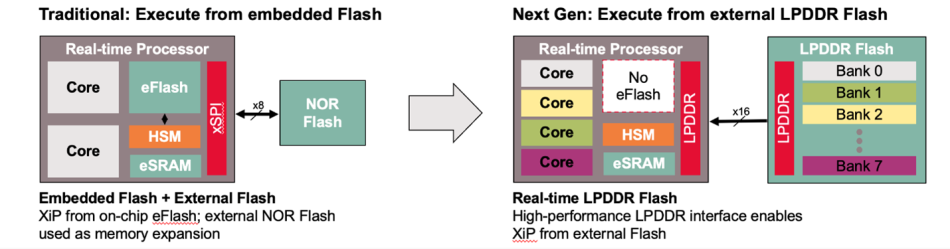

为了能够充分利用使用较小工艺节点构建的高性能 SoC,工程师需要再次转向外部 NOR 闪存。图 2a显示了一种使用外部闪存的方法,其中 SoC 可以从嵌入式闪存进行 XiP,同时使用外部 NOR 闪存作为存储器扩展。

图 2嵌入式闪存架构的传统执行方式使用外部 NOR 闪存作为存储器扩展来保存加载到 XiP 嵌入式闪存中的软件。这种方法受到嵌入式闪存容量以及 xSPI 吞吐量的限制(左)。下一代外部闪存架构执行结合了嵌入式闪存方法的灵活性和 DRAM 的性能(右)。英飞凌

前一种方法的问题是用于嵌入式闪存和外部 NOR 闪存之间

接口的 xSPI 总线的带宽有限。标准 xSPI 吞吐量为 400 MB/s,即使是 16 位,200 MHz 下的 xSPI 也只能实现 800 MB/s 的吞吐量。这远远达不到支持实时代码执行的要求。

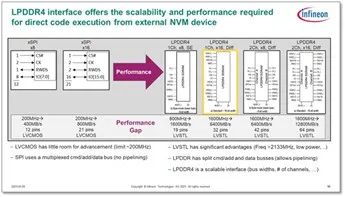

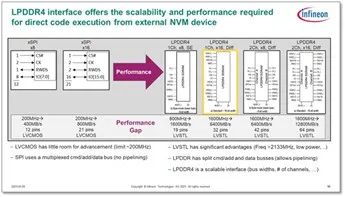

此外,xSPI 使用多路复用命令/地址/数据总线,这会对有效吞吐量产生负面影响,因为代码读取无法有效地流水线化。此外,LVCMOS 在 200 MHz 以上的发展空间几乎没有。

图 2b显示了直接从外部闪存执行代码的替代方法。该方法利用高性能低功耗双倍数据速率 (LPDDR) 接口(可从外部闪存启用 XiP),从而消除了对嵌入式闪存的需求。

LPDDR:经过验证的接口 找到了新的用例

LPDDR 是一种常与 DRAM 一起使用的存储器接口,用于高性能数据访问。LPDDR 接口经过调整,可与 NOR 闪存配合使用,并针对外部 NOR 闪存的高效 XiP 进行了优化。LPDDR 闪存具有每秒数 GB 的吞吐量潜力,可提供 DRAM 的性能以及嵌入式 NOR 闪存的非易失性可靠性和灵活性。这是两全其美的。

LPDDR NOR闪存接口成为一项引人注目的技术的因素之一是其物理层与LPDDR标准接口完全兼容。这种兼容性降低了与采用新接口相关的风险,因为 LPDDR 的信号完整性已经在市场上无数的实际应用和操作环境中得到了验证。

从较高层面来看,LPDDR NOR 闪存接口专注于代码存储和实时 XiP,适用于代码写入、多次读取的应用。因此,对接口进行了优化,以提高读取性能覆盖效率。同样,物理层未受影响,因此在控制器协议中实现了优化。这些优化旨在满足自动驾驶汽车等高性能应用的要求。

LPDDR优势

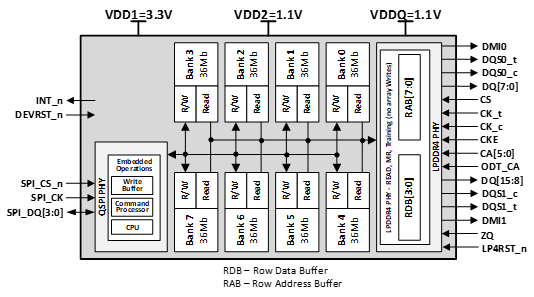

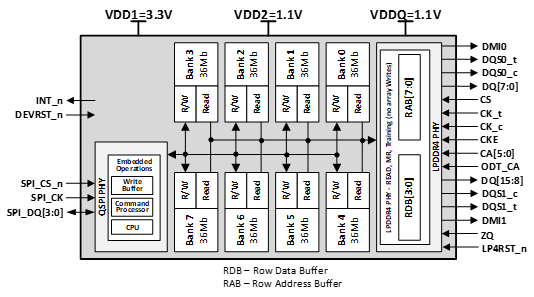

LPDDR NOR 闪存相对于 SDRAM 和基于 xSPI 的 NOR 闪存架构的优势是巨大的。以基于 LPDDR4 的SEMPER X1 NOR 闪存为例,该闪存专门针对汽车应用中的操作进行了优化。与标准 NOR 闪存相比,它提供 LPDDR 的吞吐量,以支持使用外部 NOR 闪存的 XiP(图 3)。

图 3 SEMPER X1 已针对汽车应用中的操作进行了优化,并支持使用外部 NOR 闪存的 XiP。英飞凌

整个内存架构的设计注重功能安全性和可靠性,以确保在不允许出现故障的应用中不间断运行。

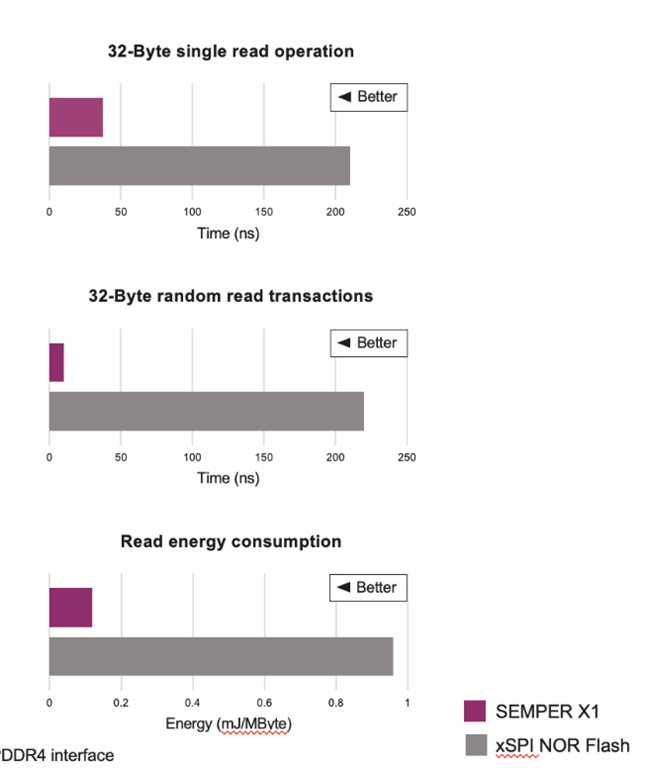

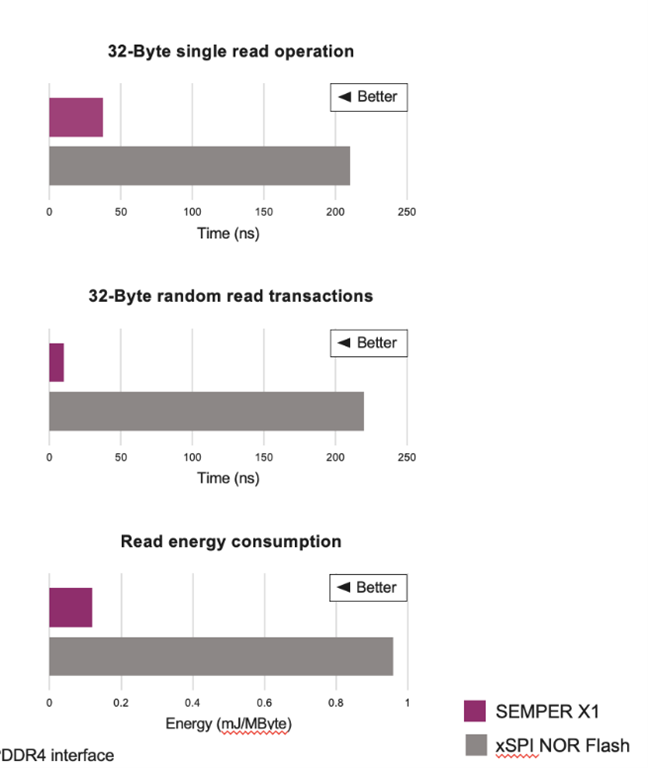

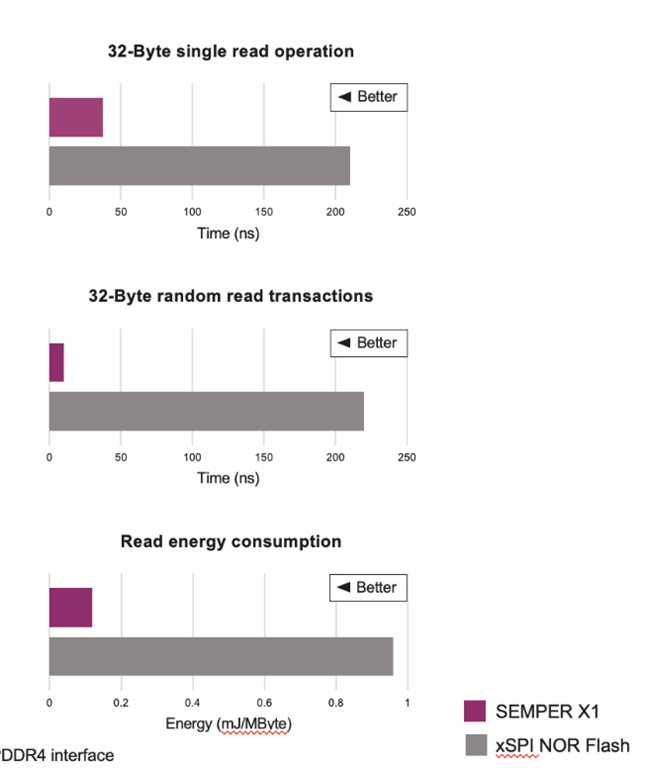

要了解 LPDDR 闪存相对于 xSPI NOR 闪存和 DRAM 的优势,请考虑 SEMPER X1 如何利用 LPDDR4 接口来提高实时性能(见图4)。

图 4如这些性能比较图所示,与 LPDDR4 SDRAM 和 xSPI NOR 闪存相比,针对数据读取访问进行优化的 LPDDR4 接口提供了卓越的性能。英飞凌

通过几种不同的优化,来自外部存储器的 XiP 成为可能,如图 4 所示:

将读与写分开

SEMPER X1 NOR 闪存具有多个端口:一个用于写入/读取的四路 SPI 和一个专用于读取的 LPDDR4。与支持写入操作相比,消除 LPDDR4 端口的写入操作可以进一步优化接口。

更快的训练

消除 LPDDR 中的写入路径就无需进行写入 DQ 训练。与 LPDDR4 SDRAM 相比,训练速度提高了 100 倍。

更快地读取命令_

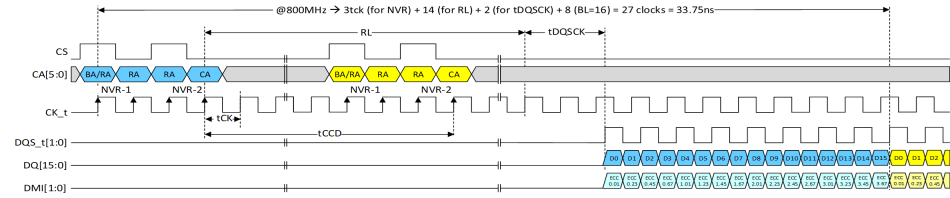

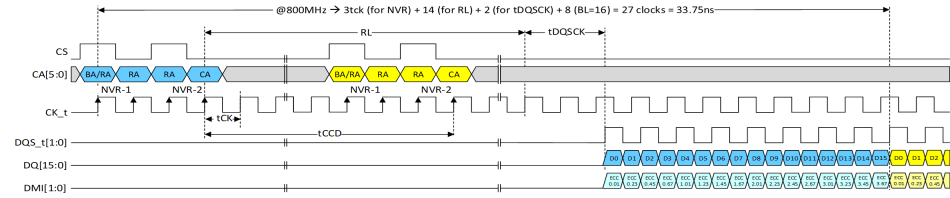

访问 DRAM 时,需要四个命令来检索数据。SEMPER X1 的 LPDDR4 接口使用更简单的格式,仅需要两个命令(图 5)。与 LPDDR4 DRAM 相比,SEMPER X1 没有存储限制、行激活或刷新,随机读取事务速度提高了 5 倍。对于从命令请求到读取数据的 32 字节单次读取操作,它的速度也比 xSPI NOR 闪存快 5 倍。

图 5 LPDDR 闪存仅需要两个命令(NVR-1 和 NVR-2)即可完成每个读取操作。英飞凌

将命令与数据分开

典型的 xSPI 接口有 8 个引脚,命令和数据必须共享该总线。相比之下,LPDDR 具有用于命令和数据的单独引脚,从而提高了命令流水线的效率。与 xSPI NOR 闪存相比,流水线随机读取事务的性能提高了 20 倍。

数据总线效率_ _

该存储器中的底层嵌入式电荷陷阱 (eCT) 技术可确保无需定期刷新来中断吞吐量。这使其能够在 125°C 下实现高达 99% 的总线效率,与 LPDDR4 DRAM 相比提高了 14%。

更好的决定论

确定性是性能一致性的衡量标准。区域控制器通常有许多并行运行的内核,以提供整合汽车系统所需的必要处理能力。当多个共享内存时,一个的访问可能会导致所有其他的访问出现延迟。此类延迟会影响实时可靠性。具有多个存储体的存储器允许每个拥有自己的存储体。这限度地减少了内存访问干扰和内核之间的相互依赖性,从而提高了整体确定性和可靠性。

零停机更新_ _

通过多个存储体,可以将无线固件 (FOTA) 更新加载到备用存储体中。更新完成并通过身份验证后,系统可以切换到备用银行,从而实现零系统停机时间无缝过渡到更新。

更好的

电源效率_

LPDDR 优化不仅仅影响性能和可靠性。与 xSPI NOR 闪存相比,SEMPER X1 每 MB 的读取能耗降低了 8 倍,同时吞吐量性能提高了 8 倍。对于高性能应用程序,这些节省会快速增加。

优于影子代码_ _

LPDDR 闪存能够提供 3.2 GB/s 的吞吐量,使其 XiP 性能与使用影子代码方法的 SDRAM 相当。此外,LPDDR 方法需要更少的内存 IC,具有更快的设置时间,并且消耗更少的能源,使其成为 SDRAM 的引人注目的替代品。

面向未来的可扩展性

LPDDR 的一个关键优势是它是一个可扩展的接口,可以支持未来日益复杂的汽车应用。xSPI 的扩展能力受到限制,因为 LVCMOS 在 200 MHz 以上的提升空间很小,带宽上限为 400 MB/s (x8) 和 800 MB/s (x16)。简而言之,xSPI 已经跟不上了。

另一方面,LPDDR4 允许高达 1,600 MHz 的频率,并且可以将吞吐量从 1,600 MB/s 扩展到 12,800 MB/s(图 6)。凭借如此广泛的容量范围,LPDDR4 可在日益先进的系统中提供 XiP 所需的可扩展性和性能,而新一代 LPDDR 则可提供更大的空间。

图 6 xSPI 的扩展能力有限,性能上限为 800 MB/s (x16)。相比之下,LPDDR4 支持高达 1,600 MHz 的频率,并且可从 1,600 MB/s 扩展到 12,800 MB/s,从而为当今和未来日益复杂的汽车应用提供 XiP 所需的可扩展性和性能。英飞凌

随着车辆的计算负载和软件复杂性随着自动化程度的提高、便利性和先进的用户体验的增加而增加,需要更大的代码存储空间。许多软件定义的功能都是关键任务,需要实时代码执行来保持可靠性和安全性。

为了保持性能和效率,当今的汽车应用需要快速的底层存储器阵列来充分利用所有可能的效率。然而,在先进制造工艺节点,汽车级嵌入式非易失性存储器技术面临着高成本(芯片面积)和缺乏可扩展性的问题。需要外部存储器方法,但日益软件定义的车辆架构的需求超出了当今的 xSPI NOR 闪存的能力,而后者根本无法提供实时 XiP 性能。

LPDDR 是下一代汽车系统的关键技术,提供与外部闪存的接口,具有足够的性能,为域和区域控制器提供实时计算和 XiP 功能。凭借随机读取事务速度提高 20 倍、每兆字节读取能耗降低 8 倍等效率,LPDDR 使下一代车辆能够提供先进的功能,并增强安全性和架构灵活性。