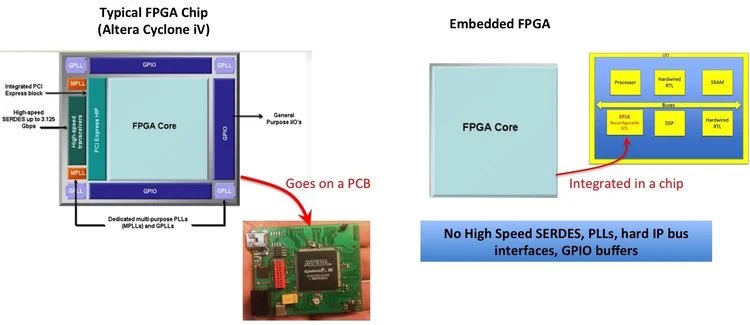

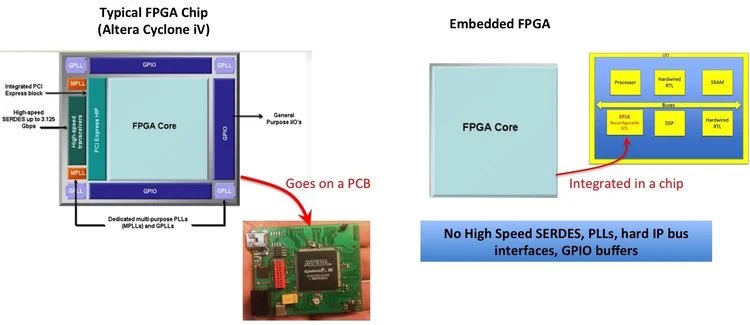

由于嵌入式 FPGA 是一项新技术,因此我们首先强调它与已经存在了数十年的标准 FPGA 的不同之处。基本上,嵌入式 FPGA 是一个 IP 块,允许将完整的 FPGA 集成到 SoC 或任何类型的

集成电路中。正如 RAM、SERDES、PLL 和处理器从独立

芯片过渡到常规 IP 块一样,FPGA 现在也是一个 IP 块。

FPGA 在可编程互连结构中组合了一系列可编程/可重新配置逻辑块。在 FPGA 芯片中,芯片的外缘由 GPIO、SERDES 和专用 PHY(例如 DDR3/4)的组合组成。在 FPGA 中,I/O 环大约占芯片的 1/4,“结构”大约占芯片的 3/4。在当今的 FPGA 芯片中,“结构”本身主要是互连,其中 20-25% 的结构区域是可编程逻辑,75-80% 是可编程互连。

嵌入式 FPGA 是一种没有 GPIO、SERDES 和 PHY 周围环的 FPGA 结构。相反,嵌入式 FPGA 使用标准数字信号连接到芯片的其余部分,从而实现非常广泛、非常快速的片上互连。

嵌入式 FPGA 内部:原始构建模块

FPGA 中的可编程逻辑块是一个查找表 (LUT),可以通过编程实现任何布尔函数:4、5 或 6 个输入以及 1 个或 2 个输出。

在 Flex Logix EFLX 阵列中,LUT 是双 4 输入 LUT,可以组合形成 5 输入 LUT。LUT 输出可选择存储在

触发器中。LUT 通常分为四个组,并带有进位逻辑,以方便加法器和移位器。

另一个可编程逻辑块是 MAC(乘法器累加器)或 DSP 加速器块。

在Flex Logix EFLX阵列中,有一个22位预加器、一个22x22乘法器和一个4位后加器/累加器。MAC 可以组合或级联以形成快速的 DSP 功能。

可编程逻辑块通过配置位进行编程,这些配置位设置 LUT 的值、选择是否使用触发器、是否旁路、激活或不激活进位逻辑等。配置位还对 MAC 的操作进行编程。通常在 FPGA 中,配置位是从外部闪存加载的。

对于嵌入式 FPGA 来说,情况是一样的,因为几乎所有 SoC 都有 ARM/ARC/MIPS/等。从外部闪存启动的处理器。同一闪存用于存储嵌入式闪存的配置位。

可编程逻辑块接收输入并将输出发送到互连网络,该互连网络允许以可编程方式与 FPGA 结构中的任何逻辑块建立连接。互连结构也通过配置位进行编程。互连结构通常是 FPGA 结构的主体。

嵌入式 FPGA 的一个主要区别在于互连结构的设计。的互连使用更少的面积和更少的金属层,同时提供高资源利用率。

与 FPGA 芯片不同,嵌入式 FPGA 中没有 PHY/SERDES/PLL。有一个“I/O”环,但它实际上是与芯片其余部分的简单数字互连。嵌入式 FPGA 将具有数百到数千个互连,可以在芯片内全速运行。I/O 宽度和带宽的增加是在芯片中嵌入 FPGA 的巨大优势。

嵌入式 FPGA 内部:构建任意大小和配置的阵列

复杂性之一是客户需要各种尺寸和配置的嵌入式 FPGA,并且每个人都希望 IP 模块在芯片中使用之前经过硅验证。

例如,在 16nm 中,一位客户可能只需要几百个可编程逻辑 LUT,即可实现在约 1GHz 下运行的快速可重新配置控制逻辑;而同一流程中的另一个客户可能需要 50K-100K LUT 用于数据中心处理器加速器。如何才能以少的设计投资和快的上市时间让这些客户满意?

Flex Logix 使用可平铺的构建块方法。首先,使用上述方法设计了4个EFLX IP核。每个 IP 核都是独立的 FPGA,但它们也可以通过逻辑/DSP 的任意组合进行排列以提供 EFLX 阵列,总共约 75 个,从 100 个 LUT 到 122.5K LUT。

每个 EFLX IP 核都有一个额外的顶层互连,允许一个核自动连接到周围的邻居,以形成高达 NxN 的大型阵列。

EFLX-100 阵列多达 5x5 或 3,000 个 LUT(EFLX-100 中实际上有 120 个 LUT)。

EFLX-2.5K 接管了 2500 个 LUT 和多达 122.5K LUT 的阵列。

阵列可以是全逻辑或全 DSP 或两种类型内核的任意混合,如下所示:

还可以在嵌入式阵列中嵌入大量 RAM。Flex Logix 通过使用标准 RAM 编译器生成客户请求的任何类型的 RAM(单端口、双端口;ECC/奇偶校验/无;任意数量)并将 RAM 放置在内核之间来实现此目的。RAM 是单个 EFLX 阵列的一部分。

使用上述方法允许几个 IP 核生成几乎无限多种嵌入式 FPGA 阵列,以满足任何客户的要求。

嵌入式 FPGA 内部:证明硅中的构建模块

Flex Logix 构建验证芯片来验证硅中的 IP 核。以下是 TSMC 40ULP 中的示例。

在此过程中,客户使用多种 VT(电压阈值模板)组合,Flex Logix 设计的 EFLX 阵列与所有可能的组合兼容。因此,验证芯片有五个阵列:一个大阵列(4x4)采用需要的 VT 组合,四个 2x2 阵列采用其他四种尺寸。

由于 40nm 的 EFLX 阵列可以在高达 300MHz 的频率下运行,而 GPIO 仅在约 150MHz 时可靠,因此有一个片上 PLL 可以生成非常快速、的时钟来测试性能,并且有 SRAM 可以启用“测试向量库” ”被加载然后全速运行,结果输出到另一个银行。这提供了“芯片上的

测试器”,以便可以在高于 GPIO 速度的情况下验证全速操作。还有温度/电压

监视器,以确保在目标、坏情况条件下进行测试。