本应用笔记展示了总线保持功能的重要性,尤其是在 CMOS 电路上。它讨论了总线在系统中的工作原理以及良好运行所需的规范。此外,还将解释一些应避免使用此功能的应用程序。

简介

本应用笔记展示了总线保持功能的重要性,尤其是在 CMOS 电路中。它讨论了总线在系统中的工作原理以及良好运行所需的规范。此外,还将解释一些应避免使用此功能的应用程序。

什么是布斯霍尔德?

总线功能是解决浮动输入问题的创新方法。该电路在空载输入上保持有效的逻辑状态,并且无需用于浮动或未驱动输入的外部调节组件。

总线电路设计用于承受浮动输入条件。如果使用非总线器件,这些浮动输入条件将导致泄漏、振荡增加,并损害系统数据完整性。

总线保持电路的另一个特点是能够将未驱动的数据总线线路保持在有效的逻辑状态。通过总线,总线保持设备可以调节总线上的其他输入。

它是如何工作的?

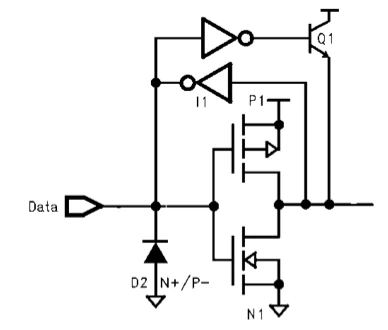

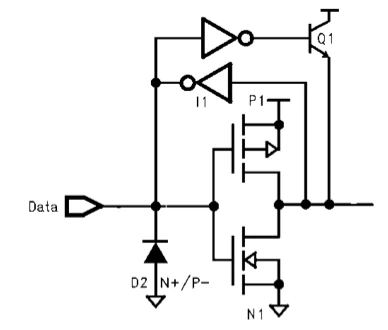

总线保持电路的工作原理是在器件输入级中使用低驱动反相器,为器件和总线的输入提供反馈(参见图 1)。

当驱动输入的信号被移除时,

逆变器将维持器件输入和总线上接收到的有效信号电平,直到被下一个输入信号过驱动。

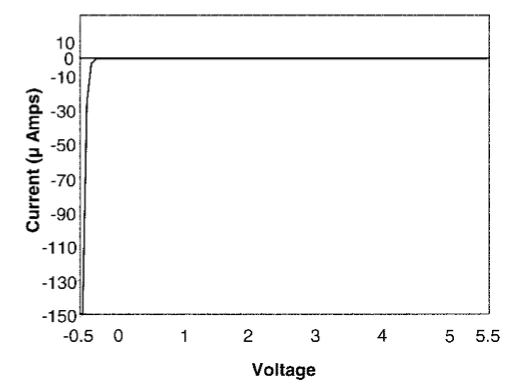

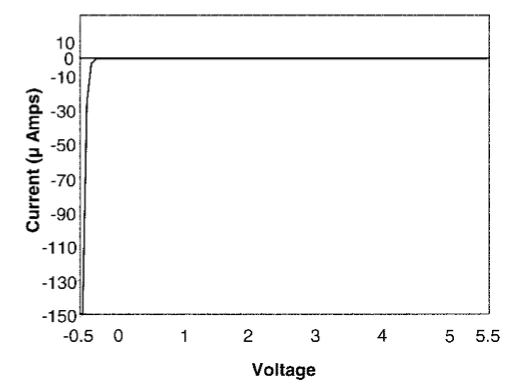

飞兆半导体提供两种母线逆变器规格(见图 2)。II(HOLD) 是总线输入驱动。这是电路能够提供的电流量。II(OD) 是改变状态的总线输入过驱动电流。这是克服总线保持电路并导致输入改变状态所需的电流量。

何时使用 Bushold?

具有总线保持的设备设计用于设备或数据总线线路处于非驱动状态的系统中。如前所述,总线保持电路将浮动输入或数据总线保持在有效状态。

非总线保持输入必须保持有效的逻辑状态。让输入悬空将导致其振荡并导致输出数据无效。错误数据问题可能导致总线争用、高电流消耗以及设备或系统损坏。

出于与单个设备输入需要调节相同的原因,系统数据总线必须保持在有效的逻辑状态。

如果允许总线浮动,则可能会出现数据完整性问题以及设备或系统损坏。然而,对于数据总线,总线上设备输入的数量使问题更加严重。

Fairchild 的带有总线孔的 CROSSVOLT 产品尤其适用于间距较小的电路板。此处,总线保持功能无需额外的调节电阻焊盘,也无需添加接地或

电源走线。

通过将设备或总线保持在接收到的有效逻辑高或低电平,具有总线保持的设备还可以提供伪

存储器功能。相反,调节

电阻器始终将总线拉至相同状态。

当使用具有总线保持的设备设计数据总线时,必须考虑总线保持驱动和电流要求。当 II(HOLD) 指定为 ±75μA 时,具有总线保持的单个器件将保持较大的数据总线,并将功耗保持在较低水平。必须考虑总线上所有设备输入的 IIN(输入电流)的计算。对于 CMOS 器件,IIN 通常在 1μA 至 5μA 范围内。

当 II(OD) 指定为 ±500μA 时,数据总线仍然可以轻松切换。CMOS 器件的驱动范围通常为 ±24mA 或更大。

什么时候不应该使用Bushold?

在某些设计应用中,总线技术要么不合适,要么不应该过度使用。在这些设计中,建议使用不带总线保持电路的等效性能器件。Fairchild Semiconductor 提供的 CROSSVOLT 器件(见图 3)与带有总线保持的 CROSSVOLT 产品具有相同的驱动和交流规格,但输入端没有总线保持电路。

所有系统或数据总线输入上的总线电路都会产生问题。在具有多个接收器子站的数据总线上,应在将数据总线保持在有效状态所需的少数量的设备上使用总线保持电路。II(OD) 规范对于数据总线上的每个总线保持电路都是附加的。例如,使用 II(OD) 规格为 ± 500 μA 的 LVT,如果数据总线上的 10 个输入具有总线保持电路,则至少需要 5mA 来克服和切换数据总线。使用 II(HOLD) 规格为 ±75μA 的 LVT,可提供 750μA 的驱动来保持理论上的 10 输入总线。全 CMOS 输入总线不需要如此多的

驱动器,并且不必要地增加了系统所需的功率预算。

总线保持电路设计用于代替调节上拉或下拉电阻。将总线输入与调节电阻结合使用会导致高功耗。如果调节电阻器和总线输入的负载足够高,驱动器可能无法在要求的时间内切换负载。