Microchip USB 集线器控制器的成功运行需要特别考虑印刷电路板 (PCB) 布局。所有 Microchip Hub 控制器均包含敏感模拟电路、数字逻辑和高速 I/O 电路。PCB 的设计是所有这些子系统的系统电路的一部分,可以增强或削弱所需的操作。

涵盖了放置和堆叠等一般问题。此外,还讨论了 USB 2.0/3.1 Gen 1 信号/阻抗、晶体连接和其他关键电路等子系统问题。还将讨论 EMI 控制、系统电源分配和信号返回路径管理。

所提供的指南取代了之前针对适用设备的说明。以下建议基于 Microchip 的经验和知识,可能会被接受或拒绝。Microchip 不保证任何设计。每个公司终负责确定自己设计的适用性。

机箱和

电缆接地

USB集线器设备可以通过以下方式实现:

嵌入主机控制器

嵌入了具有嵌入式设备的不可访问端口和用户可访问端口的组合

嵌入主机、嵌入式设备不可访问的端口以及用户可访问的端口的组合

独立的集线器

每个实施细节都会影响将机箱和 USB 电缆屏蔽层连接到数字接地的方法。建立这些连接的方法取决于设计的系统细节。请参阅互联网上有关此主题的许多参考文档和白皮书,尤其是由 USB 联盟成员以及支持 USB 的主板和设备提供商发布的文档和白皮书。

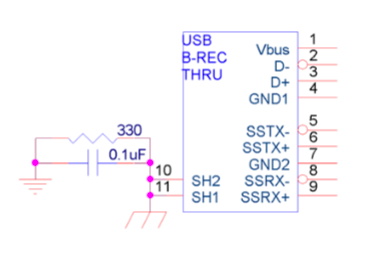

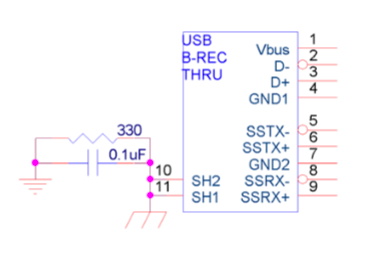

Microchip 在每个 USB 连接器处通过 RC 网络(并联 330 Ω

电阻器和 0.1 ?F

电容器)将 USB 电缆屏蔽层连接到数字接地时,在独立设计中观察到了积极的 EMI 和 ESD 行为。

图 1 机箱接地连接示例

图 1 机箱接地连接示例

VDD12 和 VDD33 电源调节器

USB57x4 和 USB553x 系列集线器使用两种外部电源电压:1.25 V 的 VDD12 和 3.3 V 的 VDD33。

VDD12 轨用于数字功能和 USB 3.1 Gen 1 PHY。集线器设备消耗的VDD12电流会有很大差异。当设备处于“挂起”状态时,它消耗的电流非常少。当所有 USB 3.1 Gen 1 SuperSpeed 接口均处于活动状态时,它将消耗电流。所选

稳压器必须在所有功耗范围内稳定、低噪声且准确。

USB57x4 和 USB553x 器件的 VDD33 轨由 PLL 和其他电路使用。此外,USB25xx 设备从 VDD33 派生内核和其他电源轨。因此,VDD33 电源必须非常干净。VDD33 上的噪声必须在被集线器设备接收之前被滤除。某些系统要求集线器设备引脚上的 VDD33 纹波小于 5 mV,才能通过 USB 3.1 Gen 1 测试套件的 SSC 。

开关稳压器是 VDD33 噪声的常见来源。

图 1 机箱接地连接示例

图 1 机箱接地连接示例