由于半导体行业的发展,对具有金属源极和漏极

触点的肖特基势垒 (SB) MOSFET 的研究正在不断扩大。肖特基势垒 MOSFET 的源极和漏极由硅化物制成,而不是通常的掺杂硅。SB MOSFET 的一个显着特征是独特的

二极管,如 I d -V ds特性的三极管工作期间呈指数电流增加。当将此类器件应用于具有微小偏置电压的

逻辑电路时,发生这种情况的可能性很小。

半导体界面处的费米能级钉扎通常发生在带隙内。这会导致接触通道界面处出现明显的 SB。这会显着影响SB MOSFET 的电气特性,导致通态性能和开关动作下降。

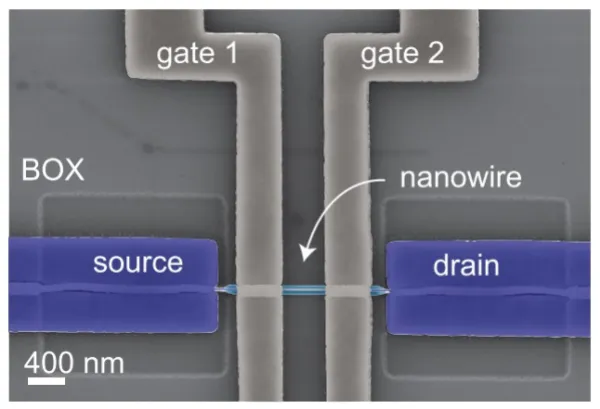

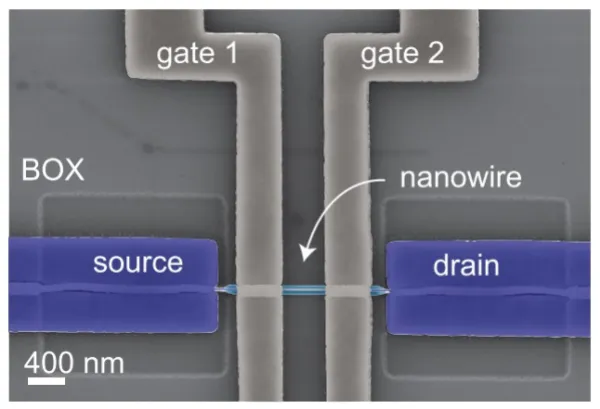

本文介绍了 SB MOSFET 的特性和特性,以及为什么亚线性是由源极侧而不是漏极侧造成的。为了支持要使用的各种实验和模拟,使用了具有硅化镍源极和漏极接触的双栅极硅纳米线

晶体管。

该晶体管有两种工作模式:在种模式中,栅极 1 用于控制流经器件的电流,同时,在栅极 2 上施加大于栅极 1 的 Vgs 的恒定电压。操作时,编程栅极位于源极,控制栅极位于漏极,其中两个电极的边缘场调制两个栅电极之间未覆盖的硅沟道(p型,1015 cm -3 )的电荷载流子浓度从而允许设备正常运行。单击此处访问原始文章。

肖特基势垒二极管次线性行为分析的仿真

双栅极纳米线 FET - 肖特基势垒

图 1:双栅极纳米线 FET

为了研究 SB FET 的次线性 I d -V ds行为,使用非平衡格林函数形式进行了自洽泊松-薛定谔模拟。到目前为止,我们考虑的是具有金属触点的纳米线 FET,其源极触点处具有 SB Ф s SB,漏极触点处具有 Ф d SB,如图 1 所示。

SB-MOSFET 沿电流传输方向的导带和价带

图 2:SB MOSFET 沿电流传输方向的导带和价带

如图2所示,假设源极和漏极与纳米线接触,这适用于硅化物接触,并且描述了沉积到纳米线的接触和金属纳米线耦合,这并不弱。对于这个实验,假设了 dnw 纳米线,它足够薄,可以解释一维电子传输,可以认为在很宽的沟道掺杂浓度范围内完全耗尽。因此,这会改变沟道掺杂中的内置电势 Фbi。该设备的静电可以在泊松方程中进行修改。

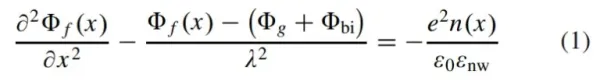

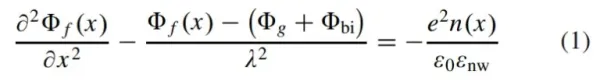

方程 1.-1-D 修正泊松方程

从上式中,λ 是电势变化的屏蔽长度尺度,反映了所考虑的器件几何形状,Ф g + Ф bi是栅极和内置势能,Ф f (x) 是沟道处的势能介电界面。此外,n(x) 是移动电荷密度,ε0 是纳米线的真空和相对介电常数。

仿真后得到的结果

在单栅极器件的情况下,λ = ((ε nw /ε ox )d nw d ox ) 1/2 ,其中使用 d nw = 1 nm 和 d ox = 4 nm可以获得相同的屏蔽。因此,两种情况下的屏蔽长度 λ 都是常数,从而导致电荷密度和电势的差异。

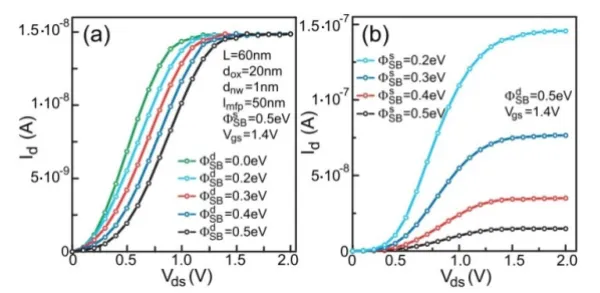

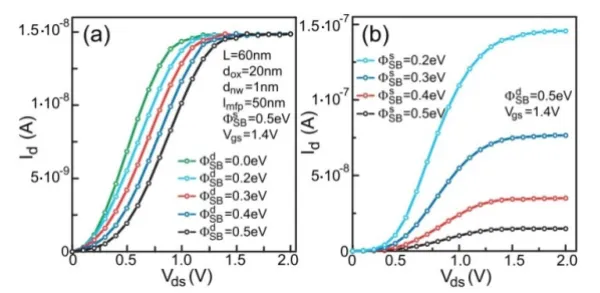

纳米线 SB-MOSFET 的输出特性 - 肖特基势垒

图 3:纳米线 SB MOSFET 的输出特性

次线性行为随着 Φ d SB的减小而减小,并且可以看出漏极端的肖特基势垒消失。当观察不同偏置电压的导带时,可以理解次线性行为的原因。