功耗较低的便携式和嵌入式产品在当今竞争极其激烈的市场中具有非常显着的优势。每一代产品规划都必须满足功能和性能的大幅提高以及功耗的大幅降低。对于

电池供电的嵌入式和便携式(通常是无线)消费

电子系统来说尤其如此。

这些便携式产品的体积在每一代产品中都变得越来越小,但消费者却越来越期待更多更好的功能(这需要更高的处理能力和性能)并要求更长的电池寿命。例如,除了实际拨打电话之外,现代

手机还可能具有以下功能:充当个人记事本;玩游戏; 拍摄、传输和接收静态图片和/或短视频;浏览网络; 等等。

过去,下一代产品规划的重点主要集中在底层微处理单元的微架构上。然而,处理器微架构的改进通常仅产生关于性能提高的二阶或三阶效应。

相比之下,整体硬件(平台)架构以及其上运行的软件的架构和算法内容都在系统层面具有一阶效应。

创建的低功耗设计需要在硬件架构、软件架构和底层软件算法方面进行复杂的权衡。成功的功耗敏感设计的创建需要系统架构师和工程师(硬件和软件)能够准确有效地执行和量化此类权衡。为了实现这一目标,建筑师和工程师需要能够在设计过程的早期访问和分析功率数据。

电源管理虚拟原型

虚拟原型 (VP) 和虚拟系统原型 (VSP)是建模、分析和优化实时系统电源需求和权衡的强大而有效的方法。使用此类工具,可以对硬件架构和软件算法进行非常和增量的更改,从而显着影响系统的功耗。

但手机等复杂系统(包括其软件)的性能和功耗等特征无法作为正式的数学问题来表示和计算。确定此类特性的现实解决方案是某种形式的模拟。

此模拟的一种选择是硬件加速和/或仿真。不幸的是,除了仅提供对系统内部工作的有限可见性之外,这些解决方案支持的抽象级别是寄存器传输级(RTL)表示。

因此,直到设计周期很长一段时间,当设计的硬件部分基本完成时,开发和评估才能开始。反过来,这限制了设计团队探索、评估和优化硬件架构的能力。此外,处理器的 FPGA 实现通常很慢,以大约 1 MIP 的速度执行软件,比同一处理器的虚拟处理器模型慢大约 50 倍。

虚拟原型(VP)和虚拟系统原型(VSP)的相关概念提供了解决方案。VP 是电子系统硬件部分的功能且定时的软件模型。这样的模型通常包括处理器内核、内存子系统、外围设备、总线、桥接器、机械和射频设备等。相比之下,VSP 是整个系统的模型:即 VP 和在其上运行的软件的组合。

全面评估复杂系统的特性可能需要对各种系统配置进行数百次实验。此外,单个模拟需要运行 1000 亿条指令来重现问题或计算代表性结果并不罕见。这意味着使用高性能、定时的 VSP 的仿真时间不到一小时。

相比之下,使用非典型定时结构指令集

仿真器 (ISS) 模型进行相同的软件仿真需要 100 到 500 小时或更长时间,而使用 RTL 模型则需要 100,000 小时或更长时间。

使用 VSP 的一个关键优势是系统的硬件和软件部分可以同时开发和评估。VSP 允许在真实软件工作负载下快速、轻松地测试和分析不同的硬件架构。在开发硬实时软件代码时,其执行会产生跟踪数据(来自插入模型的

探针),其中包括性能(时序、反应时间、延迟时间等)和功率数据以及正常的调试数据。

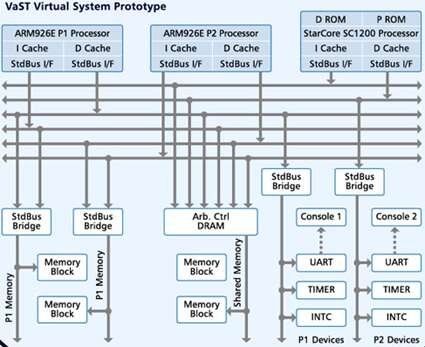

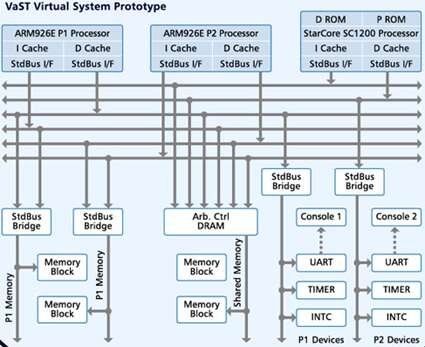

使用 VSP 进行手机功耗建模 为了更好地了解 VSP 方法,让我们看看如何在由两个 ARM926E 处理器、一个 StarCore SC1200 处理器、分层总线组成的

手机系统中使用它(如下图一)和内存子系统以及各种外设。

图1:3G手机控制器VSP

有许多技术可以构建系统属性(例如功率)的目标函数。经典技术是跟踪事件频率和/或延迟,并根据对功率计算有显着贡献的事件构建功率函数。相比之下,VSP 可以在运行真实软件工作负载的替代硬件和软件架构的背景下进行功耗分析。

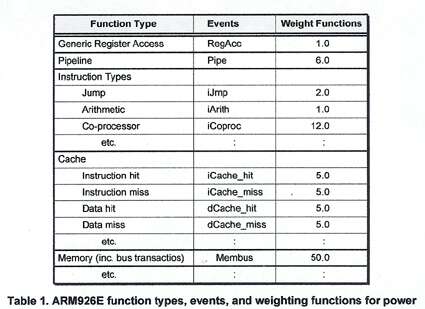

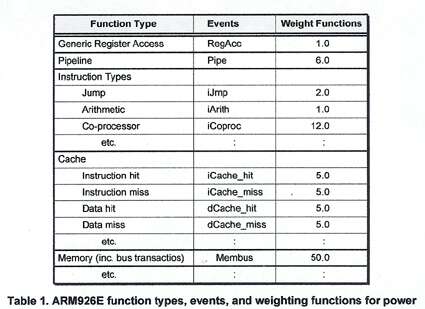

VSP 的步是为影响系统整体功耗的每一类功能分配“权重”。作为一个简单的示例,我们可以首先为通用寄存器文件访问分配默认权重 1.0,然后将其他权重设为该默认权重的倍数。考虑可能与 ARM926E CPU 及其缓存和内存访问相关的一些权重,如下表 1所示。

从这里可以看出,每个函数类别的权重 (W) 已设置为通用寄存器访问函数的常数倍。然而,这些权重可以用更复杂的函数来表示;例如,缓存命中/未命中权重可以各自是缓存结构(大小、方式、策略等)的函数。

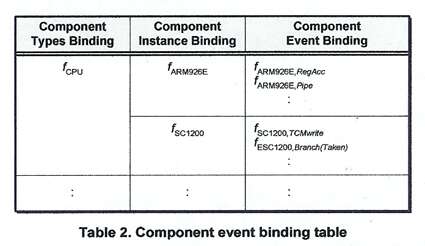

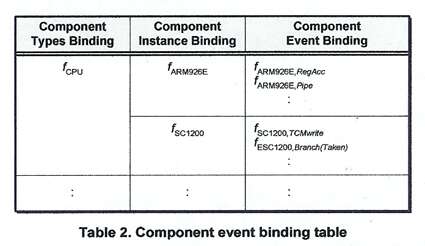

下一步是构建一个定义组件绑定的解释表,如下表 2所示。尽管这些表很大,但事件绑定本身很容易实现,因为每个表通常都是指向函数的指针和事件的历史缓冲区。

在功率计算的情况下,要计算的基本函数是瞬时功率函数,它计算在一段时间内或一定数量的事件(例如时钟周期)内消耗的总能量。基于此瞬时功率,可用于优化目的的两个主要派生函数是:

1) 特定时间内消耗的功率(这将是瞬时功率的值);2

) 整个实验过程中消耗的平均功率。