尽管数字信号处理无处不在,但它并不总是可见,就像数码相机和移动电话一样。传统上使用模拟电路实现的越来越多的功能现在包含在

微控制器单元 (

MCU) 或数字信号处理器 (DSP) 上的软件中,从而节省了印刷电路板空间和组件,从而降低了成本。

模拟设备常见的漂移和容差也可以避免。Fujitsu 的 MB91470/480 系列微控制器展示了这些软件算法的集成 DSP 单元的优势。

当今的许多

滤波器和算法很难使用模拟电路来实现,至少会产生不合理的费用。如今,开发人员必须决定是使用 MCU、DSP 还是两者都使用。特别是在信号处理只是其中一项任务的应用中,这个问题并不总是那么容易回答。控制和操作设备是 MCU 的典型,而数字滤波器和调节器是 DSP 的典型。

然而,对于经常采用数字滤波器来评估系统状态并执行快速循环的控制单元来说,这种明显的差异并不总是那么明显。富士通认识到电机控制的情况就是如此,因此开发了 MB91470/480 32 位 MCU 系列,该系列具有 ?DSPalias MAC(乘法累加)单元形式的强大外设。

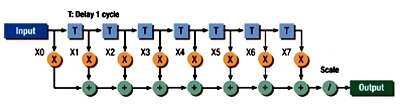

DSP 拥有自己的程序和数据存储器,使其能够作为独立于主处理器 (CPU) 的协处理器执行更长的计算,如下图 1 所示。 这使得 CPU 在滤波器计算期间也能够对中断快速做出反应,这是工业控制任务所必需的功能,而无需更改滤波器的执行时间。

图1:μDSP框图

DSP 的结构针对数字滤波器和许多其他算法的典型乘法累加指令进行了优化,它仅在一个周期内以全处理器时钟速度(高达 80MHz)执行。72 位宽累加器将值相加,数字格式选自各种 32 位定点格式。

特别是对于数字滤波器,μDSP 能够通过滤波器级传输输入变量,而无需 CPU 的帮助。只要 ?DSP 空闲,CPU 就可以完全访问 ?DSP 的所有配置和内存地址,从而可以与 CPU 进行数据传输。一旦开始计算,一些状态和控制寄存器将保持可访问状态以指示其操作状态。当 ?DSP 执行程序时,它可以生成中断或触发 DMA(直接内存访问)传输。

现代传动系统需要电力

控制现代三相

驱动器是一种应用示例,其中需要在固定时间间隔内处理大量子任务,这些时间间隔由系统要求决定。通常,使用矢量或场定向控制,由多个坐标变换和级联控制循环组成。两个电流控制器形成内层的控制回路,并监控定子电流的磁场和扭矩产生分量。

该控制环路通常以全 PWM(脉宽调制)频率循环,该频率可以达到数十 kHz。内部控制环路的设定点由速度调节器确定,速度调节器控制所需的扭矩,从而通过电流控制加速度。然后通过定位控制进行预连接。因此,除了矢量控制的三角变换和应用本身之外,还有四个控制过程需要掌握。

如果考虑到这种控制的时间间隔,一些子任务可以并行执行。例如,扫描实际电流值和下可能用新目标值更新PWM寄存器之间的时间通常是一个PWM周期。

由于 CPU 和DSP 进行并行计算,因此可以轻松实现附加功能,而无需增加有效的 CPU 负载。MAC 单元执行典型 PID 算法所需的时间远少于一微秒,这就是 ?DSP 可以承担更多职责的原因,例如在两次 PWM 更新之间过滤输入信号。与 MCU 的灵活定时器一起,可以实现非常动态的三相驱动器。

MB91480 系列甚至可以为两个电机实现这一点。在这种情况下,MAC 单元可以接管两个电机的所有 6 个 PID 控制环路(位置环路通常具有附加功能,例如防寻机等,这些功能更容易在 CPU 上实现),从而在执行时间方面带来好处变得更加明显。

与 MB91480 系列 MCU 的灵活电机定时器和 ADC 功能一起,可以优化两个电机控制的时序,从而限度地减少外设使用的干扰。为了实现这一点,两个电机的 PWM 相互偏移大约四分之一的 PWM 周期。通过这种方式,ADC 单元可用于同时采样每个电机的相电流并与 PWM 同步,从而为每个控制提供自己的时隙以使用外设。

对所有电流进行采样后,μDSP 被触发并执行 PID 计算。由于执行时间短,控制输出在个 PWM 需要值之前就被更新得足够早,因此 PWM 可以以的延迟更新到新的输出电压。也就是说,个电机控制的响应时间不受添加第二个电机控制的影响;两者仍可在 20kHz 的全 PWM 频率下保持。

为了将控制回路有效地映射到类似 DSP 的结构上,必须满足某些要求。首先,大多数微控制器和DSP都没有配备浮点单元,因此采用定点运算代替。然而,调节器的结构也可以优化。

通过一些改造,典型的离散 PID 调节器可以转换为 IIR(无限脉冲响应)滤波器式结构。该实现还避免了积分项的求和。它具有数字滤波器典型的“乘积和”形式,并且 ?DSP 已针对该形式进行了优化。

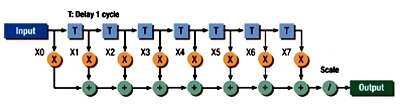

图2:FIR8滤波器

DSP 代替 RC

在许多应用中,有必要评估模拟读数,但噪声等干扰可能会成为一个问题。这通常可以通过模拟低通滤波器来减少,但也可以通过数字方式实现。原则上,模拟抗混叠滤波器对于几乎所有 AD 转换都是必需的,但数字滤波可以通过过采样来压平对模拟预滤波器的要求。

为了实现必要的带宽,这使用了比根据奈奎斯特定理所需的采样频率(避免混叠所需的采样率,等于信号频率的两倍)更高的采样频率。因此,可以使用具有低边缘陡度的更简单的滤波器,其中对目标频率范围的限制以及采样率的降低是数字的,从而避免额外的电路复杂性。

常用过滤器。FIR(有限脉冲响应)或 IIR 是常用的滤波器。FIR 滤波器是非递归的,因为没有输出到输入的反馈。因此它们总是稳定的,产生有限长的输出信号。相比之下,IIR 滤波器可能会谐振并变得不稳定,但通常需要更少的滤波器级才能实现指定的行为。由于 ?DSP 自行执行滤波器计算,因此通常可以使用易于使用的 FIR 滤波器,而无需增加 CPU 负载(上图 2)。

“移动平均”滤波器是典型的简单 FIR 滤波器。它通常用作简单的低通滤波器,提供平滑的测量读数。所有滤波器系数都具有相同的值,并且通常以滤波器系数之和(表示滤波器的 DC 增益)等于 1 的方式进行缩放(归一化)。MB91470 的 ?DSP 可以在大约 1.2 微秒内计算出具有 64 级的滤波器。因此,MB91F479 中两个 12 位 ADC 的完整采样率都可以与该滤波器一起使用,或者可以同时计算多个较短的滤波器。