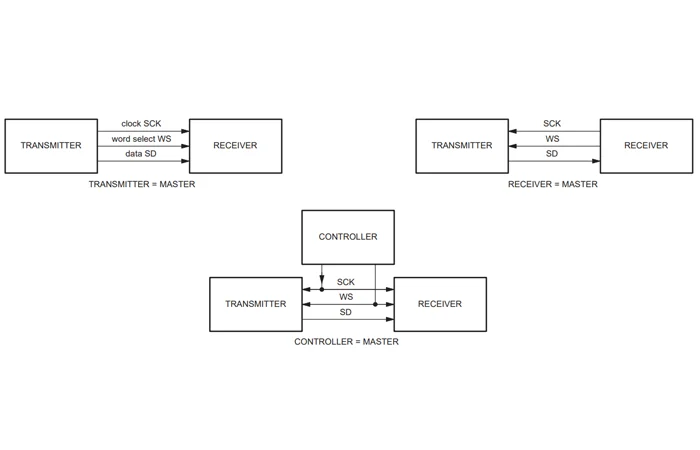

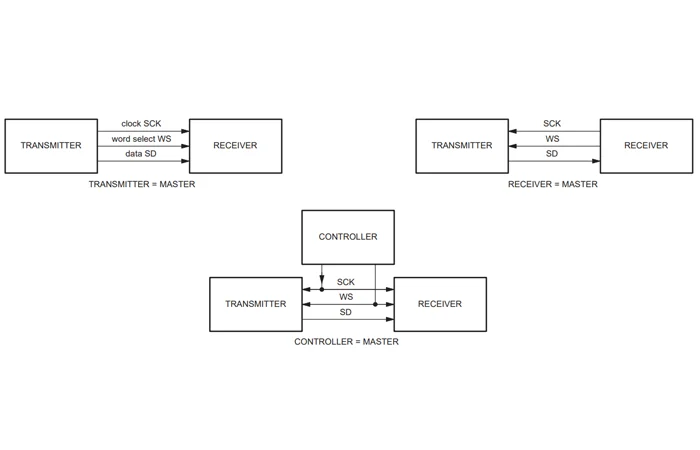

下图描述了 I2S 支持的三种配置。

该图取自I2S 规范,该规范由飞利浦

半导体于 1986 年首次发布,并于 1996 年进行了修订。

数据在SD线上驱动,WS线的状态对应于当前正在传输的音频通道(右或左),时钟线承载串行时钟。如图所示,WS 和 SCK 信号可以由

发送器、

接收器或第三方

控制器组件生成。

下面列出了三个 I2S 信号的显着特征。

串行数据(SD)

数字值首先传输 MSb。

发送器和接收器不需要有商定的字长;发送器发送其拥有的内容,接收器获取其可以使用的内容。

新的数据位可以在时钟的上升沿或下降沿输出。然而,它们必须在上升沿计时,因此这里更直接的方法是下图所示的安排,即我们在下降沿计时数据,并在上升沿计时。

该协议不包括字之间未使用的时钟周期;一个字的 LSb 后面紧接着是下一个字的 MSb。