本文将探讨电压模式R-2R DAC结构。

在本文中,我们将探索什么是R-2R DAC以及如何实现它们。

首先,我们将简要回顾一下开尔文分压器DAC。这种结构很简单,但它们需要大量的电阻和开关来实现高分辨率DAC。这个问题的一个解决方案是称为R-2R DAC的DAC结构。这些结构巧妙地利用梯形网络来实现电阻较少的DAC。

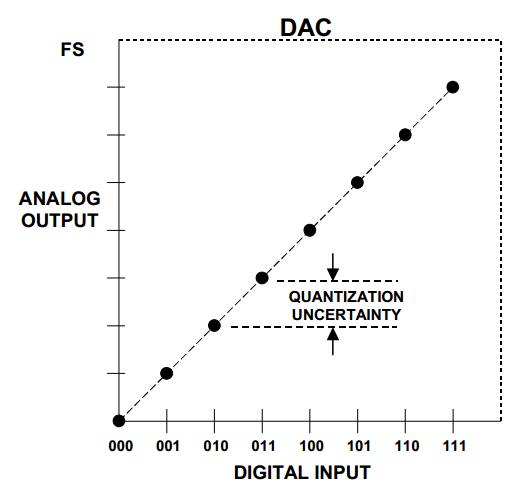

数模转换器(DAC)接收以数字代码表示的数据,并产生等效模拟输出(见下面的图1)。值得一提的是,除了数字输入外,DAC还需要模拟基准电压或电流才能工作。该基准电压源可在DAC芯片内部产生,也可在外部提供。

上述理想传递函数对应于一个三位单极性DAC。请注意,DAC输入和输出都是量化值,传递函数实际上由八个点组成(而不是穿过这八个点的线)。此外,模拟输出(输入代码全为1的输出)比满量程(FS)值低。

产生图1传递函数的基本结构如下图2所示。这种结构称为串式DAC或开尔文分压器,使用八个相等的电阻串联来产生三位DAC的八个不同电压电平。例如,要产生等于 V 的模拟输出裁判/4,我们只需要转动开关SW4 上。

输出缓冲器用于防止电阻串受到DAC输出节点V的任何负载效应代数转换器.

开尔文分频器的一个主要缺点是n位DAC需要2n 电阻器和开关。这就是为什么使用这种方法来构建高分辨率DAC并不容易的原因(尽管可以将开尔文分频器与其他技术结合使用来构建更复杂的DAC)。

然而,有一种有趣的方法,它使用梯形网络来显着减少电阻器的数量。这些结构称为R-2R DAC,将在下一节中讨论。

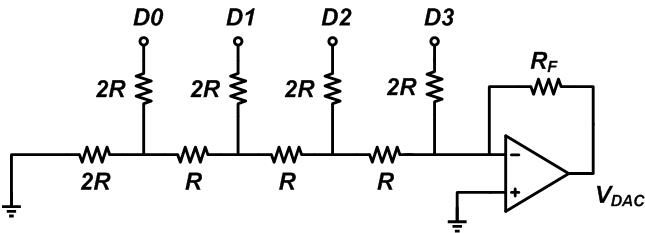

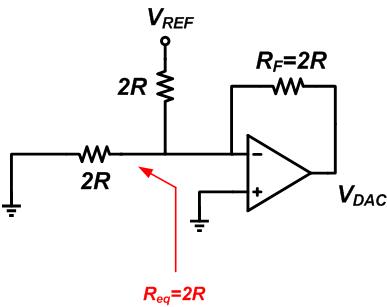

基本的四位R-2R电压模式DAC如图3所示。数字代码应应用于输入 D3...D0,其中 D3 是有效位 (MSb),D0 是有效位 (LSb)。请参考Robert Keim之前的文章以了解更多信息 /有效位/字节和字节序.

如您所见,梯形图中有两种不同的电阻值(R 和 2R)。

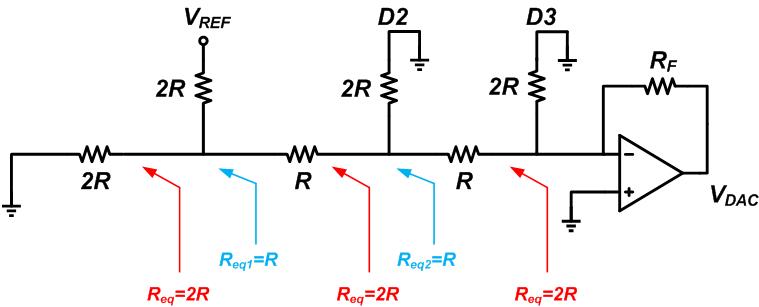

一些观察可以使电路的分析更简单:

请注意,为了计算等效电阻,施加到 D3...D0 的电压源对地短路。

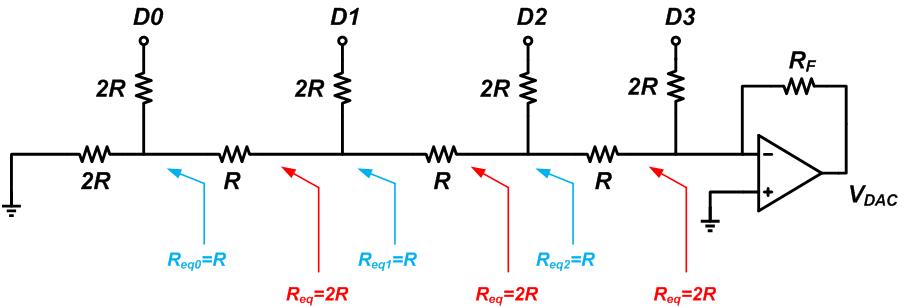

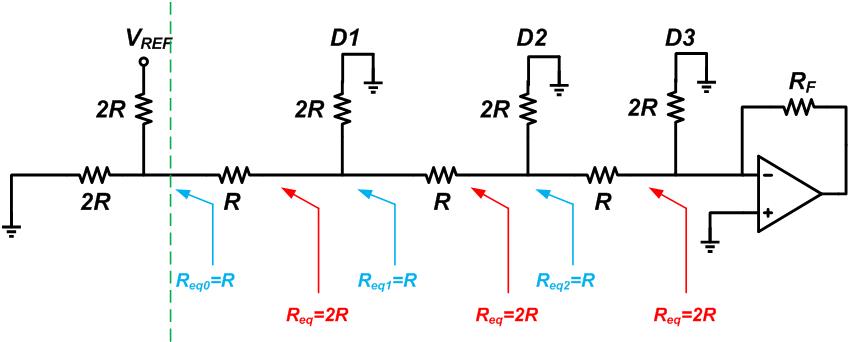

现在让我们检查电路操作。假设 D0 连接到 V REF并且其他位为逻辑低电平;我们得到图5中的电路。

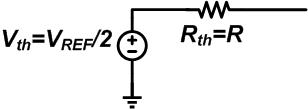

应用戴维宁定理,我们可以对虚线左侧的电路建模,如图 6 所示。

戴维南等效电压为VREF除以2,戴维南等效电阻等于R。

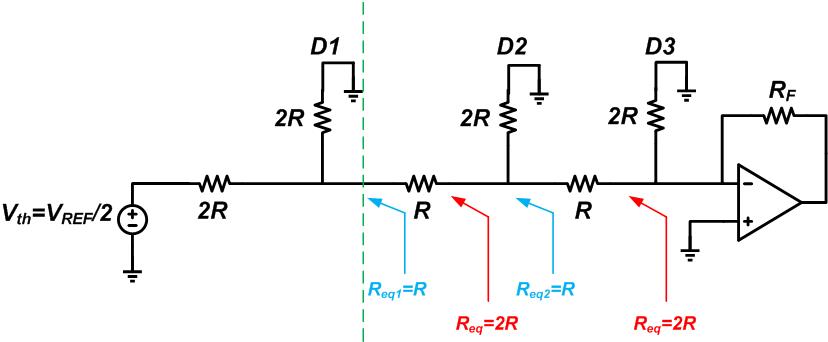

现在,我们使用这个等效电路,得到图 7 中的电路。

如果我们考虑图7中虚线左侧的电路,我们会观察到重复的模式。有两个2R电阻和一个电压源。这部分电路的戴维宁等效值如图8所示。

因此,V裁判 再次降低两倍,等效电阻仍为R。如果我们将此模型连接到电路的其余部分,则先前的模式将再次出现。如图 9 所示。

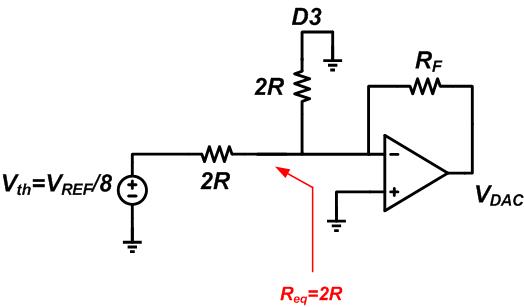

考虑到我们之前的简化,我们可以很容易地在虚线左侧找到电路的戴维宁等效物。戴维宁电压将为V裁判/8,戴维宁电阻将为2R。插入戴维宁等价物,我们得到图 10。

考虑到 虚拟地面 在运算放大器的反相输入端,我们可以看到没有电流流过电阻,导致D3输入接地,因此电流(V裁判/8)/2R 将流过反馈电阻 (RF).假设 RF=2R,输出电压将为 VDAC = -2R ? (V裁判/8)/2R = -V裁判/8.该输出电压对应于DAC LSB。

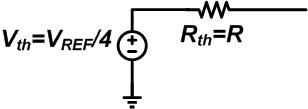

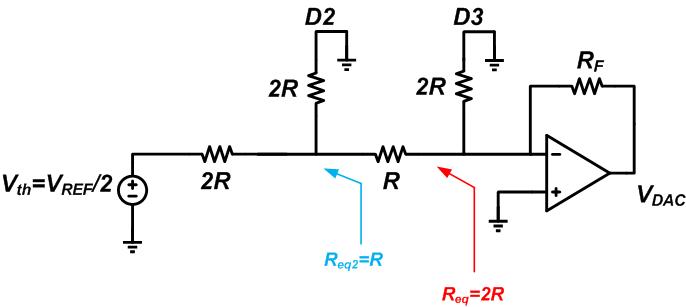

现在,让我们检查其他数字输入组合。假设 D1 连接到 V裁判 其他位逻辑低电平。考虑到我们的个观察结果,我们可以对电路进行建模,如图11所示。

应用戴维宁定理,我们得到以下原理图。

这与图 9 相同,只是输入为 V裁判/2 而不是 V裁判/4.考虑D的结果3D2D1D0 = 0001,如果 RF = 2R 我们得到 V代数转换器 = -V裁判/4.

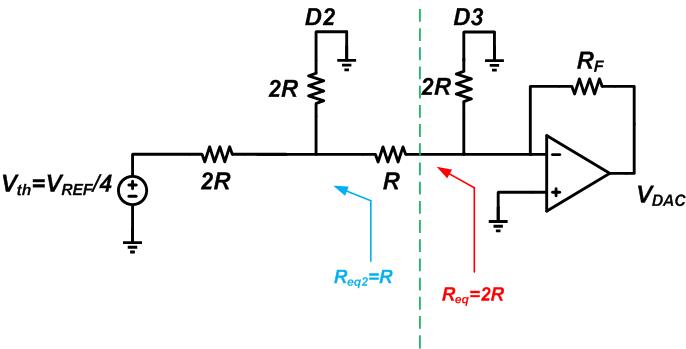

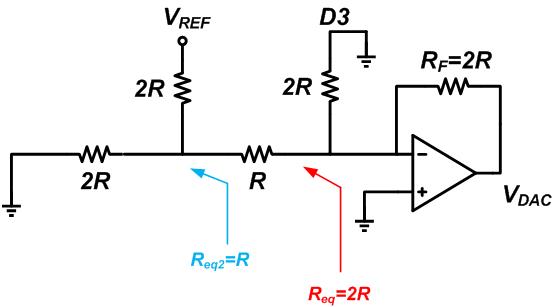

如果 D2 连接到 V裁判 其他三位逻辑低电平,我们得到图13中的模型。

应用戴维宁定理,我们得到图14中的电路。

考虑到运算放大器反相输入端的虚地,电流 (V REF /2)/2R 应该流过反馈电阻。因此,我们有:V DAC = -V REF /2。

为了检查 MSB,我们假设 D3 连接到 V REF(逻辑高电平),其他三位接地(逻辑低电平)。在这种情况下,我们获得图 15 中的模型。

因此,输出电压将为 V DAC = -(V REF /2R)?2R = -V REF。

总而言之,连接输入 D3, D2, D1和 D0 到 V裁判 可分别产生-V的电压步长裁判, -V裁判/2, -V裁判/4 和 -V裁判/8.这些电压阶跃是执行数模转换时所需的基准电压的二进制加权分数。由于电路是线性的,输入的组合将产生相应的输出电压阶跃的相同组合。例如,如果 D0 和 D1 连接到 V裁判 和 D2 和 D3 逻辑低电平,输出将为-V裁判/8 -V裁判/4 = -3V裁判/8.注意反馈电阻,RF,直接影响DAC的增益。

R-2R梯形网络中的电阻连接永远不会被开关断开(如开尔文分压器)。该设计使得无论对DAC施加何种数字代码,运算放大器的反相端始终具有恒定的等效电阻。换句话说,梯形网络的输出阻抗是恒定的。这使得放大器或单位增益缓冲器的稳定更加容易。

但是,基准电压源观察到梯形图网络的负载阻抗变化。因此,参考发生器应该能够产生适用于宽负载电阻范围的电压。

如果与理想元件值的偏差相对较大,则R-2R DAC的输入至输出响应可以是非单调的。单调DAC响应要么完全不增加,要么完全不减少。例如,开尔文分频器的输入-输出特性是单调的。如果我们增加输入数字代码,输出模拟电压将增加或(在坏的情况下)保持其值;它不会减少。因此,组件不匹配不会导致非单调响应。

R-2R DAC的情况并非如此。采用图4的结构,模拟输出应随着输入代码的增加而减小。但是,假设由于电阻值不匹配,对应于MSB的输出电压阶跃为-3?V裁判/4而不是理想值 -V裁判.如果输入代码从 0111 更改为 1000,则输出将从 -V裁判/2 - V裁判/4 - V裁判/8 = -7?V裁判/8 至 -3?V裁判/4.

因此,如果我们有不匹配,输入代码的增加会导致模拟输出电压的增加,因此输入到输出的响应可以是非单调的!请注意,某些应用需要在闭环系统中使用DAC。在这些情况下,非单调DAC响应可能会改变 负面反馈 到积极的反馈。这就是为什么单调性可能很重要,具体取决于应用。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。