也许极低值电阻器(即毫欧 (mΩ) 及以下)常见的应用是电流控制电路,它们的低值可减少功率损耗。对于这些应用,大约 10%-20% 的公差就足够了。但即使在这些公差下,准确测量非常低的电阻值也可能相当困难,尤其是在涉及大电流时。

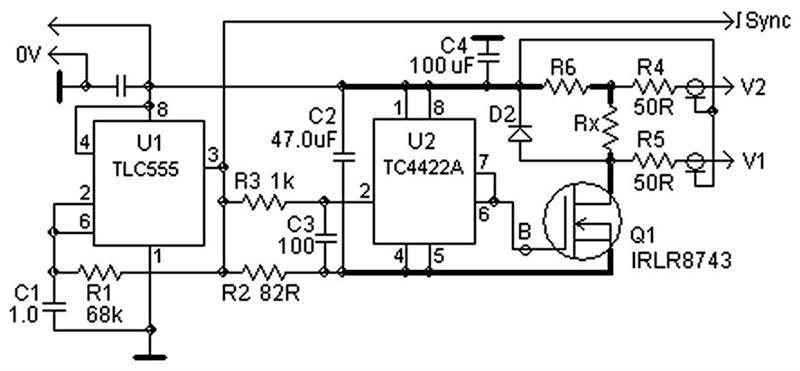

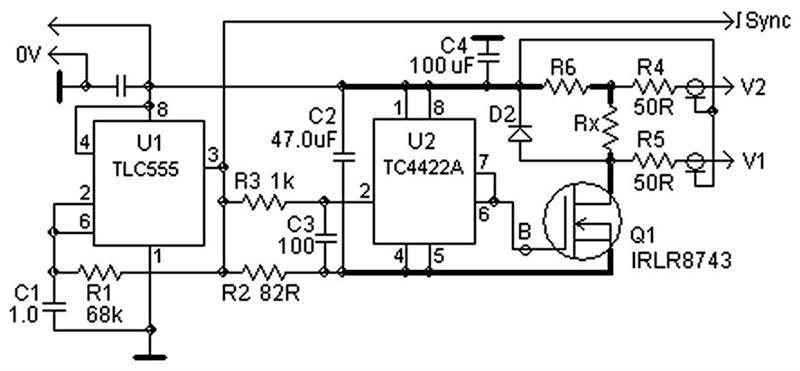

图 1所示的电路通过向未知电阻器和已知值的参考电阻器施加低占空比脉冲来解决该问题。比例技术用于比较两个组件的响应并确定被测电阻器的值。

图 1所示电路通过向未知电阻器和已知值的参考电阻器施加低占空比脉冲,实现了对极低电阻值的测量。

可以使用普通示波器或脉冲峰值电压表从输出 V1 和 V2 获得计算准确电阻值所需的测量值,后者可提供更高的精度。

用您独特的设计让工程界惊叹不已: 设计创意提交指南

该电路使用久负盛名的 555 定时器,在不稳定模式下运行以产生用于对低电感电容器 C2 充电和放电的脉冲。在放电周期中,电流通过精密标准电阻 (R6) 和被测电阻 (Rx)。电阻值可以根据相应电压的比值计算得出:

V1 / V2 = (Rx + R6) / R6 = Rx / R6 + 1,

其中 V1 和 V2 是峰值。

因此,未知值:

Rx = (V1 / V2 – 1) * R6

示波器/电压表的带宽应该足够大以捕获电路产生的短脉冲。由于 555 振荡器的半周期与脉冲持续时间的比率非常大,某些示波器无法确保足够的亮度。

该电路还可用于驱动其他需要大振幅、短持续时间电流脉冲的低电阻负载,例如

半导体激光器。

测试电路细节 脉冲同步(U1,引脚 3)有助于更早同步示波器;同步和输出脉冲之间的延迟可能允许示波器捕获脉冲的前端,因为某些示波器的 Y 通道中可能没有延迟线,使得非常陡峭的前端无法显示。该延迟由时间常数 R3 * C3 决定。C3 的值可能在 20 – 500pF 的范围内(甚至更多),具体取决于所使用的时基和示波器本身。

MOSFET 驱动器 U2 (TC4422A) 用于确保 Q1 的高栅极充电电流和快速导通时间,这对于测量至关重要。

MOSFET (Q1) 具有非常低的RDSOn(低于 3Ω),以确保干净的高振幅脉冲。快速二极管 D2 限制 Q1 的过压。注意:这部分电路中出现的大电流需要特别注意元器件选择和 PCB 布局。有关详细信息,请参阅下面的组件选择说明和设计说明部分。

该电路的短而强大的电流脉冲还在频域中产生广谱响应。因此,必须特别注意尽量减少寄生电感和电容负载,否则电路将显示高水平的电抗,并在布局的各个部分产生振荡。您需要了解的有关如何化这些不需要的寄生效应的实用细节记录在本文的设计说明部分。

元器件选择注意事项

强烈推荐在电路中使用 SMD 组件。一些电容器,即使是基于薄膜的结构,在受到尖锐的高电流脉冲时,其介电层也会经历压电运动,类似于 C2 所暴露的那些。有时您甚至可以从此类电容器中听到非常明显的“滴答声”,这意味着由于压电效应导致的高损耗。在这种情况下,“ticks”级别较低的组件可以被视为更好的组件。

来自 TT Electronics 的 0.005 Ω (5 mΩ)、容差为 1% 的 LOB-3

精密电阻用作标准电阻 (R6)。

由于电路采用比例测量技术,大多数元件的公差不是很关键,但应特别注意它们的稳定性和结构方式。例如,电容器 C2 的值并不重要,但它应该足够大以提供足够长的电流脉冲,很容易被示波器或电压表注意到。

该电容器应使用具有低内阻/电感的构造技术,例如叠箔膜或陶瓷。您应该避免使用许多类型的电容器,尤其是

陶瓷电容器,如果它们的电容取决于所施加的电压。如有必要,可以并联几个电容器以产生所需的值。

对于 MOSFET,具有极低 RDSon 的好例子是 TI 的CSD16321Q5或 IR 的 IRLx8743。但是,此类器件通常具有相对较低的漏源和栅源击穿电压(CSD16321Q5 仅为 8 V)——您在进行任何修改时都应考虑到这一潜在弱点。

另一个潜在的限制是 MOSFET 的漏极电流。这两个参数都会影响测试电路的测量下限。

为降低寄生振荡水平,电阻器 R6 和电容器 C4 的电感应该非常低——组件本身以及它们所连接的 PCB 走线。

设计说明

R6 和 C4 周围的 PCB 走线必须保持较短并进行布局,以地减少寄生电抗,寄生电抗会导致电流脉冲激发的局部谐振。如果电路布局不符合此要求,则很容易超过 MOSFET Q1 的额定电压。例如,对于 6nF(栅极电容)的容性负载,驱动器 TC4422A 的输出上升/下降时间可以小于 25ns;事实上,连同通过电感的大电流 (~100 A) 会产生几乎会损坏任何 MOSFET 的电压。

请参阅示意图以查看以粗体突出显示的走线 - 这些走线必须足够宽以承载高电流并保持尽可能短以地减少寄生电感。这对于将栅极连接到驱动器(U2,引脚 6 到 Q1 基极)的走线尤为重要,该走线应保持在一英寸以内。此走线 (B) 上的铁氧体

磁珠有助于抑制不需要的振荡。

出于同样的原因,电阻 Rx 和 R6 的连接应尽可能接近相同的长度。它们还应尽可能短,以限度地减少电感和电压降。

电路的所有外部连接都应使用基本的高频实践进行设计。例如,必须使用两端阻抗匹配良好的 50 Ω 同轴

电缆