1、引言

随着雷达技术的发展,线性调频信号已经广泛应用于高分辨率雷达领域。过去获得线性调频信号主要借助模拟方法,其中包括VCO方法和声表面波方法。这两种脉冲电压信号的产生方法因其一些固有的缺陷(如对环境温度比较敏感、信号波形比较单一、信号产生的重复性差、线性度及信号间的相关性不理想等)而制约了雷达整机性能的提高。目前,VCO方法和声表面波方法已渐渐被数字方法所取代。直接数字频率合成方法具有传统方法所不具备的许多突出优点,如频率分辨率和切换速度高,频率切换时相位可保持连续,超宽的频率范围,能实现各种调制波和任意波形的产生以及易于实现全数字化设计等。然而,其全数字化的工作原理也给它带来了两个缺点,一是输出杂散较大,二是输出带宽将受到限制。但是,这一缺陷随着新工艺和新算法的出现正在逐渐得到改善。

AD9858是AD公司于2003年推出的一款高性能DDS芯片,其工作频率高达1GHz,杂散性能指标更高于以前的产品。AD9858凭借优良的性能可广泛应用于甚高频/超高频本振合成器、雷达、蜂窝基站跳频合成器等许多领域。

2、AD9858的主要特点

AD9858的工作频率可达1GHz,由于该芯片在时钟输入端提供有二分频器,因而其外部时钟可达2GHz。AD9858内部集成有10位数模转换器,其频率分辨率(即频率累加器位数)为32位,可输出高达400MHz的信号。而其内部集成的可编程快锁充电泵(charge pump)和鉴频器(phase frequency detector)使其非常适合于高速DDS和锁相环结合应用的场合;同时,它还提供有模拟混频器,可适用DDS、PLL和混频器相结合的应用场合。此外,AD9858的杂散抑制性能和谐波抑制性能也非常突出,当输出40MHz信号时,±1MHz带宽内的数模转换SFDR为-87dBc,输出180MHz信号时,±1MHz带宽内的数模转换SFDR为-84dBc。

AD9858作为一个可编程DDS器件,其配置相对比较简单,频率调节字和控制字可以以并行方式或串行方式写入。将数据写入控制与工作有关的寄存器中就可以配置AD9858了。当AD9858工作于点频模式时,有四个用户定义的频率可以通过一对外部引脚来选择,这四个频率允许用户写入四个不同的频率调节字和相位偏移字,从而获得不同的频率和相位偏移。AD9858还可以配置为扫频模式。为了节省功耗,可以通过编程使其进入全休眠状态。

3、AD9858的配置

3.1 扫频工作模式的配置

AD9858有两种工作模式,单一点频模式和扫频模式。单一点频模式的配置比较简单,只需将控制寄存器(CFR)(注:与扫频模式的配置类似,不同点在于将扫频使能位置0)和频率调节字(FTW)配置完毕,即可打开该功能。下面介绍扫频工作模式的配置方法。扫频模式需要配置的寄存器有控制寄存器(CFR)、频率调节字(FTW)、步进频率调节字(DFTW)、步进频率斜率控制字(DFRRW)和相位偏移字(POW),其中,控制寄存器有4个字节,地址分别为0x00、0x01、0x02和0x03。由于该设计未用到PLL功能,故与PLL有关的控制字均置为无效。0x01的Bit7为扫频使能位,将其置1可打开扫频功能。

对于线性调频工作状态的实现,还有几点需要说明。由于线性调频信号是有时宽限制的,因此,AD9858具有输出线性调频信号的功能,但是不具有定时的功能,所以需要外部定时器来实现对时宽的控制。AD9858的线性调频工作原理是:先指定频率起始点和步进频率,并使频率以系统时钟的1/8或其整数倍进行累加,但是在没有指定上限的情况下,会一直扫到1/2参考时钟频率处(即奈奎斯特频率),故需做好对上限频率的控制。利用定时器可以实现对上限频率的控制。

3.2 频率调节字的计算

设输出频率为f0,相位累加器的位数为N,参考时钟为fSYSCLK,则频率调节字为?2?:

ftw=?f0×2N/fSYSCLK

3.3 步进频率调节字的计算

设fF为终止频率,fS为起始频率,DFRRW为步进频率斜率调节字,T为线性调频信号时宽,则步进频率控制字为3

DFTW=(|fF-fs|/fSYSCLK2)?DRRRW/T?×232

4、硬件结构

本设计利用AD9858上集成的锁相环来将60MHz的时钟信号倍频到960MHz,以便使其作为DDS的工作参考时钟,配置芯片选用Xilinx公司生产的CPLD芯片XC95144XL来完成。其电路的硬件结构如图2所示。

使用XC95144XL时,可按照AD9858数据手册上提供的时序来对图中所示的端口进行操作,以便完成对AD9858的配置。用60MHz时钟输入到PFD端口可作为鉴频器的输入,VCO的输出经功分器后,一路经16分频后从DIV端口输入作为鉴频器的输入,另一路直接从端口REFCLK输入以作为DDS的参考时钟。端口CP的输出经环路滤波后可作为VCO的调谐电压。而线性调频信号则从端口IOUT输出,并经带通滤波器和放大器后,作为终所需要的输出。

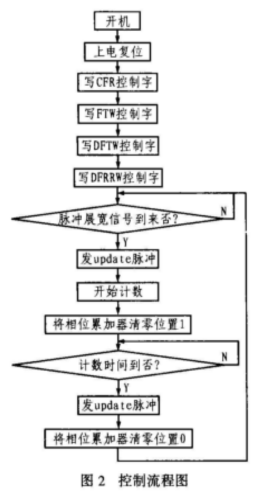

5、控制流程

该设计的配置芯片选用的是Xilinx公司的XC95144XL,控制程序采用VHDL语言编写。设计输出的线性调频信号的起始频率为48MHz,终止频率为72MHz,时宽为20μs,其控制流程如图2所示。在系统接到上电复位信号后,可依次向CFR、FTW、DFTW、DFRRW写控制字,然后等待脉冲展宽信号的到来。脉冲展宽信号为外部激励信号,上升沿有效。当检测到一个上升沿之后,系统将发出一个update信号(update信号的作用是将写入寄存器的数据导入DDS内核,同时使DDS按照新的配置开始工作),同时计数器开始计数并输出宽度为20μs的线性调频信号,同时对地址为0x02的寄存器进行操作,以将Bit3置为高电平,并使相位累加器的清零位有效。计数器计满后会发出一个update信号,由于此时相位累加器清零位有效,此时相位累加器被清零,与此同时停止输出线性调频信号,然后继续对地址为0x02的寄存器进行操作,同时也将Bit3置为低电平,并使相位累加器清零位无效,此时如果接收到update信号,则线性调频信号重新输出。至此,系统将进入等待状态以等待脉冲展宽信号的到来,这样依次往复,即可实现脉冲线性调频信号的输出。

6、结束语

随着数字电子技术的发展,直接数字频率合成得到了日益广泛的应用,DDS技术也日臻完善。传统线性调频信号的产生方法(VCO方法和声表面波方法)由于线性度差、频率稳定度低而逐渐被淘汰。本文介绍了一种采用DDS方式直接产生线性调频信号的全数字设计方法。该方案一方面采用了当今技术为的DDS芯片AD9858,另一方面也根据严格的高速电路设计理论进行了整体规划和布线。经过测试,该方案的各项性能指标均较高,从而证实了其可行性和前瞻性,同时也表明AD9858在相位噪声、杂散抑制度、谐波抑制度等方面确有很好的表现。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。