低压差稳压器(也称为LDO)的使用在许多应用中很常见,因为它们提供了一种简单而廉价的方法来调节必须从较高输入电压降压的输出电压。此外,与开关稳压器相比,线性LDO易于实现并且噪声非常低。

虽然LDO规格简单易懂,但某些应用可能需要更深入地了解关键参数,以确保稳压器适合预期的应用并满足整体电路要求。遗憾的是,数据表并未在所有可能的操作条件下提供所有规格。在这种情况下,设计者必须解释和推断可用信息,以确定在非指定条件下的性能。

此功能要求设计人员对LDO规格和功能有很好的理解。除了这里提供的信息之外,我还建议阅读德州仪器公司Michael Day的“理解低压降(LDO)稳压器”,它提供了对线性LDO稳压器的压差性能的基本了解。它还向您展示了LDO和系统参数如何影响LDO的压差性能及其操作。

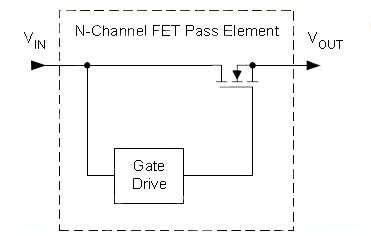

解释从基本规格压差开始,这是稳压器所需的电压。保持监管。例如,具有1 V压降的3.3 V LDO稳压器将需要4.3 V的输入。为了理解LDO上的压降含义,让我们看一下带有传递元件的基本LDO架构。如图1所示,传输元件可以是N或P沟道FET,它提供的电压降是FET导通电阻RDS(on)的函数。

图1:LDO的传输元件可以是N或P沟道FET(由TI提供)。

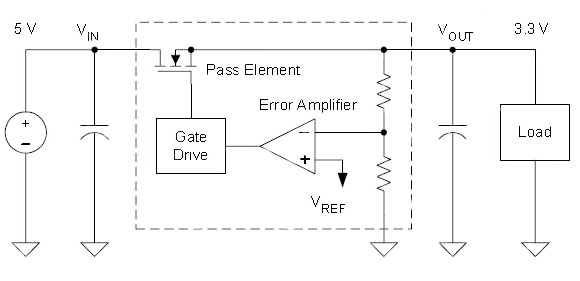

本质上,LDO的行为类似于可变电阻,其电阻值由图2所示的误差放大器控制。通常,如果输入是恒定电源,LDO可以简单地用电阻代替。但是,实际上,输入源永远不会是恒定的,因此需要反馈来改变LDO的有效电阻以维持所需的稳压输出电压。根据输入电压或负载电流,误差放大器驱动通路元件的栅极以保持恒定的输出电压。

图2:基本LDO模块图(由TI提供)。

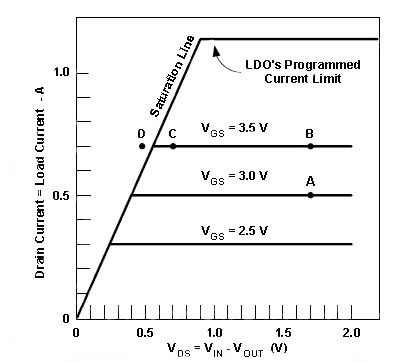

但是,存在基于FET的V-I曲线的限制和边界条件,超过该曲线,LDO将无法按预期执行。如图3所示,x轴是FET的漏源电压VDSM,对于LDO是VIN - VOUT,而y轴表示以安培(A)为单位的传输FET晶体管的漏极电流。使用此曲线,工程师可以确定任何工作电流下的压差。实际上,必须通过输入电压或负载电流的变化来控制传输元件的栅极 - 源极电压,以保持所需的输出调节,如图3所示。

图3:LDO的N沟道传输元件的工作区域(由TI提供)。

辍学通常由制造商指定。例如,采用TI的TPS79330。对于3.0V输出和200mA电流,此LDO规定的压差为200 mV。该LDO的RDS(on)为RDS(on)= 200 mV/200 mA =1Ω。该稳压器的输入电压为3.15 V,在200 mA负载电流下,该器件所需的有效压差必须小于150 mV。

通过将RDS(on)乘以实际负载电流来计算任何其他电流的压差。因此,如果负载电流为170 mA,则此电流下的压差电压将为VDO =1Ωx170 mA = 170 mV。

这仍然不足以确保监管。设计人员必须找到具有170 mA低压差的LDO,以满足所需要求。 TI提供大量LDO供您选择。除了TI之外,其他一些LDO供应商还包括ADI公司,飞兆半导体公司,凌力尔特公司,安森美半导体公司,Microchip技术公司和Maxim Integrated公司等。

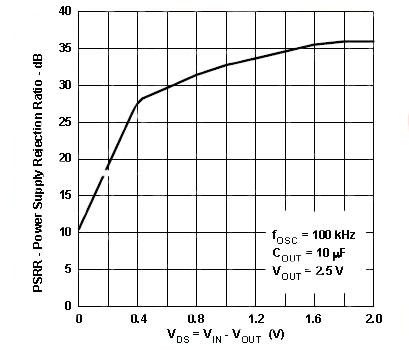

同样,影响LDO性能的其他一些参数包括电源抑制比(PSRR)和输出噪声。 PSRR影响LDO防止输入电压变化引起的输出电压波动的能力。它通常以特定频率的分贝表示。图4显示了LDO输入到输出电压差VDS的典型曲线图,其中VOUT为2.5 V.显示低于0.4 V VDS时,LDO的PSRR开始迅速下降。为了获得良好的输出性能,PSRR必须很高。

图4:LDO电源抑制比(PSRR)与输入到输出的典型曲线图电压差(由TI提供)。

LDO的内部参考电压是潜在的噪声源。该噪声直接馈入前面图2所示的误差放大器。该放大器输出端的噪声调制FET的栅极电压,进一步增加LDO的输出噪声。根据参考文献1中的讨论,设计者必须确定高PSRR和低噪声性能之间的权衡。 TI的TPS799xx系列具有高PSRR和低噪声性能。

正如我们所看到的,设计人员必须了解LDO的各种规格,而不是那些突出显示在数据表上的规格;他或她还必须知道这些规范如何影响整个系统设计。本文讨论了关键参数并展示了样本部分。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。