当今许多应用都要求高速采样模数转换器(ADC)具有12位或以上的分辨率,以便用户能够进行更的系统测量。

然而,更高分辨率也意味着系统对噪声更加敏感。系统分辨率每提高一位,例如从12位提高到13位,系统对噪声的敏感度就会提高一倍。因此,对于ADC设计,设计人员必须考虑一个常常被遗忘的噪声源——系统电源。ADC属于敏感型器件,每个输入(即模拟、时钟和电源输入)均应平等对待,以便如数据手册所述,实现性能。噪声来源众多,形式多样,噪声辐射会影响性能。

当今电子业界的时髦概念是新设计在降低成本的同时还要 “绿色环保”。具体到便携式应用,它要求降低功耗、简化热管理、化电源效率并延长电池使用时间。然而,大多数ADC的数据手册建议使用线性电源,因为其噪声低于开关电源。这在某些情况下可能确实如此,但新的技术发展证明,开关电源可以也用于通信和医疗应用。

这里将介绍对于了解高速ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使ADC实现预期性能,有两种测试十分有用:一般称为电源抑制比 (PSRR)和电源调制比(PSMR)。

模拟电源引脚详解

一般不认为电源引脚是输入,但实际上它确实是输入。它对噪声和失真的敏感度可以像时钟和模拟输入引脚一样敏感。即使进入电源引脚的信号实际上是直流,而且一般不会出现重复性波动,但直流偏置上仍然存在有定量的噪声和失真。导致这种噪声的原因可能是内部因素,也可能是外部因素,结果会影响转换器的性能。

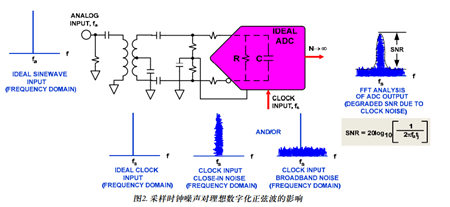

想想经典的应用,其中,转换器采样时钟信号中有噪声或抖动。采样时钟上的抖动可能表现为近载波噪声,并且/或者还可能表现为宽带噪声。这两种噪声都取决于所使用的振荡器和系统时钟电路。即使把理想的模拟输入信号提供给理想的ADC,时钟杂质也会在输出频谱上有所表现,如图2所示。

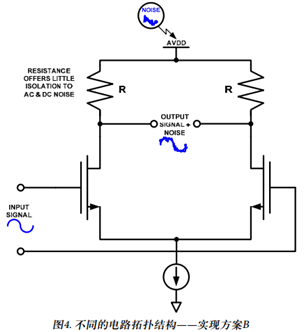

由该图可以推论出是电源引脚。用一个模拟电源引脚 (AVDD)代替图2中的采样时钟输入引脚。相同的原理在此 同样适用,即任何噪声(近载波噪声或宽带噪声)将以这种 卷积方式出现在输出频谱上。然而,有一点不同;可以将 电源引脚视为带一个40 dB至60 dB的衰减器(具体取决于工 艺和电路拓扑结构)的宽带输入引脚。在通用型MOS电路 结构中,任何源极引脚或漏极引脚在本质上都是与信号路 径相隔离的(呈阻性),从而带来大量衰减,栅极引脚或信 号路径则不是这样。假定该设计采用正确的 电路结构类型来使隔离效果达到化。在电源噪声非常明显的情况 下,有些类型(如共源极)可能并不是十分合适,因为电源 是通过阻性元件偏置的,而该阻性元件后来又连接到输出 级,如图3和图4所示。AVDD引脚上的任何调制、噪声等 可能更容易表现出来,从而对局部和/邻近电路造成影响。 这正是需要了解并探索转换器PSRR数据的原因所在。

正如不同实现方式所示,存在寄生R、C和失配造成的不同 频率特性。记住,工艺也在不断变小,随着工艺的变小, 可用带宽就会增加,可用速率也会提升。考虑到这一点, 这意味着更低的电源和更小的阈值。为此,为什么不把电 源节点当作高带宽输入呢,就像采样时钟或模拟输入引脚一样呢?

何谓电源抑制

当供电轨上有噪声时,决定ADC性能的因素主要有三个, 它们是PSRR-dc、PSRR-ac和PSMR。

PSRR-dc指电源电压的 变化与由此产生的ADC增益或失调误差的变化之比值,它可以用有效位(LSB)的分数、百分比或对数dB (PSR = 20 × log10 (PSRR))来表示,通常规定采用直流条件。

但是,这种方法只能揭示ADC的一个额定参数随电源电压 可能会如何变化,因此无法证明转换器的稳定性。

更好的方法是在直流电源之上施加一个交流信号,然后测试电源 抑制性能(PSRR-ac),从而主动通过转换器电路耦合信号 (噪声源)。这种方法本质上是对转换器进行衰减,将其自身表现为杂散(噪声),它会在某一给定幅度升高至转换器噪底以上。其意义是表明在注入噪声和幅度给定的条件下转换器何时会崩溃。同时,这也能让设计人员了解到多大 的电源噪声会影响信号或加入到信号中。

PSMR则以不同的方式影响转换器,它表明当与施加的模拟输入信号进行 调制时,转换器对电源噪声影响的敏感度。这种影响表现 为施加于转换器的IF频率附近的调制,如果电源设计不严 谨,它可能会严重破坏载波边带。

总之,电源噪声应当像转换器的任何其他输入一样进行测 试和处理。用户必须了解系统电源噪声,否则电源噪声会提高转换器噪底,限制整个系统的动态范围。

电源测试

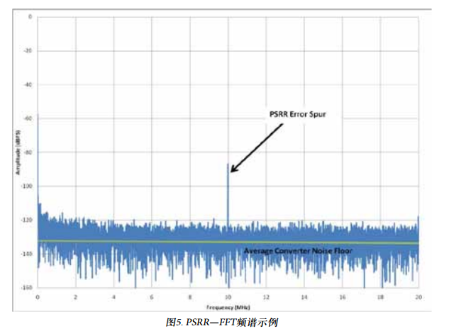

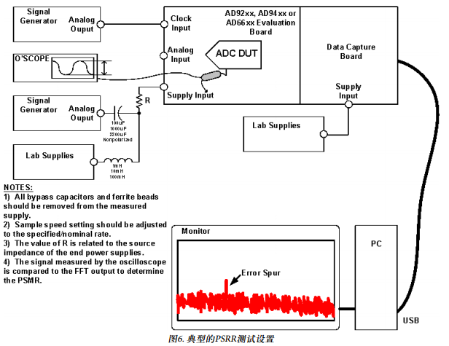

图6所示为在系统板上测量ADC PSRR的设置。分别测量每 个电源,以便更好地了解当一个交流信号施加于待测电源 之上时,ADC的动态特性。开始时使用一个高容值电容,例如100 F非极化电解质电容。电感使用1 mH,充当直流 电源的交流阻塞器,一般将它称为“偏置-T”,可以购买采用连接器式封装的产品。

使用示波器测量交流信号的幅度,将一个示波器探针放在电 源进入待测ADC的电源引脚上。为简化起见,将施加于电 源上的交流信号量定义为一个与转换器输入满量程相关的 值。例如,如果ADC的满量程为2V p-p,则使用200 mV p-p 或–20 dB。接下来让转换器的输入端接地(不施加模拟信号), 查找噪底/FFT频谱中处于测试频率的误差杂散,如图5所 示。若要计算PSRR,只需从FFT频谱上所示的误差杂散值中 减去–20 dB即可。例如,如果误差杂散出现在噪底的–80 dB 处,则PSRR为–80 dB – –20 dB,即–60 dB(PSRR = 误差杂散 (dB) – 示波器测量结果(dB))。–60 dB的值似乎并不大,但如 果换算成电压,它相当于1 mV/V(或10 60/20),这个数字对于 任何转换器数据手册中的PSRR规格而言都并不鲜见下一步是改变交流信号的频率和幅度,以便确定ADC在系 统板中的PSRR特性。数据手册中的大部分数值是典型值, 可能只针对差工作条件或差性能的电源。例如,相对 于其他电源,5 V模拟电源可能是差的。应确保所有电源 的特性都有说明,如果说明得不全面,请咨询厂家。这 样,设计人员将能为每个电源设置适当的设计约束条件。

请记住,使用LC配置测试PSRR/PSMR时有一个缺点。当扫 描目标频段时,为使ADC电源引脚达到所需的输入电平, 波形发生器输出端所需的信号电平可能非常高。这是因为 LC配置会在某一频率(该频率取决于所选的值)形成陷波滤 波器。这会大大增加陷波滤波器处的接地电流,该电流可 能会进入模拟输入端。要解决这一问题,只需在测试频率 造成测量困难时换入新的LC值。这里还应注意,LC网络 在直流条件下也会发生损耗。记住要在ADC的电源引脚上测量直流电源,以便补偿该损耗。例如,5 V电源经过LC网 络后,系统板上可能只有4.8 V。要补偿该损耗,只需升高 电源电压即可。

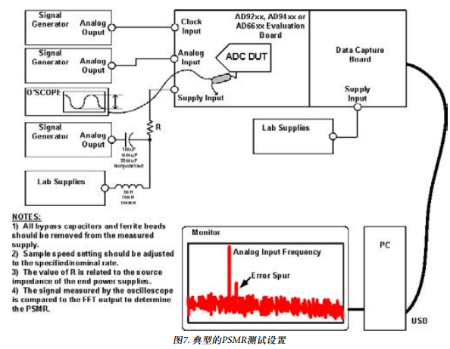

PSMR的测量方式基本上与PSRR相同。不过在测量PSMR 时,需将一个模拟输入频率施加于测试设置,如图7所示。

另一个区别是仅在低频施加调制或误差信号,目的是查看 此信号与施加于转换器的模拟输入频率的混频效应。对于 这种测试,通常使用1 kHz至100 kHz频率。只要能在基频周 围看到误差信号即混频结果,则说明误差信号的幅度可以 保持相对恒定。但也不妨改变所施加的调制误差信号幅 度,以便进行检查,确保此值恒定。为了获得终结果, (差)调制杂散相对于基频的幅度之差将决定PSMR规 格。图8所示为实测PSMR FFT频谱的示例。

电源噪声分析

对于转换器和终的系统而言,必须确保任意给定输入上的噪声不会影响性能。前面已经介绍了PSRR和PSMR及其重要意义,下面将通过一个示例说明如何应用所测得的数值。该示例将有助于设计人员明白,为了了解电源噪声并满足系统设计需求,应当注意哪些方面以及如何正确设计。

首先,选择转换器,然后选择调节器、LDO、开关调节器 等。并非所有调节器都适用。应当查看调节器数据手册中 的噪声和纹波指标,以及开关频率(如果使用开关调节器)。 典型调节器在100 kHz带宽内可能具有10 V rms噪声。假设 该噪声为白噪声,则它在目标频段内相当于31.6 nV rms/√Hz 的噪声密度。

接着检查转换器的电源抑制指标,了解转换器的性能何时 会因为电源噪声而下降。在奈奎斯特区f S /2,大多数 高速转换器的PSRR典型值为60 dB (1 mV/V)。如果数据手册 未给出该值,请按照前述方法进行测量,或者询问厂家。

使用一个2 V p-p满量程输入范围、78 dB SNR和125 MSPS采 样速率的16位ADC,其噪底为11.26 nV rms。任何来源的噪 声都必须低于此值,以防其影响转换器。在奈奎斯特 区,转换器噪声将是89.02 V rms (11.26 nV rms/√Hz) × √ (125 MHz/2)。虽然调节器的噪声(31.6 nv/√Hz)是转换器的 两倍以上,但转换器有60 dB的PSRR,它会将开关调节器的 噪声抑制到31.6 pV/√Hz (31.6 nV/√Hz × 1 mV/V)。这一噪声 比转换器的噪底小得多,因此调节器的噪声不会降低转换器的性能。

电源滤波、接地和布局同样重要。在ADC电源引脚上增加 0.1 F电容可使噪声低于前述计算值。请记住,某些电源引 脚吸取的电流较多,或者比其他电源引脚更敏感。因此应 当慎用去耦电容,但要注意某些电源引脚可能需要额外的 去耦电容。在电源输出端增加一个简单的LC滤波器也有助 于降低噪声。不过,当使用开关调节器时,级联滤波器能 将噪声抑制到更低水平。需要记住的是,每增加增益 就会每10倍频程增加大约20 dB。

需要注意的一点是,这种分析仅针对单个转换器而 言。如果系统涉及到多个转换器或通道,噪声分析将有所 不同。例如,超声系统采用许多ADC通道,这些通道以数 字方式求和来提高动态范围。基本而言,通道数量每增加 一倍,转换器/系统的噪底就会降低3 dB。对于上例,如果 使用两个转换器,转换器的噪底将变为一半( 3 dB);如果 使用四个转换器,噪底将变为 6 dB。之所以如此,是因为 每个转换器可以当作不相关的噪声源来对待。不相关噪声 源彼此之间是独立的,因此可以进行RSS(平方和的平方根) 计算。终,随着通道数量增加,系统的噪底降低,系统 将变得更敏感,对电源的设计约束条件也更严格。

结论

要想消除应用中的所有电源噪声是不可能的。任何系统都 不可能完全不受电源噪声的影响。因此,作为ADC的用 户,设计人员必须在电源设计和布局布线阶段就做好积极 应对。下面是一些有用的提示,可帮助设计人员 地提高PCB对电源变化的抗扰度:

对到达系统板的所有电源轨和总线电压去耦。

记住:每增加增益就会每10倍频程增加大约20 dB。

如果电源引线较长并为特定IC、器件和/或区域供电, 则应再次去耦。

对高频和低频都要去耦。

去耦电容接地前的电源入口点常常使用串联铁氧体磁 珠。对进入系统板的每个电源电压都要这样做,无论它是来自LDO还是来自开关调节器。

对于加入的电容,应使用紧密叠置的电源和接地层(间 距≤4密尔),从而使PCB设计本身具备高频去耦能力。

同任何良好的电路板布局一样,电源应远离敏感的模拟 电路,如ADC的前端级和时钟电路等。

良好的电路分割至关重要,可以将一些元件放在PCB的 背面以增强隔离。

注意接地返回路径,特别是数字侧,确保数字瞬变不会 返回到电路板的模拟部分。某些情况下,分离接地层也 可能有用。

将模拟和数字参考元件保持在各自的层面上。这一常规 做法可增强对噪声和耦合交互作用的隔离。

遵循IC制造商的建议;如果应用笔记或数据手册没有直接 说明,则应研究评估板。这些都是非常好的起步工具。

这篇技术文章旨在清楚说明高速转换器的电源敏感问题, 以及它为何对用户的系统动态范围如此重要。为使系统板 上的ADC实现数据手册所述的性能规格,设计人员应当了解所需的布局布线技术和硬件。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。