亚德诺半导体 ? 2018-07-11 09:21 ? 122次阅读 0

ADC 在任何依赖外部(模拟)世界收集信息进行(数字)处理的系统中都是不可或缺的组成部分。从通信接收机和电子测试测量到航空航天,这些系统在不同的应用中各有不同。。。

硅片处理技术的发展(65 nm CMOS、28 nm CMOS等)使高速 ADC 得以跨越 GSPS(每秒千兆采样)门槛,同时提供12位或14位性能。

对于系统设计人员来说,这意味着能用于数字处理的采样带宽更宽。出于环境和成本方面的考虑,系统设计人员不断尝试降低总功耗。一般而言,ADC 制造商建议采用低噪声 LDO(低压差)稳压器为 GSPS(或 RF 采样)ADC 供电,以便达到性能。然而,这种方式的输电网络 (PDN) 效率不高。设计人员对于使用开关稳压器直接为GSPS ADC 供电且不会大幅降低 ADC 性能的方法呼声渐高。

解决方案是谨慎地进行 PDN 部署和布局布线,确保 ADC 性能不受影响。本文讨论了线性和开关电源的不同之处,并表明 GSPS ADC 与 DC-DC 转换器搭配使用可大幅改善系统能效,且不会影响 ADC 性能。本文通过输电网络组合探讨 GSPS ADC 性能,并对成本和性能进行了对比分析。

通常建议 GSPS ADC 使用的 PDN

高带宽、高采样速率 ADC(或GSPS ADC)可以具有多个电源域(AVDD、DVDD等)。随着尺寸的缩小,不仅电源域增多,为 ADC 供电所需的不同电压数量也有所增加。新近的 GSPS ADC 设计多有 7 个不同域和三种不同电压:1.25 V、2.5 V和3.3 V。

Tips

“......GSPS ADC 与 DC-DC 转换器搭配使用可大幅改善系统能效,且不会影响 ADC 性能。”

这些电源域和各种电压的日益普及是在这些采样速率下工作所必需的。它们可以确保各种电路域(采样、时钟、数字、串行器等)之间具有正确的隔离,同时使性能。正是因为这个原因,ADC 制造商才设计了评估板,并推荐详细的电源设计方案,确保降低风险,使性能化。

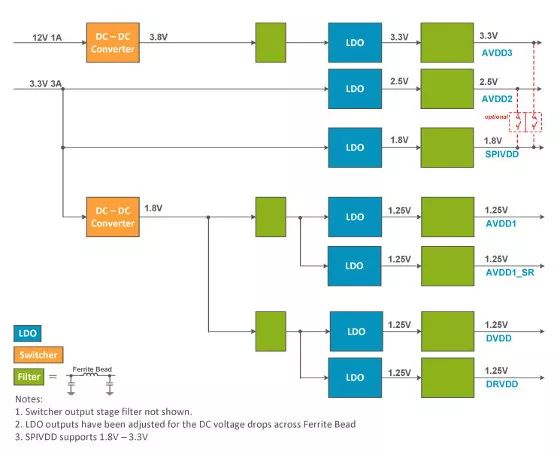

例如,图 1 显示了一个 GSPS ADC 评估板使用的默 认PDN 的功能框图。根据 Vita57.1 规格,电源输入来自 FMC(FPGA夹层卡)连接器供应的 12 V/1 A 和 3.3 V/3 A 电源。DC-DC 转换器用于使电压下降到可控水平,以便 LDO 能够在不进入热关断的情况下进行稳压操作。

图1:GSPS评估板使用的PDN

显而易见,这是一种昂贵的解决方案,有 7 个 LDO 稳压器,每个域一个。这款 PDN 也许是性能的,但肯定不是性价比的。系统设计人员认为部署含有多个 GSPS ADC 的系统非常有难度。

DC–DC 转换器驱动电源

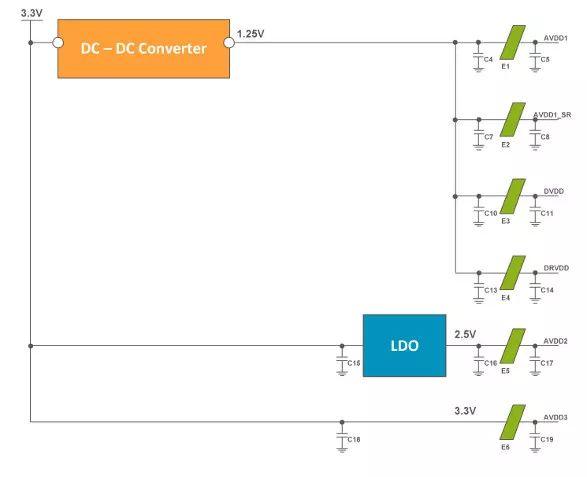

通过移除为 1.25 V 域供电的单个 LDO,还可进一步简化 PDN。这是效、性价比的解决方案。这种方案的困难之处在于确保 DC-DC 转换器的操作稳定性,从而不影响 ADC 性能。单个 DC–DC 转换器驱动 GSPS ADC 所有 1.25 V 域的 PDN 如图 2 所示。

图2:使用DC-DC转换器为AD9680供电

比较不同的 PDN

对上面讨论的两个 PDN 进行了测试。图 3 显示了使用图 1 和图 2 所示 PDN 时的 SNR 性能比较。各奈奎斯特区使用数据手册推荐的设置。

图3:图1和图2所示PDN的性能比较

仅使用 DC-DC 转换器为 GSPS ADC 的 1.25 V 域供电的 PDN 在各种输入频率下显示出了良好的性能。这证明了可以组合域,并在不损失大量 ADC 性能的情况下以高效率、高性价比的方式为它们供电。

开关杂散

除了噪声性能,由于采用了开关元件和磁性元件,因此还应当检查 DC-DC 转换器部署的杂散成分。此时,采用谨慎仔细的布局技术以降低接地环路和接地反弹将会是有好处的。有许多资源可帮助测量开关电源噪声。边带杂散出现基波的一侧,偏移频率为开关频率(本例中为 1.2 MHz)。DC-DC 转换器输出端的滤波器有助于降低输出FFT中表现出来的开关杂散,如图 4 所示,其中输入频率为 170 MHz。

图4:170 MHz输入时的1.2 MHz边带开关杂散

杂散水平 = -105 dBFS

通过了解PSRR(电源抑制比)或ADC的电源域,可估算边带杂散水平。

结论

RF 采样(或GSPS)ADC 可对宽带宽进行数字化处理,在系统设计方面具有独特的优势。针对这些GSPS ADC,业界正在力求降低电源设计的复杂度、尺寸和成本。DC–DC 转换器实现的低噪声、高性价比 PDN 能够为 GSPS ADC 供电,同时对性能无任何影响。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。