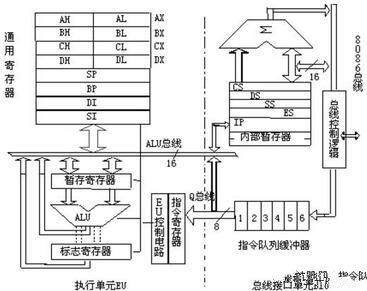

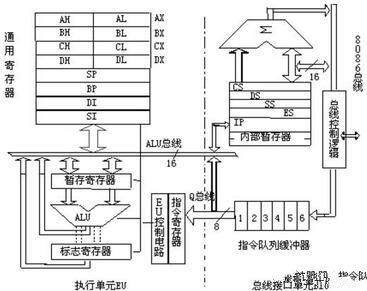

8086CPU内部结构之

总线接口部件BIU

主要功能:20位地址加法器产生20位地址加法器产生20位的物理地址、预取指令并存入先进先出的指令队列

缓冲器中、从

内存和I/O接口读/写操作数、发出各种总线控制信号等。

组成部件:

1)4个16位段寄存器

数据段寄存器(Data Segment,DS)

代码段寄存器(Code Segment,CS)

附加段寄存器(Extra Segment,ES)

堆栈段寄存器(Stack Segment,SS)

2)16位指令指针IP(Instruction Pointer):专用于存放下一条将要执行的指令的偏移地址。

3)20位地址加法器:它能够将逻辑地址变换成读/写

存储器所需要的20位物理地址的加法操作。

4)6字节指令队列缓冲器,用于预存放6字节的指令代码。

5)总线控制电路,用于控制总线的开放、关闭及信号的传送方向。

工作过程:

首先,代码段寄存器CS中的16位段基地址左移4位,并且低4位补4个0,加上16位指令地址IP的值,产生20位物理地址(实际地址),这在20位地址加法器内完成,将20位物理地址存入地址寄存器,并由地址寄存器输出端连接到CPU的地址总线,然后,通过总线控制逻辑发出存储器读信号,从20位物理地址指定的存储单元中取出指令,送到指令缓冲队列中等待执行。

一般情况下,COU从内存取出指令并填满6字节指令队列缓冲器后,EU可从指令队列中取出指令执行。EU从指令队列输出端取出指令后,BIU则自动调整指令队列输出端的指针。当指令队列中有2个或2个以上的字节空出时,BIU将从内存按代码的顺序自动取出后续的代码填入指令队列中。当指令队列已装满,EU没有向BIU申请读/写存储器及I/O端口的操作数时,则BIU不会执行任何总线操作,处于一种空闲状态。

EU从指令队列取出指令并译码后,如果需要从存储器或I/O端口读/写操作数时,EU便向BIU传递偏移地址,BIU只要收到EU送来的偏移地址,就将通过地址加法器将现行数据段及送来的偏移地址组成20位的物理地址,根据得到的20位物理地址,通过执行存储器的读/写总线周期来完成对存储器的读/写操作,或者通过执行I/O端口的读/写总线周期来完成度/写I/O接口的操作。

指令指针寄存器IP有自动加1的功能,它指向下一条指令在当前代码段内的偏移地址。当EU执行跳转指令时,总线接口部件BIU则清除指令队列,根据转移指令的新地址取出指令代码,立即送给EU执行,并且从后继指令序列中取指令,依次填满指令队列。

8086CPU内部结构图: