化功耗的挑战

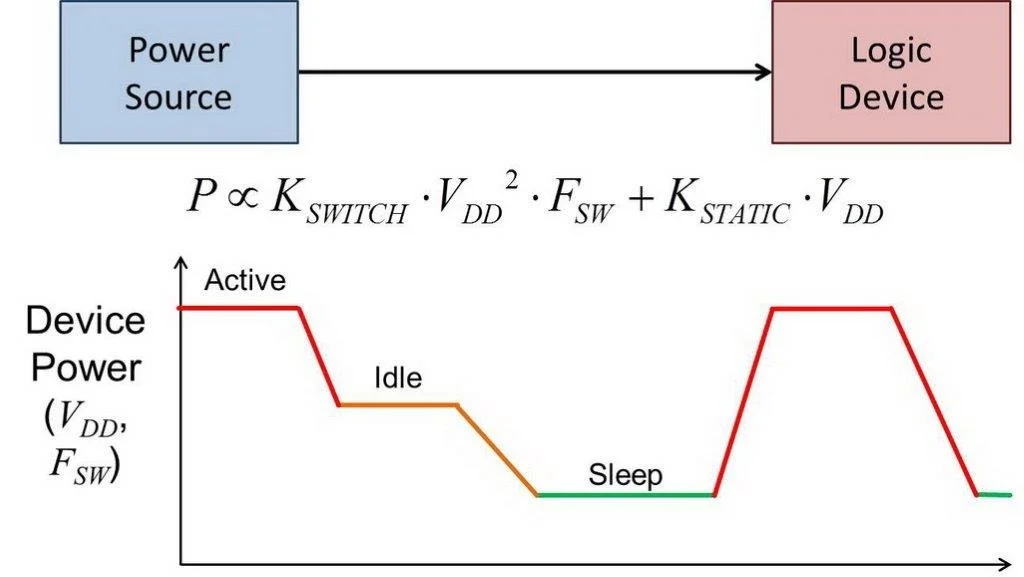

多年来,通过减小 CMOS 特征尺寸并在较低电压下运行,可以限度地降低功耗。然而,随着特征尺寸的减小,由于切换

晶体管的电容而节省的功耗与断态漏电流相匹配。现在,为了限度地降低功耗,处理器或其他大型数字设备(例如大型 ASIC 或 FPGA)必须在低功耗空闲或睡眠模式与高性能模式之间快速切换。在低功耗模式下,器件必须限度地降低其工作电压以减少泄漏损耗,并限度地降低时钟频率以限度地降低

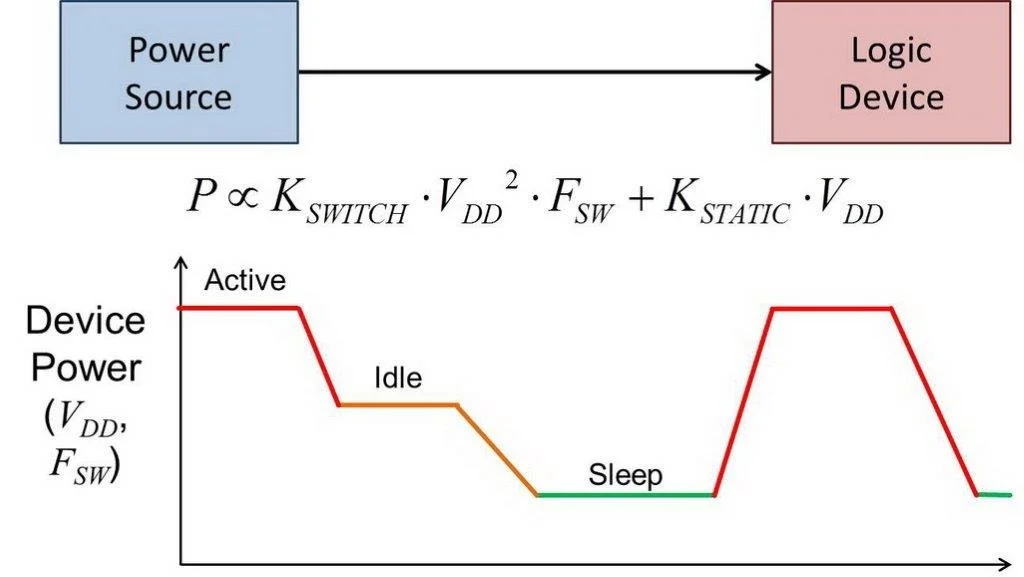

开关损耗。当需要高性能模式时,电源电压必须尽可能快地斜坡上升到支持更高时钟速度所需的更高电压,然后必须提高时钟频率。这种优化功耗的方法称为动态电压和频率调节 (DVFS),如图 1 所示。

几年前,英特尔在其高性能处理器中实现了这一点。处理器通过专有的高速串行总线(“串行 VID”)与其电源进行通信。其他制造商只能自行设计实施 DVFS 的方法。

2012 年,德州仪器 (TI) 的 Juan Arango 和 Travis Summerlin 开发了一种称为 AVSBus(自适应电压总线)的 DVFS 协议。 2013 年 1 月,TI 向拥有并管理 SMBus 和 PMBus 标准的系统管理接口论坛 (SMIF) 提供了该 AVSBus 协议,作为PMBus的扩展。 SMIF 接受了 PMBus 规范工作组的进一步开发,AVSBus 于 2014 年 3 月作为 PMBus 标准修订版 1.3 的一部分发布。它现在可用于任何 PMBus

适配器,这是一种非专有高速总线,用于控制电源转换器并在任何数字 IC 中实施 DVFS。

在不牺牲速度的情况下降低功耗

为了使 DVFS 有效,电源转换器必须非常快速地改变其输出电压,如数字 IC 负载所示。对于以 GHz 为单位运行的时钟频率的数字设备来说,需要数百甚至数十毫秒响应的电源转换器将被视为极其缓慢。当转换到低功耗模式时,数字设备必须立即降低其时钟频率,因为它不知道电源电压何时会降低。

如果电源电压的转换时间很长(意味着甚至数百微秒),那么就会浪费电力。当数字设备需要返回高功率、高性能模式时,必须等到电源电压达到所需的更高水平后才能提高时钟频率。这种延迟会降低性能。

当电源管理方案在毫秒级的时间尺度上在节能和性能模式之间切换时,必须化电源转换延迟,以获得节能和性能的组合。

通过 DVFS 节省能源

图 1:通过 DVFS 节能

使用 AVSBus 解决延迟问题

从数字设备发出改变电压的命令到电压达到新的期望值之间的延迟由三个因素组成:

从数字设备到电源转换器的通信延迟,

功率转换器处理命令并将控制信号(例如占空比)更改为功率级所需的时间,以及

功率级响应所需的时间

至于功率级响应所需的时间,正在通过努力驱动更高的开关来解决。这减小了输出

滤波电感器的尺寸,并允许在给定输入和输出电压下更快地转换输出电流。

其他两个因素(通信延迟和命令处理时间)由 AVSBus 解决。

虽然使用现有的 PMBus 协议将 DVFS 命令从数字设备传送到其电源转换器会很好,但速度太慢了。在 100 kHz 的典型 PMBus 速度下,仅发送命令就需要大约 360 ?s。 PMBus 协议旨在适用于各种设备,但也没有针对纳秒级处理命令进行优化。即使总线速度提高到 1 MHZ(PMBus 1.3 标准允许的值),传输电压命令的 36 ?s 对于数字设备标准来说仍然非常慢。

AVSBus 通过两种方式解决通信延迟问题:50 MHz 的总线速度和固定的 32 位帧。以总线速度运行时,改变电压的命令现在可以在 640 ns 内从数字设备发送到其电源转换器。通过使用标准的类似 SPI 的物理层 (PHY),可以保持较低的接口成本。目前,这确实将 AVSBus 限制为数字设备与其电源转换器之间的点对点通信,但如下所述,这并不是一个重大限制。

AVSBus 通过使用针对该应用进行优化的简单、高效的命令集来解决处理延迟问题。这意味着需要少的逻辑来解码接收到的命令并生成功率级所需的控制信号。凭借良好的设计和电源控制器IC适中的时钟速度,命令处理可以在数十纳秒内完成。

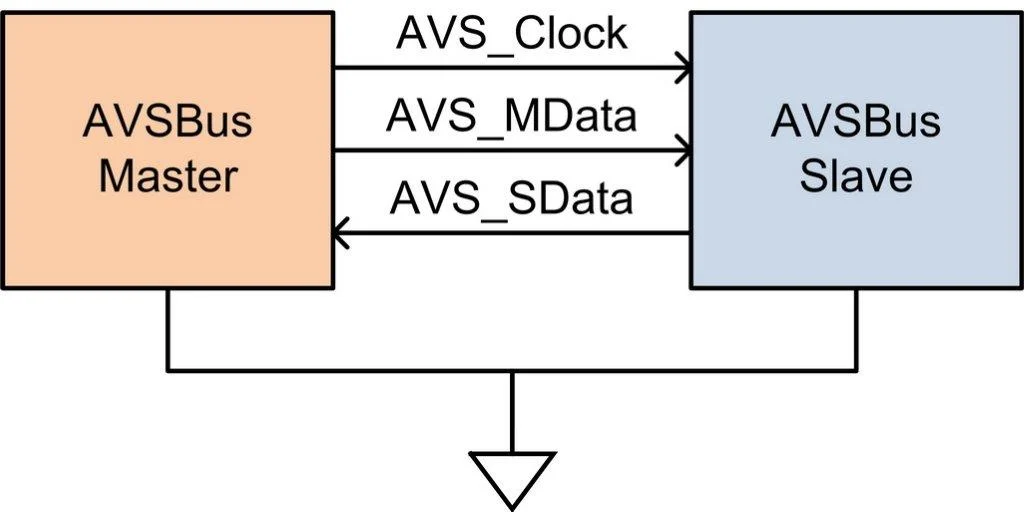

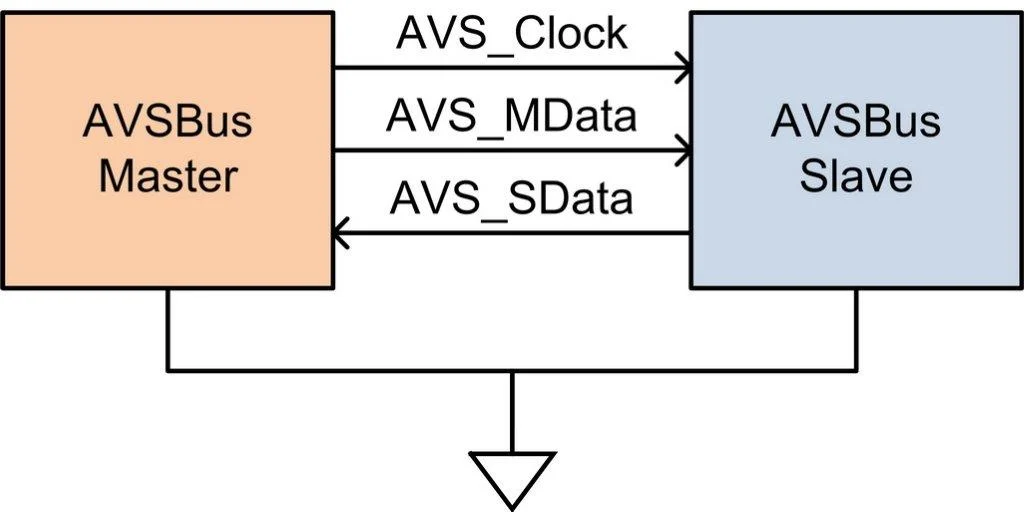

AVSBus 信号和系统

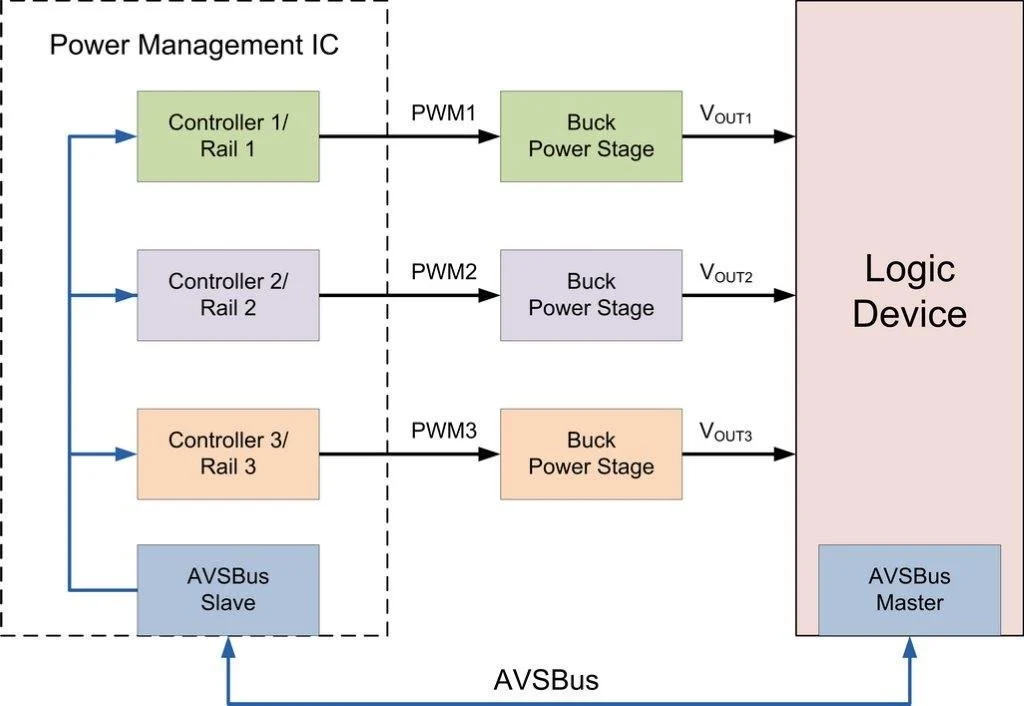

如上所述,AVSBus 的 PHY 基于业界现成的标准 SPI I/O 端口。 AVSBus 的实现需要两个信号:由 AVSBus 主设备生成的 AVS_Clock 和用于将数据从 AVSBus 主设备(数字设备)发送到 AVSBus 从设备(电源转换器)的 AVS_MData。如果应用程序要求 AVSBus 主设备能够从 AVSBus 从设备接收状态信息,则添加可选的第三个信号 AVS_SData。连接如图 2 所示。

AVS总线连接

图 2:AVSB 总线连接

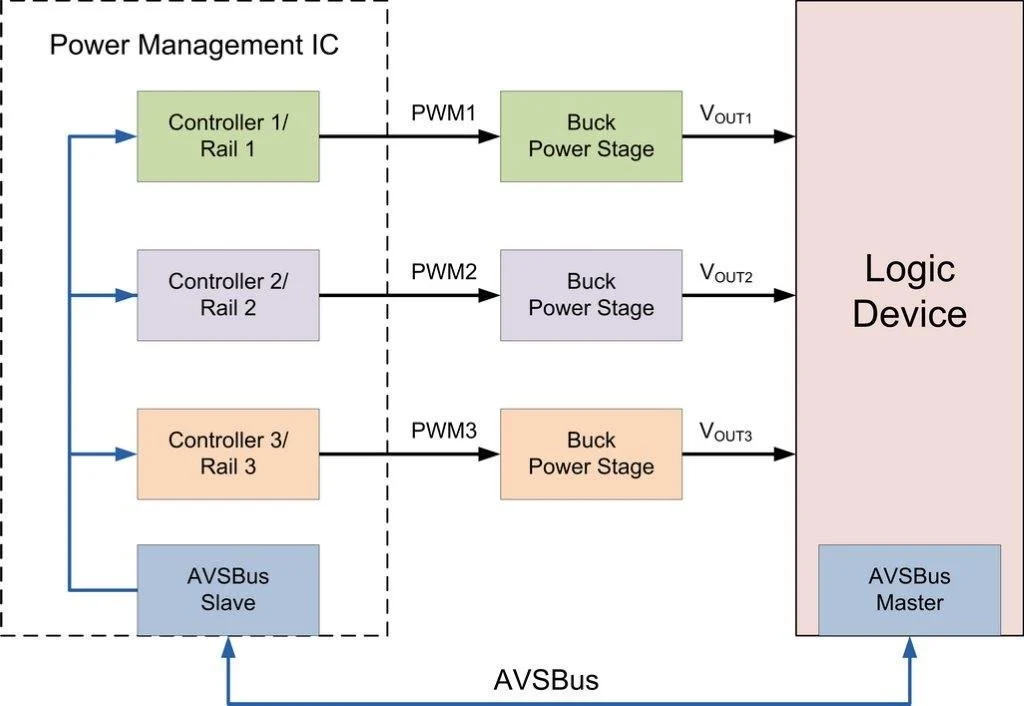

对于需要控制多个轨道的数字设备,有两种选择。个是拥有与需要控制的电源轨一样多的 AVSBus 端口。我们认为方案是单个 AVSBus 与具有多个电源控制器的电源管理 IC (PMIC) 进行通信,如图 3 所示。AVSBus 规范规定可在一个 AVSBus 上寻址多 15 个独立电源轨。

在多轨系统中,AVSBus 规范提供了调度命令执行的灵活性。 AVSBus 命令可以发送到由 PMIC 控制的电源轨,并立即执行指令。或者,AVSBus 主设备可以向轨 1 发送一条命令,其中包含保持执行的指令,然后向轨 2 发送一条命令,其中包含一条保持执行的命令,然后向轨 3 发送一条命令,其中包含执行所有挂起命令的指令。这为 AVSBus 主设备提供了一种使多个电源轨同时改变的方法,这通常是遵守电源排序要求所必需的。

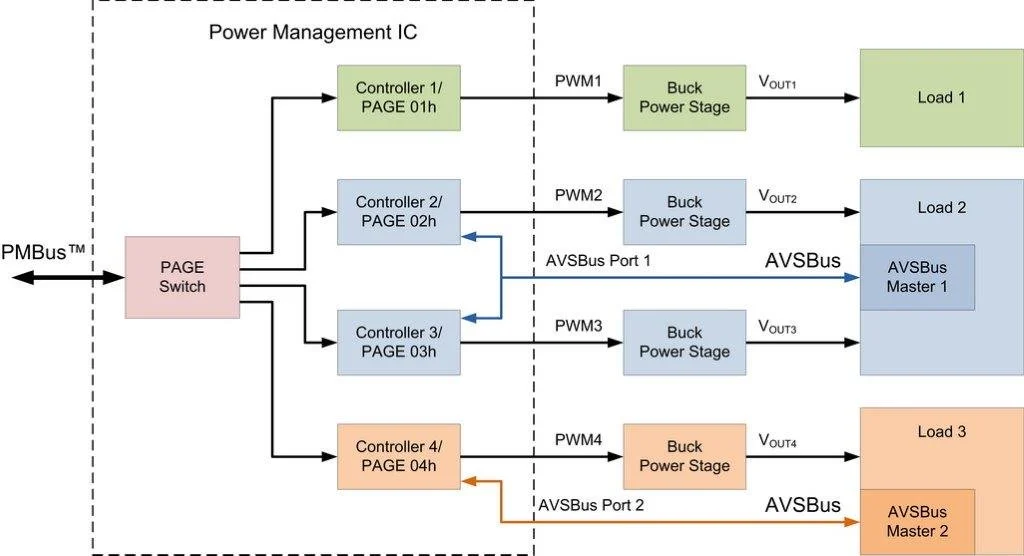

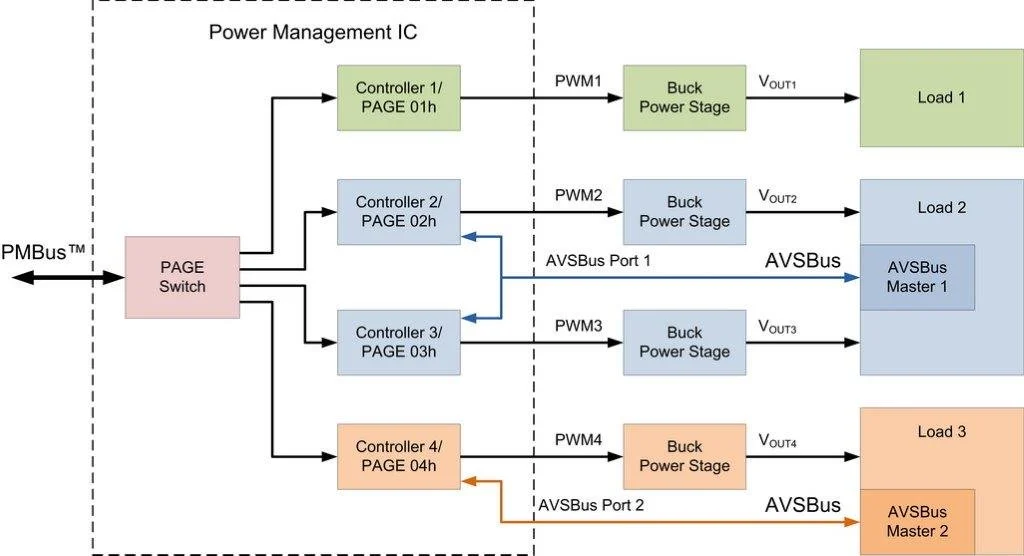

系统也可以同时具有 PMBus 和 AVSBus,如图 4 所示。在这种情况下,加电时,轨电压将由默认 PMBus 输出电压设置来设置。一旦运行,PMBus 主设备可以将控制权转移到 AVSBus 主设备。如果需要,PMBus 主设备还可以从 AVSBus 主设备收回控制权。 AVSBus 和 PMBus 规范中描述了如何管理这些控制转换以避免轨电压故障。

具有多个电源轨的 AVSBus 系统

图 3:具有多个电源轨的 AVSBus 系统

同时具有 PMBus 和 AVSBus 的系统

图 4:同时具有 PMBus 和 AVSBus 的系统

AVSBus 数据帧和传输

AVSBus 数据始终以 32 位帧传输。当 AVSBus 空闲时,所有数据线都为高电平。当主数据信号 AVS_MData 从高电平转变为低电平时,数据传输开始。它保持低一位,然后升高一位,以完成传输的开始。发送数据的设备,例如主设备向从设备发送帧,在时钟的上升沿发送数据。接收设备在时钟的下降沿捕获数据。每个帧的三位是循环冗余校验 (CRC),它可以很好地保证帧接收时未损坏。

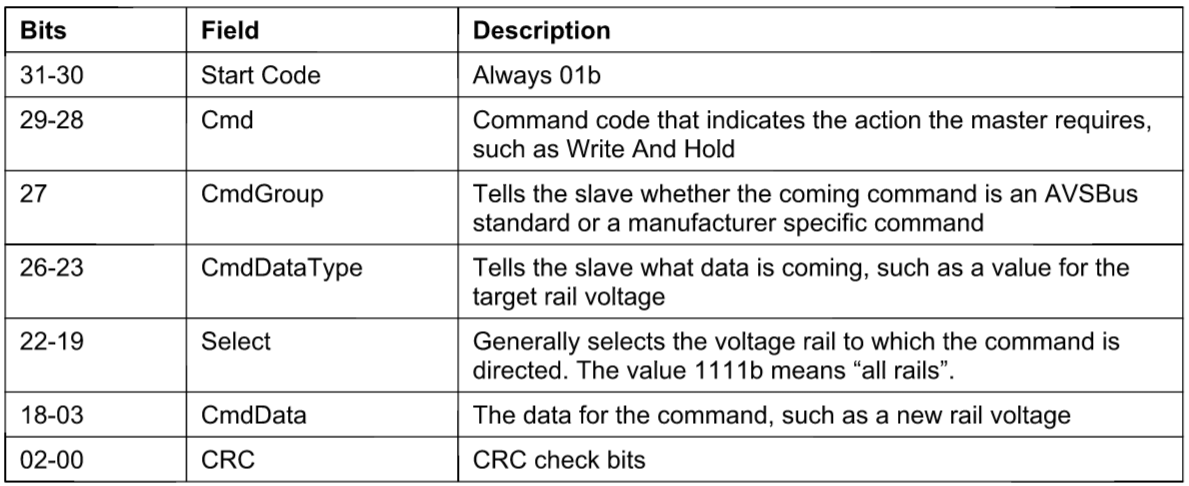

当主机向从机发送帧时,有两种可能的格式。写帧用于向从设备发送命令。读帧用于告诉从设备主设备正在请求数据,例如轨电压。这两种帧类型的格式在下面的表1和表2中给出。

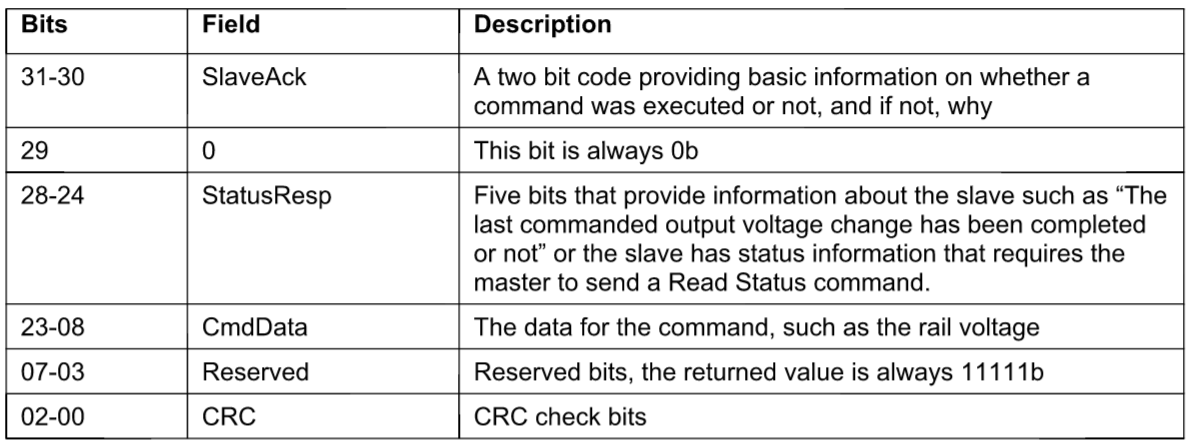

如果系统使用带有 AVS_SData 线的完整三线 AVSBus,则每次主设备向从设备发送帧时,从设备必须使用包含两位 ACK 字段和五位状态字段的帧进行响应。如果主设备已发送写入帧并且从设备未请求数据,则从设备发送的帧中的大部分位将设置为 1。如果主设备已请求数据,则从设备将返回该数据。包含返回数据的从站到主站帧的格式如表 3 所示。

从从设备到主设备的位应答字段比 I?C/SMBus/PMBus 系统的一位 ACK/NACK 具有显着优势。仅使用一个 ACK??/NACK 位,如果从设备不确认(“NACK”),主设备无法知道原因。这可能是因为接收到的数据已损坏、接收到的命令或数据无效、设备在处理接收到的数据时可能出现错误,或者从设备可能太忙而无法处理传入的传输。 AVSBus 的两位确认提供了一些附加信息,以确定帧是否已正确接收和处理,如果没有,则说明原因。两个 AVSBus 应答位指示:

10:CRC 错误,不采取任何措施;

11:CRC 良好,选择器无效,不采取任何操作;

01:CRC 良好,但由于资源不可用而未采取任何操作;或者

00:良好的 CRC,一切正常并采取行动。

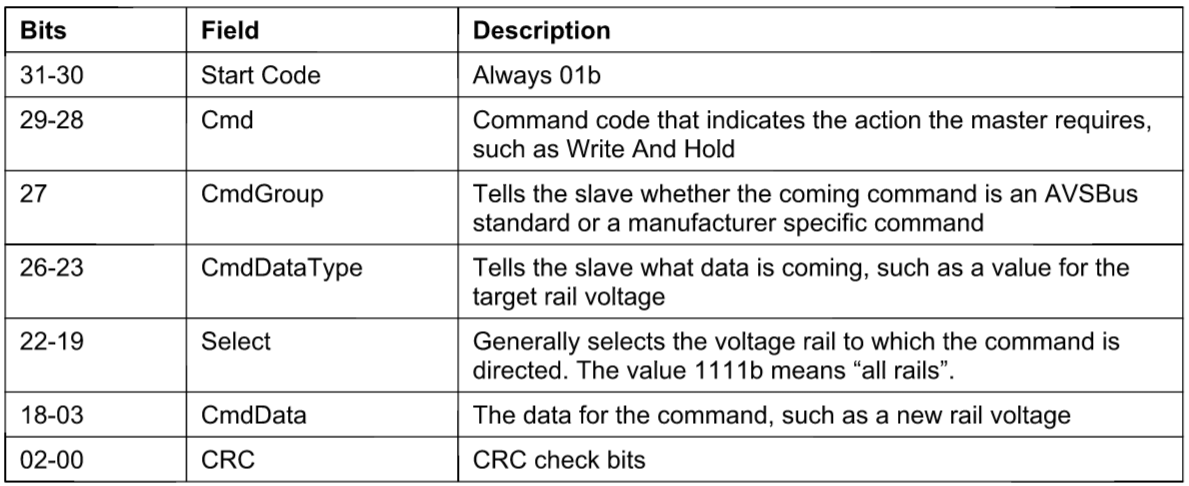

AVSBus 写入帧位字段

表 1:AVSBus 写入帧位字段

AVSBus 读取帧位字段

表 2:AVSBus 读取帧位字段

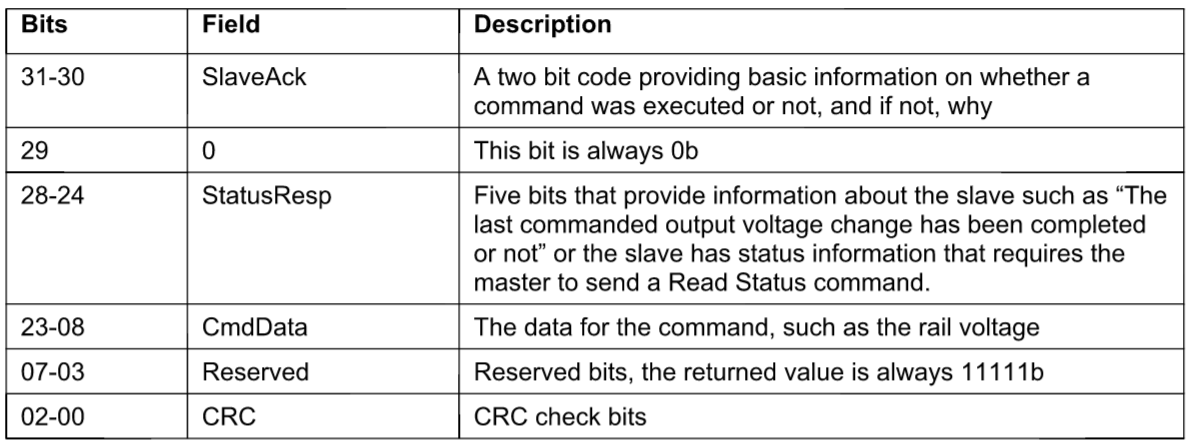

数据返回至主机时的 AVSBus 状态响应帧位字段

表 3:数据返回至主机时的 AVSBus 状态响应帧位字段