一颗高性能

芯片在区区数百平方毫米的

硅片上蚀刻数十亿

晶体管,晶体管间的间隔只有几十纳米,需要经过几百道不同工艺加工,而且全部都是基于精细化操作,制作上凝聚了全人类的智慧,是当今世界上的工艺、生产技术、机械的集中体现。

我们知道,芯片的设计制造要经过一个非常复杂的过程,可大体分为三个阶段:前端设计(逻辑代码设计)、后端设计(布线过程)、投片生产(制芯、测试与封装)。如图所示:

从图中可以看出,前端设计包括需求分析、逻辑设计与综合,输出门级网表;后端设计对原有的逻辑、时钟、测试等进行优化,输出终版图;投片生产是在特定电路布线方式与芯片工艺条件下将电路逻辑“画”到硅片上的过程。

一颗高性能芯片在区区数百平方毫米的硅片上蚀刻数十亿晶体管,晶体管间的间隔只有几十纳米,需要经过几百道不同工艺加工,而且全部都是基于精细化操作,制作上凝聚了全人类的智慧,是当今世界上的工艺、生产技术、机械的集中体现。在如此复杂和细微的芯片内部,除了完成所宣称的功能之外,在额外的电路中构建一个后门,使得可以接受外部控制,一般的验证检测手段通常不能找出任何问题,一般用户也很难察觉芯片上后门的操作行为。

在芯片设计阶段,对任何的代码或版图的改动都是非常容易的,在芯片设计阶段植入后门已屡见不鲜、广为人知,但是,在制造生产阶段,同样也可能被有意植入后门,而这一点则往往被人们所忽略。

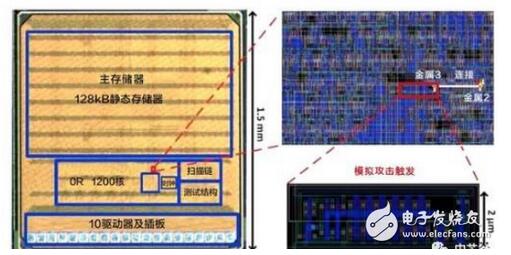

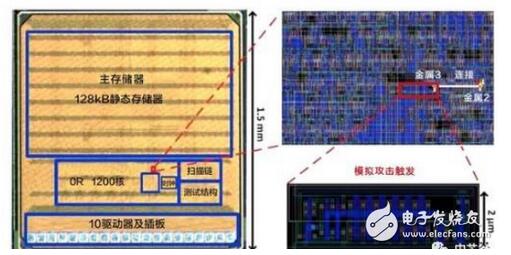

据报道,2016年6月,在DARPA和国家科学基金会支持下,美国密歇根大学首次在开源OR 1200

处理器制造中植入模拟恶意电路(即硬件木马),可进行远程控制和实施攻击。如下图所示,该硬件木马比传统

数字电路构成的硬件木马小2个数量级,结构小巧,难以检测,易于实现,危害极大。该事例再次证实了芯片潜在安全风险来源从设计阶段延伸至制造阶段,给芯片安全带来新的挑战。

应根据应用需求合理选择工艺制程

近年来,随着技术的不断进步,芯片工艺水平也得到逐步提高,较小的工艺制程能够在同样大小的硅片上容纳更多数量的芯片,可以增加芯片的运算效率;也使得芯片功耗更小。

但是,芯片尺寸的缩小也有其物理限制,摩尔定律正在逐渐失效,当我们将晶体管缩小到 20nm左右时,就会遇到量子物理中的问题,晶体管存在漏电现象,抵消缩小芯片尺寸获得的效益;另外,必须采用更高的机器进行芯片的掩膜蚀刻,会带来制造成本高、良品率下降等问题。

由此可见,芯片的工艺制程并不是越小越好,在我们推进芯片自主化研制过程中,绝不能一味追求高端工艺和高性能,而是根据应用需求选择国内成熟制造工艺,做到量力而行、够用就好。

如何实现真正意义的自主可控

卢锡城院士指出,自主可控至少应包括三个方面的涵义:一是信息系统的软件在设计和制造阶段不会被对手插入恶意功能,导致潜藏的不安全隐患;二是无论平时、战时都能按需提供相应软硬件产品,供应保障不受制于人;三是掌握技术,软硬件产品能适应技术进步或需求变化自主发展。

多年来实践经验告诉我们,芯片的国产化是一项长期艰苦的工作,无任何捷径可走,依靠买来的技术只会让我们的信息系统成为“房子盖在沙堆上”,只会让信息系统的发展永远被别人“牵着鼻子走”。唯有把技术和自主知识产权牢牢掌握在自己手里,坚持芯片设计、流片、生产全过程国产化,才能做到信息安全不受制于人,产业发展不受制于人,也才会有真正意义上的自主可控。