在电子学中,加法器是一种数位电路,其可进行数字的加法计算。加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

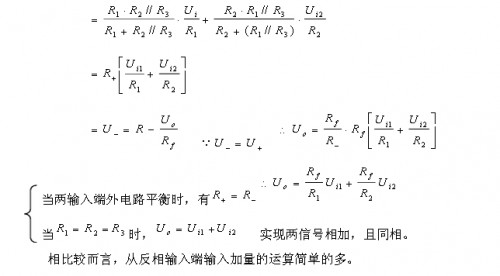

对于加法器为什么大家都选用反相加法器,而不用同相加法器呢?

基本原因是:

同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高

当选用同相加法器时,如A输入信号时,因为是同相加法器,输入阻抗高,这样信号不太容易流入加法器,反而更容易流入B端,而影响到B端的正常使用;同样,如B输入信号时,容易流入A端,而影响到A端的正常使用。

当选用反相加法器时,因为加法器输入阻抗低,不管是A端,还是B端信号,更容易流入加法器,而不会影响其它路的正常使用。

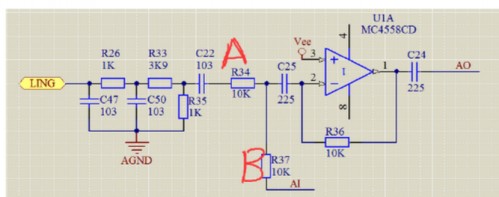

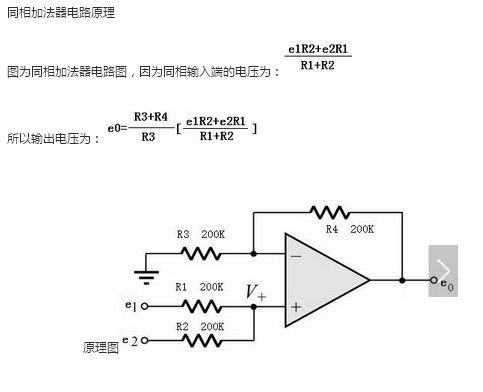

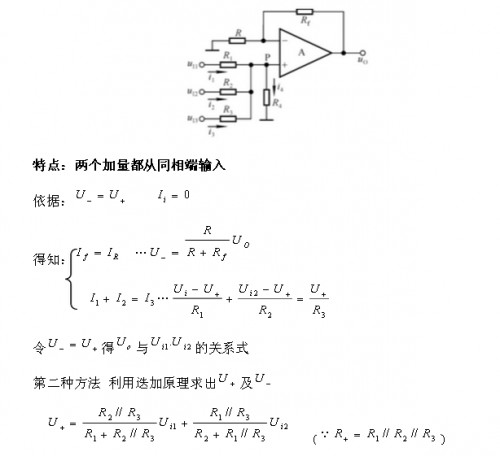

同相加法器电路原理

同相加法器计算

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。