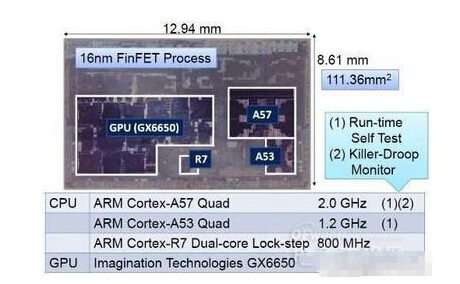

瑞萨开发的车用安全处理器采用16nm制程技术

ISSCC的常客、微处理器分析师David Kanter同意以上观点,他指出汽车的功率限制并不像手机那么多,而且对晶片的需求快速成长,特别是下一个十年将问世的自动驾驶车辆:“手机市场发展趋缓,意味着人人都在找下一个大商机;而显然资料中心领域已经是英特尔(Intel)的天下,但汽车领域还有很多能像是Nvidia等厂商取得差异化的机会。”

配备12通道的瑞萨处理器进行高解析度视讯解码仅耗电197mW

联发科智慧型手机应用处理器内含10

车用处理器还没有完全把手机处理器比下去,目前市面上其实只有少数晶片是采用14/16nm FinFET制程;主要是苹果(Apple)、三星(Samsung)智慧型手机的应用处理器,还有高通(Qualcomm)的Snapdragon 晶片。

联发科在ISSCC发表的智慧型手机处理器也不落人后,整合了8颗Cortex-A53、2颗A57,以及GPU、数据机与多媒体子系统。该款晶片采用20nm制程,将处理器分成三个丛集;中阶的2GHz A53丛集占据独特的地位,提供比低阶的1.4G A53丛集高40%的性能,以及比高阶2.5 GHz A72丛集低40%的耗电。

联发科技术副总Uming Ko表示,因为晶片尺寸小,在手机处理器内可以整合多少颗并没有限制:“如果你在超低功耗与高性能之间画一条直线,沿着它还有足够的性能点可以让你继续找到添加够多的效益。”

联发科以20nm制程生产的应用处理器已经开始出货

AMD的工程师则展示了让其PC 处理器Carrizo性能提升15%的聪明方法──仅透过简单地提供更积极的电源管理技术到该28nm制程设计中。该Bristol Ridge平台设计,是利用电源管理方案来克服与发热、电压、电流息息有关的性能限制。

16nm设计挑战

另外我还询问瑞萨工程师有关于16nm节点的设计经验,采用该制程的处理器设计需要克服多重图形(multi-patterning)与FinFET的挑战,晶片架构在某种程度上需要有所改变;不过他们有其他的看法。

Takahashi表示:“16nm节点有许多考验与困难…功号是一个问题,有时候可靠度也是问题;”他指出,16nm晶片的记忆体单元非常小,而且记忆体线(memory lines)很短、因此更容易遭遇软体错误。”

而Takahasi也表示,晶圆代工厂会提供16nm互连,但缺乏对先进功能的支援,像是瑞萨在自家晶片上互连内建的服务品质(quality-of- service controls)控制。为了简化16nm设计与验证工作,需要采用更高阶的设计语言例如System C。

此外Mochizuki 则指出,16nm晶片使用相对较高频率的时脉,很难维持低功耗;他表示,16nm节点:“与前几世代的制程比较起来弹性较少…为了降低功耗,我们可能需要改变设计模式。”

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。