在使用音频放大器的系统中,设计工程师必须克服的另一个技术挑战是“拍频”,亦即电源的开关DC/DC转换器之间的频差。如果拍频在100Hz到23kHz之间,则音频放大器很可能会检测到它们,并扰乱系统性能。

文探讨了如何使用相移时延技术来对主/从(Master/Slave)配置的多个DC/DC降压稳压器进行同步。对多个转换器进行相移可防止ON时间重叠和减小RMS电流、纹波和输入电容要求,这可改善系统电磁干扰并提高功率效率。该方法还可消除对高输入滤波电路的需要,并解决与拍频有关的问题。

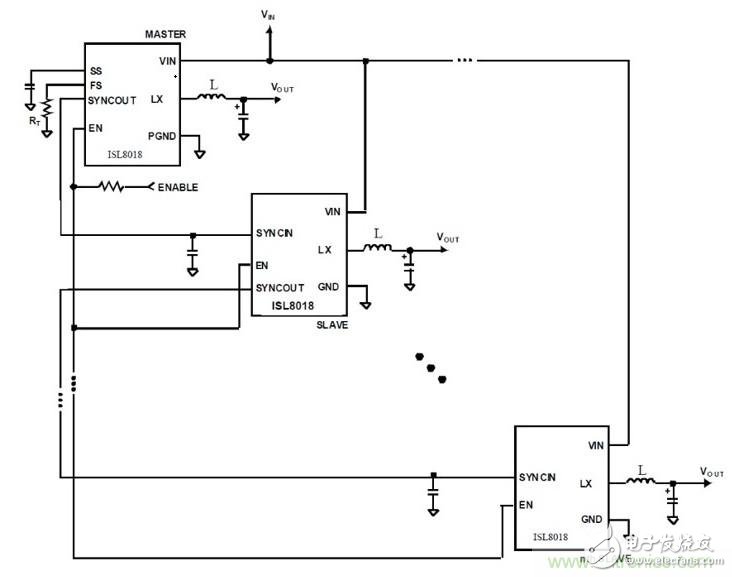

如图1所示,转换器1是“主”转换器,它为其余的“从”转换器提供设定频率。

图1:使用主/从配置的ISL8018 DC/DC转换器应用。

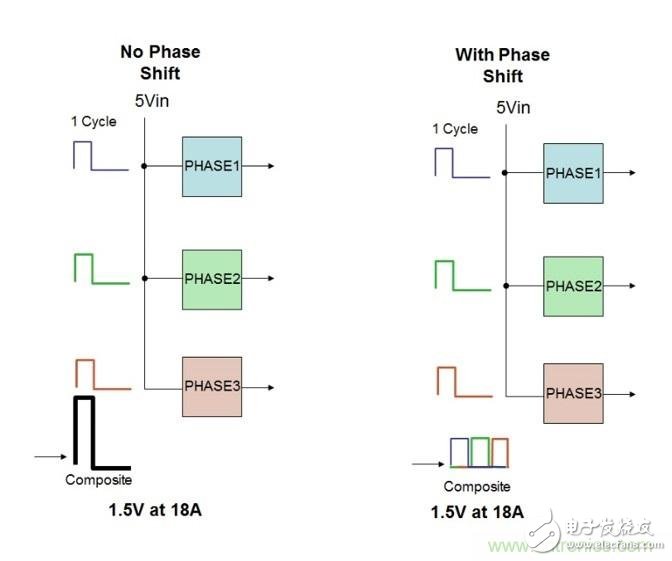

同步多个DC/DC转换器通道比较容易和简单,但相移编程却可能是个挑战。图2是同相和异相配置的DC/DC转换器的对比。两种设计均使用三相方法来提供24A输出电流。若想增大输出电流,可增加相数。在两种方案中,每个转换器均已优化为8A输出电流。左侧配置为同相工作,而右侧的设计使每个相位偏移约120°。左侧的3个转换器具有24A(3&TImes;8A)峰值输入纹波或12A RMS (50%占空比) 。右侧的3 个异相工作转换器的工作电流为8A或4.3A RMS(50%占空比)。

图2:同相和异相配置三相DC转换器对比。

如上文所述,使用相移技术可显著减小输入和输出电容要求。RMS输入电流由公式1规定:

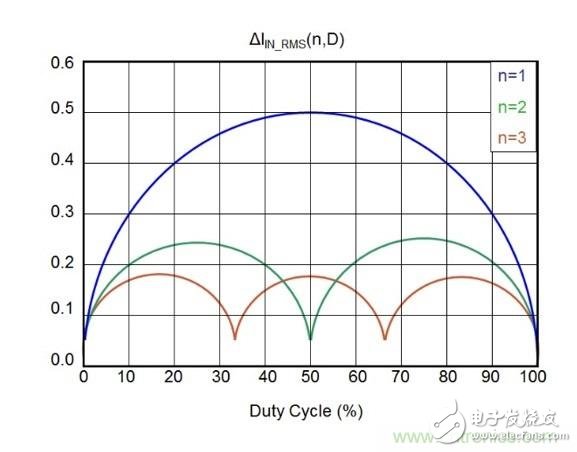

其中,n为相数,L为输出电感,Fs为开关频率,k(n,D)=floor(n,D),floor函数的返回值为小于或等于输入值的整数。图3显示了ΔIIN_RMS(n,D) 与占空比的关系曲线。

图3:ΔIIN_RMS(n,D) 与占空比的关系曲线。

表1总结了三个同相工作转换器和三个异相工作转换器的性能结果对比。

表1.异相方案比同相设计具有显著优点。

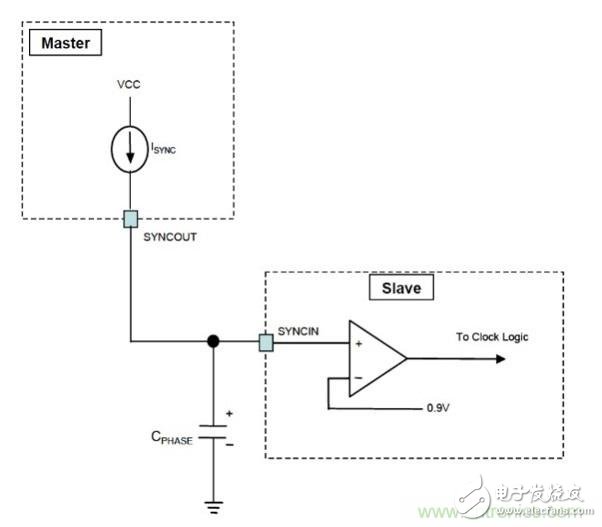

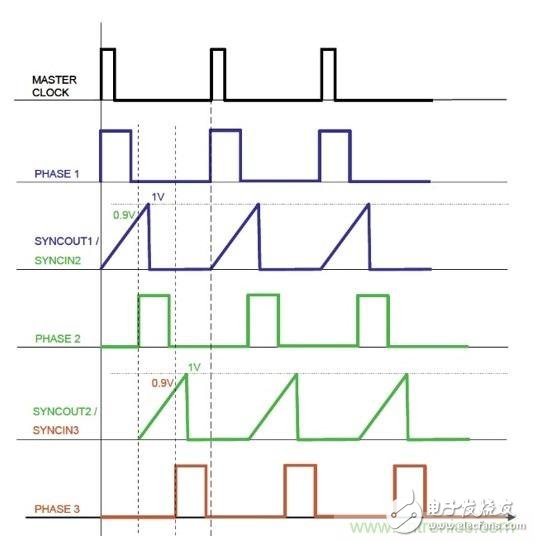

同步降压稳压器( 如ISL 8018)为实现异相工作提供了一种简单、低成本的方法。主开关稳压器的SYNCHOUT特性在每个时钟周期开始时提供一个电流脉冲ISYNC。该电流源在达到1V SYNCHOUT电压后终止并放电至0V。从稳压器的SYNCIN特性的检测阈值为0.9V。当SYNCIN的每个上升沿达到0.9V时,其PHASE的ON脉冲即被触发。只需在SYNCIN至GROUND之间添加一个小而便宜的电容,即可改变SYNCHOUT电流源转换速率。

图4所示为主/从电路示意图,图5所示为其逻辑实现。相移时间(t,单位ns)等于2.8·CPHASE(单位pF)。

图4:主/从电路实现。

图5:主/从逻辑实现。

电流源的实现比较简单,只需要70平方密耳的裸片面积。该面积可以调整,以实现±5%的公差。同样,SYNCIN的阈值也可调整为±0.5%。应用容值在pF范围内,只需一个具有±1%小公差的低成本NPO或C0G介质的陶瓷电容即可。这样相移公差约为5.12%。

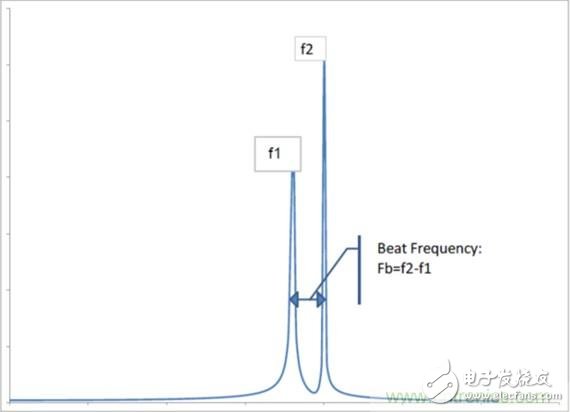

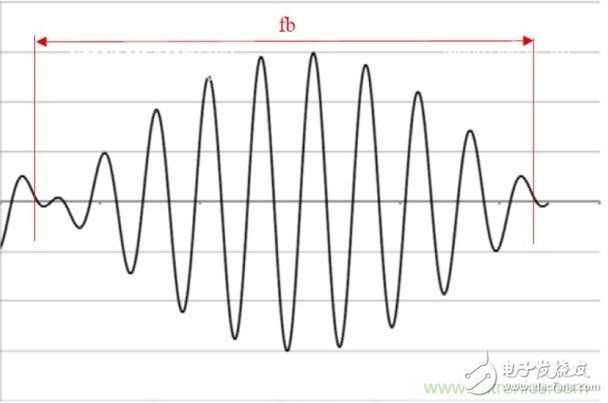

如上文所述,ISL8018可从主转换器或外部时钟加以同步。该特性在多个稳压器的工作频率彼此很接近时是必不可少的。图6显示了工作频率分别为f1和f2的转换器1和2。输入可见一个“拍”频(fb),亦即f1与f2之差。如果没有隔离的话,该fb将在GROUND出现。输出则可能如图7所示,其中的包络即为“拍”频。

图6:输入源的频谱图。

图7:地线纹波电压噪声。

通常情况下拍频非常低,特别是在对多个电源轨使用同类型转换器时。该低水平将出现在整个系统之中。在包含音频的计算、电信、工业或医疗设备应用中,系统的音频放大器极有可能接收到拍频噪声。如上文所述,添加共模或差分模式噪声滤波器将会增加系统设计成本。

然而ISL8018 DC/DC转换器的SYNC特性能够通过使用多个时钟频率相同的转换器解决拍频问题。于是fb将等于0Hz,从而消除整个系统中的拍频。

结束语

诸如ISL8018等DC/DC转换器能够为噪声敏感型应用(特别是包含音频电路的应用)提供低成本解决方案。借助相移时延技术,在主/从配置中采用多个负载点(POL)DC/DC转换器,有助于设计工程师通过降低RMS电流、纹波和输入电容要求而优化其电源设计。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。