1 引言

随着集成电路集成度的提高,越来越多的元件集成到芯片上,电路功能变得复杂,工作电压也在降低。当一个或多个电路里产生的信号或噪声与同一个芯片内另一个电路的运行彼此干扰时,就产生了芯片内的EMC问题,为常见的就是SSN(Simultaneous Switch Noise,同时开关噪声)和Crosstalk(串音),它们都会给芯片正常工作带来影响。由于集成电路通过高速脉冲数字信号进行工作,工作频率越高产生的电磁干扰频谱越宽,越容易引起对外辐射的电磁兼容方面问题。基于以上情况,集成电路本身的电磁干扰(EMI)与抗扰度(EMS)问题已成为集成电路设计与制造关注的课题。

集成电路电磁兼容不仅涉及集成电路电磁干扰与抗扰度的设计和测试方法,而且有必要与集成电路的应用相结合。针对汽车电子领域来讲,将对整车级、零部件级的电磁兼容要求强制性标准,结合到集成电路的设计中,才能使电路更易于设计出符合标准的终产品。作为电子控制系统里面为关键的单元——微控制器(MCU),其EMC性能的好坏直接影响各个模块与系统的控制功能。

本文在汽车电子MCU 中采用抗EMI的设计方法,依据IEC61967传导测试标准,对汽车电子MCU进行电磁干扰的测试。

2 汽车电子MCU设计方法

下面介绍在汽车电子MCU中使用的可行性设计方法以及其他几种抗EMI设计技术。

2.1 时钟电路设计

由于时钟电路产生的时钟信号一般都是周期信号,其频谱是离散的,离散谱的能量集中在有限的频率上。又由于系统中各个部分的时钟信号通常由同一时钟分频、倍频得到,它们的谱线之间也是倍频关系,重叠起来进而增大辐射的幅值,因此说时钟电路是一个非常大的污染源。

针对汽车电子MCU 数字前端设计,在抗EMI方面采用门控时钟的方法改进。任何时钟在不需要时都应关闭,减低工作时钟引起的电磁发射问题。根据A8128(汽车电子MCU的型号)芯片系统功能设计要求,采用Run、Idle、Stop和Debug四种工作模式,在每一种工作模式下针对系统时钟、外设模块时钟进行适当门控。此外,还有几种在时钟方面常见的抗EMI的设计方法,包括:

①降低工作频率

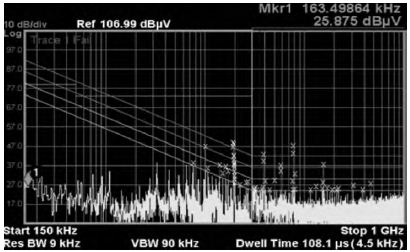

MCU的工作时钟应该设定为满足性能要求所需的频率。从下面的测试结果可以看出,一个MCU的运行频率由80MHz变为10MHz,可以使频谱宽频范围内的干扰峰值产生几十dBμV 的衰减,而且能够有效的降低功耗。

②异步设计

异步电路工作没有锁定一个固有频率,电磁辐射大范围均匀分布而不会集中在特定的窄带频谱中。这一关键本质特征决定了即使异步电路使用大量的有源门电路,它所产生的电磁发射也要比同步电路小。

③扩展频谱

扩展频谱时钟是一项能够减小辐射测量值的技术,这种技术对时钟频率进行1%~2%的调制,扩散谐波分量,在CISPR16或FCC发射测试中峰值较低,但这并非真正减小瞬时发射功率。因此,对一些快速反应设备仍可能产生同样的干扰。扩展频谱时钟不能应用于要求严格的时间通信网络中,比如FDD、以太网、光纤等。

2.2 IO端口设计

在汽车电子MCU 的输入输出端口设计中,也加入了抗EMI方案,包括翻转速率(slew rate control)和驱动强度(drive strength)控制方法。通过在所有通用P口引入可配置的翻转速率和驱动强度寄存器,在需要的时候打开相应功能。翻转速率有打开和关闭两种选择,打开后能够有效地平缓上升沿或者下降沿,降低瞬态电流,进而控制芯片产生的电磁干扰强度。驱动强度有强驱动电流和弱驱动电流两种选择,在能够满足工作驱动强度的情况下,选择弱电流驱动会更好的控制电磁干扰现象。

另外,基于GSMC 180nm工艺库,选择具有施密特触发特性的IO,可以有效地平缓输入信号中带进来的尖峰或者噪声信号等,对芯片的电磁抗扰度有所帮助。

3 汽车电子MCU测试方案

IEC61967标准是国际电工委员会制定的有关集成电路电磁发射的标准,用于频率为150kHz到1GHz的集成电路电磁发射测试。标准中涉及到辐射和传导两类测试方法,由于传导方式的电磁干扰带给芯片应用上的影响更大一些,本次试验选取IEC61967-4直接耦合法进行测试。该方法又分为1Ω测试法和150Ω测试法,1Ω测试法用来测试接地引脚上的总干扰电流,150Ω测试法用来测试输出端口的干扰电压。

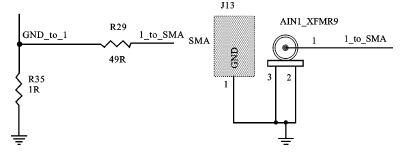

在测试时,需要在进行测试的电路中接入串联电阻为1Ω的电流探针(探针即为1Ω测试网络,已经集成在EMC测试板的芯片地端与PCB地平面之间),49Ω串联放置为了形成50Ω匹配,用接收机测量射频电流流经该电阻时产生的射频电压,所测得的电压应为所有流回到集成电路的射频电流在电流探头上产生电压的总和,测得的电压值可以换算为流过探针的电流,测试环境图如图1所示。

图1 1Ω测试环境

在150Ω测试中,集成电路的引脚通过标准规定的匹配网络接到测试接收机,通过150Ω探针(探针即为150Ω测试网络,已经集成在EMC测试板上)可以测量SSN在输入输出端口和电源两类引脚上的传导干扰,通过计算可以将接收机测量的电压转换为噪声电压幅值,测试环境图如图2所示。

图2 150Ω测试环境

下面是针对EMI进行的1Ω和150Ω测试步骤,包括测试前准备工作以及测试数据分析等。

3.1 测试前装备工作

①环境温度

本次实验集中在晚间进行,现场温度控制在23±2℃范围内,符合标准要求。

②环境噪声电平

将DUT(被测设备)固定在实验台上且为断电状态,用EMI接收机测量残留噪声。本次实验环境噪声电平在可接受的测试要求内,详情请参看图6。

③其他环境条件

所有其他可能影响测试结果的环境条件,例如环境湿度。本次实验所测得的相对湿度为45%RH左右。

④确认工作状态

给DUT供电并检查确认IC处于正常的工作状态,同时在实验时保持周围的测试条件不变。

3.2 1Ω测试

(1)将SMA连接线一端连接到测试板,另一端连接到接收机(安捷伦N9030,内置N141A电磁兼容测试软件),将EMI接收机的测量频率范围设置为150kHz到1GHz,根据标准对测试操作的要求,分成150kHz~30MHz(RBW 为9kHz)和30MHz~1GHz(RBW 为120kHz)两段。下面测试图中绿色边框范围内的是150kHz~30MHz,范围外的是30MHz~1GHz。

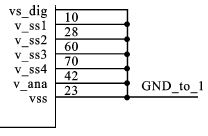

结合汽车电子MCU 端口特性以及标准要求,将接地端口与1Ω网络相连,再与SMA口相接,引入EMI接收机进行监控,原理图如图3、图4所示。

图3 芯片的地网络引脚

图4 1Ω网络

(2)选取可能影响EMC特性的因素,在时钟上分别测试10MHz、20MHz以及77MHz频率下电磁干扰大小数值,在测试功能上选取模数转换程序ADC;

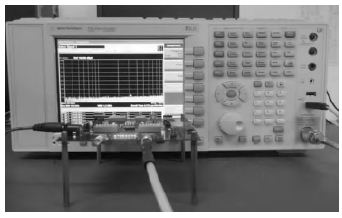

(3)测量每一段频谱内可能出现的干扰,提取各个谐波的包络值,接收机的电压可以换算为流过探针的电流。测试仪器以及EMC测试板如图5所示;

图5 实际测试环境

(4)在对每个频率点测试的时候要进行多次测量,以便排除偶然因素的干扰。下面是各个测试情况的说明;

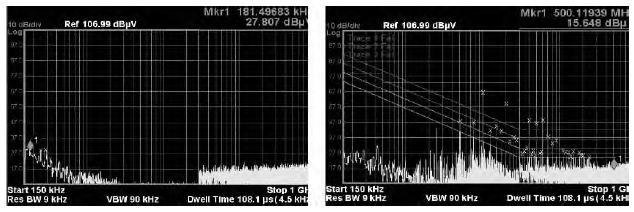

①时钟采用外部晶振10MHz,烧录SRAM 中的程序为ADC。图6左侧为未上电时的环境噪声信号,右侧为上电但未运行程序的测量结果。

图6 断电vs.上电

通过对比可以得出上电之后在整个频谱范围内干扰强度变大,时钟的固定周期将使电磁辐射集中在时钟基波和谐波附近很窄的频谱范围内。根据傅里叶级数展开公式可以得出,在时钟倍频处的频点其干扰值也越大,所以在10MHz、20MHz等倍频点处的现象更明显,

②为了进一步对比,运行ADC程序,分别在10MHz、20MHz以及77MHz时钟下进行测试,比较不同时钟接地引脚总干扰电流大小,测试结果如图7、图8、图9所示。

图7 10MHz—ADC测试图

图8 20MHz—ADC测试图

图9 77MHz—ADC测试图

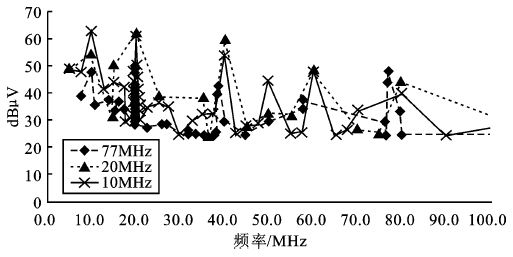

图10 10/20/77MHz—ADC测试数据整理

图7、图8、图9分别是10MHz、20MHz和77MHz的测试图,图10是整理后的数据。通过对比可以得出,频谱大致集中在100MHz以内,在对应工作时钟的主频点处干扰值,10MHz、20MHz情况下在相应倍频点(如40MHz、60MHz等频点)附近的干扰值也比较集中。

提取数据得到10 MHz时峰值点为9.999MHz(62.643dBμV),20 MHz 时的峰值点为20.002MHz(61.692dBμV),77MHz时的峰值点为19.264MHz(48.049dBμV)以及77.042MHz(47.316dBμV)。可以看出,77MHz时干扰强度和密度反而要弱于20MHz,可能是由于77MHz是MCU工作的极钟,此时工作性能受到一定影响,导致测试的结果有所不同。

③由于汽车电子MCU的工作时钟可以选择外部晶振或者内部PLL倍频,所以要对两种情况分别测试,以便比较是否有差别。运行ADC程序后的测试结果如图11所示。

图11 PLL vs.外部晶振(10MHz)

从图11中可以看出,在频谱范围内各个峰值点的分布大致相同,整个频谱范围内没有明显差异,MCU通过外部晶振或PLL倍频两种方式测得的结果基本一致,时钟源选择上不会对芯片的电磁干扰强度带来影响。

3.3 150Ω测试

(1)设备装置连接同1Ω测试法的步骤①;

(2)根据芯片电源类型,电源分为4路,分别是VDD1(数字IO 供电的5V 电源信号)、VDD2(为ADC和PLL供电的LDO 的5V 电压)、VDD3(数字逻辑LDO的5V电压输入)和VDD4(Flash的5V电压输入)。可单独对每一路电源的干扰噪声进行捕捉,连接方式与1Ω 测试法步骤②相同,如图12所示;

图12 VDD连接150Ω网络145

(3)根据汽车电子MCU应用特点,选取为典型的PWM、CAN 程序,为了方便以后对众多引脚进行单独测量,将P0、P1、P2(P3未涉及到外设功能复用)端口共24个引脚进行了开关控制,再通过150Ω耦合网络连接到EMI接收机,图13是P0端口的电路原理图,P1和P2的原理图同P0。

图13 IO-P0连接150Ω网络

(4)重复测试多次,得到较多测试样本,经过整理,下面是各个测试情况的说明。

①从电源端口结果来看,区别很小,下面以VDD1为例进行分析说明。VDD1测试选取了ADC和counter(数字计数器)的程序,以比较不同类别的程序对数字供电是否有影响,测试结果如图14、图15所示。

在10MHz和20MHz时钟上对比,ADC峰值分别为35.827dBμV、43.517dBμV;counter的峰值为35.899dBμV、43.271dBμV。可以得出频率越高,干扰强度越大。但就两类程序横向对比来看,结果基本上一致。另外还发现60~300MHz和550~650MHz两处集中的干扰频谱,可见电源处的干扰在高频附近比较明显。

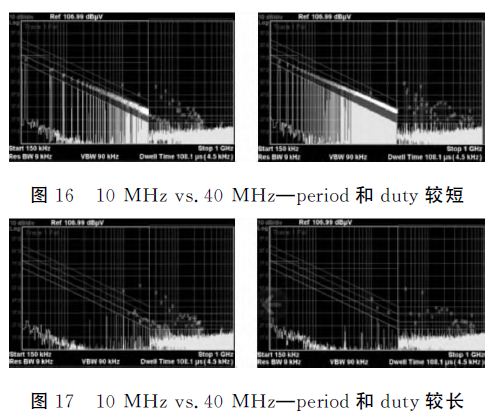

②PWM 功能测试

双通道模式下,在不同占空比和周期大小情况下,测试对应P口引脚处传导发射强度的大小,测试结果如图16、图17所示。

从图16中的干扰密度可看出时钟对电磁干扰影响程度。在图17中,由于period和duty较长,测试结果相差不大,此时时钟频率变成次要因素,主要因素取决于输出引脚处高低电平变化周期长短。

③CAN功能测试

运行Loopback(回路模式)程序,在不同时钟频率下进行比较,测试结果如图18、图19所示。

从图16~19中观察,随着时钟频率变大,TX和RX端口的传导辐射强度也变大。对于RX端口,10/40MHz频点附近的干扰密度比较大,且在40MHz时候现象更明显,捕捉到连续三个频点(图18右侧标注),分别是39.060 MHz(71.063dBμV)、39.360MHz(67.447dBμV)、40.020MHz(39.171dBμV),两个时钟下的峰值都在70~85dBμV 之间,但一般都在10MHz以下,应该是受低频某一频点的影响较明显。

对于TX端口,10/40MHz频点附近的干扰密度没有RX明显,峰值也都在70~85dBμV 之间,且发生在10MHz以下,和RX的特点大致相同。

4 测试结果分析

从测试数据结果可以总结出以下几点:

①在时钟频率上,从10 MHz到40 MHz、77MHz,干扰强度或是密度在整体上都会增加,可以是一小段频谱或者是整个频谱范围内,这与测试对象关系比较大。分析原因不难发现,由于时钟电路产生的时钟信号一般都是周期信号,其频谱是离散的,离散谱的能量集中在有限的频率上,又由于系统中各个部分的时钟信号通常由同一时钟分频、倍频得到,它们的谱线之间也是倍频关系,会重叠起来进而增大辐射的幅值。

②在程序烧写方式上,外部晶振或PLL倍频两种方式测得的结果基本一致,整个频谱范围内没有明显差异,时钟源选择上不会对芯片的电磁干扰强度带来影响。

③从VDD1测试结果来看,除了得出频率越高,干扰强度越大之外,还发现出现干扰的频谱范围分别在60~300MHz和550~650MHz两处,可见电源处的干扰在高频附近比较明显。

④对于PWM 功能,通过配置输出波形周期和占空比大小,会导致在不同时钟下产生的电磁干扰强度有所差异。由于双通道模式下寄存器为16bit(原单通道模式为8bit),此时周期和占空比可配置的数值变大,PWM 波输出引脚处的高低电平翻转周期就取决于周期和占空比的设置,与时钟的关系变得没有之前如此紧密,时钟变成了次要因素。由此建议在满足功能要求的前提下,使用PWM 功能时尽量将周期和占空比数值变得大一些,这样会较好地改进EMC性能;

⑤对于CAN 总线来讲,通过10 MHz和40MHz时钟对比,当合理地降低时钟工作频率,会使一大段频谱范围内的干扰值降低,从整体上较好的控制EMI带来的影响。

5 结束语

对于微电子行业来说,芯片级电磁兼容性的设计与测试已经成为一个非常重要的主题。实际上,如果不对集成电路电磁辐射及抗扰度方面进行深入的研究,就很难满足电子设备电磁兼容性方面的需要。本文通过对设计方法的引入,并进一步通过测试方案去总结归纳影响电磁发射的因素和原因,从而间接证明了设计方法的必要性和重要性。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。