摘要:绝缘体上硅(Silicon On Insulator,简称SOI)以其独特的材料结构有效克服了体硅材料的不足,使其在能够成功应用于辐照恶劣环境中。本文使用Sentaurus TCAD软件中的SDE(Sentaurus Structure Editor)工具设计一个0.18μmH栅P-Well SOI MOSFET器件结构,并且运用Sentaurus TCAD软件中的Sentaurus Device工具进行器件特性仿真,使用INSPECT和TECPLOT_SV工具查看仿真结果并得到设计的器件的阈值电压(Vth=1.104V)和饱和电流(Idsat=3.121E-4A)。

1.引言

近年来范围内出现了新一轮的太空探索热潮,世界各主要航天大国相继出台了一系列雄心勃勃的航天发展规划。空间技术的迅猛发展,使各种电子设备已经广泛应用于人造卫星、宇宙飞船等设备中,在天然空间辐射环境中往往因经受空间辐射而导致性能降低或失灵,甚至终导致卫星或空间飞行器灾难性后果。因此,必须在辐照恶劣环境中的电子设备使用抗辐射的电子元器件。

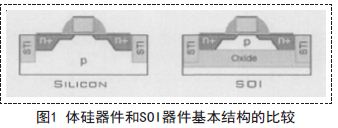

绝缘体上硅与体硅器件相比较,其独特的绝缘层把器件和衬底隔开,减轻了衬底对器件的影响,降低了源漏极电容、消除了闩锁效应、改善了短沟道效应以及热载流子效应、提高了抗辐照性能等等,因此,SOI技术能够成功地应用于抗辐射领域,其被国际上公认为“二十一世纪的硅集成电路技术”.SOI与体硅MOS器件结构的比较如图1所示。

通常根据在绝缘体上的硅膜厚度将SOI分成薄膜全耗尽FD(Fully Depleted)结构和厚膜部分耗尽PD(Partially Depleted)结构。本论文中设计的SOI MOS器件是薄膜全耗尽结构的,这是因为薄膜SOI结构的器件由于硅膜的全部耗尽完全消除“翘曲效应”,且这类器件具有低电场、高跨导、良好的短沟道特性和接近理想的亚阈值斜率等优点。因此薄膜全耗尽FDSOI应该是非常有前景的SOI结构。

因此,对SOI MOS器件进行研究具有十分重要的意义。本论文将设计一个0.18μmH栅P-Well SOI MOS器件并对该器件进行电学特性仿真,通过仿真获取阈值电压和饱和电流这两个重要参数。

2.设计0.18μmH栅P-Well SOI MOSFET

整个设计流程为:首先,使用SentaurusStructure Editor工具编辑器件的基本结构和设定注入粒子的类型和剂量;然后,在使用Sentaurus Structure Editor工具中的网格生成工具Mesh设置器件的网格参数;使用Sentaurus Device工具仿真器件的电学特性并测试。在这一部分,我将通过上述流程来设计一个0.18μmH栅P-Well SOI MOSFET器件。

对于器件结构的设计,器件结构的X和Y轴范围分别为[-0.3,0.3]和[-0.3,0.3],Z轴的范围为下面过程中设置的厚度的总和。

首先,画一层0.2μm厚度的硅衬底,硅衬底上画一层0.15μm厚度的绝缘氧化层,再在绝缘氧化层上画一层0.1μm厚的硅层(即顶硅层);然后,在顶硅上放置一层0.005μm厚度的氧化层,氧化层上放置一层宽度为0.18μm,厚度为0.04μm的多晶硅栅层;,在栅的周围放置侧墙并定义接触点。

经过上述过程,器件的基本结构已经完成。下面,往顶硅中注入剂量为1E+11cm-3的硼粒子来形成P-Well.在对源漏极进行注入粒子之前,需要先定义粒子注入的窗口,然后,设置注入粒子类型、峰值剂量、峰值位置和扩散长度。源漏极注入粒子参数如表1所示。

器件的结构和掺杂粒子的一些参数已经设置好,现在需要做的工作就是设置网格,这里设置了三个部分的网格,全局网格、顶硅层部分的网格和沟道处的网格。设置沟道处网格是因为仿真器件的电学特性时,粒子的传输主要是在沟道处,在沟道处设置合理的网格不仅会提高仿真,也能优化仿真速度。

设置完网格后,就可以通过生成网格把器件结构,掺杂信息,网格信息集成到一个网格文件中,进行器件电学特性仿真时需要用到这个文件。

器件的电学特性仿真,可以理解为半导体器件(比如,晶体管或则二极管)电学特性的虚拟测试。器件被看作为有限网格点构成的结构,结构中的每个点都包含着金属类型、掺杂粒子类型和浓度等属性。对于每个点,载流子浓度、电流密度、电场强度、电子空穴对的生成和复合速率等都要进行计算。

3.结果和分析

0.18μmH栅P-Well SOI MOSFET器件的结构和器件特性仿真如图2到图7所示。使用INSPECT工具显示器件电学特性曲线,TECPLOT_SV工具显示器件结构。这两个工具都在Sentaurus TCAD软件中。

图2和图3所示分别显示了生成网格之前的器件结构和生成网格之后的终器件结构。图中显示的有花纹的界面代表的是源极、漏极、栅极、衬底的接触点,这些接触点是为了器件特性仿真设置电压参数的。图中凹的地方是源极和漏极,凸的地方是H形栅极;按从上到下的顺序看,下面3层结构分别为顶硅、绝缘氧化层、衬底。

需要对设计的器件做传输特性和输出特性分析,结果如图4和图5所示。从图中我们可以得到所设计器件的阈值电压(Vth)为1.104V,饱和电流为3.121E-4A.

阈值电压(Vth)是MOSFET重要的参数之一,通常将传输特性曲线中输出电压随输入电压改变而急剧变化转折区的终点对应的输入电压称为阈值电压。当栅极上所加的电压大于阈值电压时,器件处于开通状态;小于阈值电压时,器件处于关闭状态。

本文所设计的器件的阈值电压为1.104V图6中显示了在不同辐照剂量条件下,器件阈值电压的漂移。这是因为在辐照会产生总剂量效应,在MOS器件中总剂量效应主要是在氧化物中产生电荷以及在Si/SiO2界面产生界面态。即使在室温条件下,SiO2中的电子也是可以移动的,它们能够迅速离开氧化层;另一方面,陷在氧化物中的空穴会产生正氧化物电荷,该电荷会导致器件阈值电压产生负漂移。同时,总剂量辐照也会也会在Si/SiO2界面产生界面态,与氧化物电荷作用相反,界面态会使阈值电压增大。

4.总结

使用Sentaurus TCAD软件成功设计了0.18μmH栅P-Well SOI MOSFET器件并进行了特性仿真。整个设计过程中用到了SentaurusTCAD软件中的SDE和Sentaurus Device两个主要工具,分析仿真结果得到了阈值电压(Vth)和饱和电流(Idsat)两个主要参数,参数值和理论相符合。(作者:周永辉)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。