摘要:对实现快速锁定的原理和方法进行了分析,设计了一种实现1 μs快速捷变频的方案。采用电压预置的辅助捕获方式,减小跳频的起始频差,同时利用反馈修正进行预置,可以极大地提高锁相跳频速度。对方案实现中的一些问题进行了讨论。

0 引言

频率捷变信号广泛应用于雷达探测、电子战、导航定位、通信和测试系统中等,其性能指标的优劣直接影响武器装备的性能。现代局部战争中,雷达探测、电子对抗与反对抗的竞争日趋激烈,武器系统对其关键部件之一的频率源提出了越来越多的要求。其要求频率合成器输出频带宽、频率点数多、相位噪声低、杂散输出小的同时,频率转换速度要快,从发出频率转换指令开始,到频率转换完毕,并进入允许的相位误差范围所需的时间要短。

目前频综技术从其合成方法上基本可分成三类:直接频率合成;间接式频率合成;直接数字频率合成(DDS)。三种方法在实现频率捷变方面各有特点,直接式在捷变速度上具有很大优势,但是大量的倍频、分频、混频、滤波环节增加了电路的体积和复杂度,方法移植性差;锁相式频率源具有频带宽,频谱纯,结构简单,利于小型化、集成化,噪声低的优势,被广泛应用在各种电子设备和系统中,但其缺点是频率转换时间慢;DDS具有细分辨,捷变速度快的优势,缺点是杂散较大。如果能够将三种方法有效的结合起来,以锁相环为主体,DDS和直接式为辅助,采用有效的措施降低主环锁定时间的同时可以大大改善合成器的各种性能参数,如体积大小、频率分辨率等。

一般的锁相式频率合成器跳频时间都在数十微秒到数百微秒,如果能够将锁相式频率合成器的跳频时间缩短到数微秒甚至1 μs之内无疑将有重要的意义。目前提高锁相源跳频速度的方法主要采用辅助捕获法,其中以减小起始频差的电压预置方法使用广泛。本文主要关注的是如何提高锁相环的锁定速度,并应用到具体的合成器研制中。

1 锁相环快速捷变原理分析

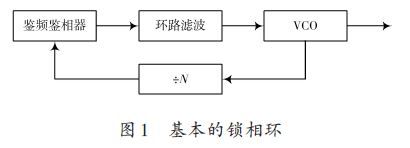

由于应用鉴频鉴相器的锁相环比传统应用正弦模拟鉴相器的锁相环具有快得多的锁定速度,故本文只对应用鉴频鉴相器的锁相环进行讨论。

鉴频鉴相器在起始频差较大时表现为非线性,只有频差较小时才近似表现为线性。其工作过程可根据所加输入频率阶跃的大小分为两部分:牵引过程和锁相过程。若输入频率阶跃在锁定带内,则锁相环仅发生锁相过程;若输入频率阶跃较大,超出锁定带范围,则锁相环既发生牵引过程又发生锁相过程。锁定带的概念为,输入参考频率与压控振荡器输出频率偏差使锁相环在一个单拍周期内获得锁定,则参考频率与反馈频率差值的大小即为锁定带大小。

电荷泵锁相环的牵引过程属于一种紊乱过程,它是一个瞬态过程,同时也是一个频率捕获过程,可用锁相环的频率特性作近似分析。而在锁定带内,电荷泵锁相环为相位捕获过程,可近似采用线性系统理论分析。采用二阶有源比例积分滤波器的锁定带为:

式中:ωn 为环路自然谐振角谐振频率;ζ 为阻尼因子;Δftol 为终锁定频差;f1 为初始频率;f2 为进入锁定带频率。

锁定带外牵引过程时间的近似计算公式(以鉴相范围为2π 的鉴频鉴相器为例)为:

从公式可以看出,环路带宽直接决定了锁定时间。

环路带宽越大,锁定时间越短,反之,锁定时间越长。频率跳变的大小也决定了锁定时间。频率跳变越大,锁定时间越长,反之,锁定时间越短。

可以用一锁相单环对这几个公式进行简单的验证,如图1 所示,锁相单环的鉴相频率从625 MHz 跳到1 250 MHz,环路分频比为8,VCO输出从5 GHz向10 GHz跳频,设定环路的自然谐振频率为ωn = 2π × 9 × 106 rad/s,相位余量为48°,终锁定频差为100 kHz,则可近似计算得到理想条件下整个环路的跳频时间T = Tf + Tl≈1 140 ns,实测为1.65 μs,考虑到非理想因素,二者相符度较高。

除了环路带宽和频率跳变大小,锁相环中的其他组件性能也对锁定时间产生直接影响,如鉴相频率,运放电压建立速度,VCO 的置频速度,以及分频器、放大器等器件延时等。鉴相器的选择要鉴相频率较高,因为鉴相频率决定了反馈分频和参考频率的比较速度,减小了鉴相延时;VCO的选择要电调速度快,运放的选择要转换速度快和增益带宽积高,其他器件的选择也要有较高的速度。

虽然采用鉴频鉴相器,并选用高速组件的锁相环也可实现数微秒的频率捷变,但是想要跳频时间达到1 μs还必须应用下一节中提到的电压预置方法,另外使频率分辨率达到1Hz还必须使用DDS,优化输出信号的杂散和相噪考虑使用环内混频,并使用低相噪的晶振和VCO.

2 电压预置法原理及具体实现

电压预置法由于其实现简单、效果明显等优点,现在被普遍用来提高锁相环的跳频速度。这种方法的基本思路是:通过给VCO提供一个很高的调谐电压,使得锁相环的起始频差能减小到快捕带,从而实现快速锁定。在实际应用中,考虑到VCO 等器件是温度敏感元件,并且压控灵敏度非常高,次预置可能会有较大误差,为了预置电压尽量,还需进行修正。

修正即是对VCO 反馈频率进行f/D 变换(即频率-数字变换),将它与预先已知的输出频率的标准参考量值相比较得出两者差值,再乘上和压控灵敏度相关的系数,以此修正VCO 电压预置,从而实现VCO 的调谐。

由于本方案对时间要求比较高,只进行修正,在跳变频率步进很小时也可不必修正。

3 捷变频设计方案

根据以上原理和方法,设计了如图2 所示的方案,目的为研制1.15~20 GHz 的宽频带小型锁相频率源,要求输出频率分辨率为1 Hz,全频带范围内频率跳变时间在1 μs左右。如图2所示,方案的主体为由鉴频鉴相器、环路滤波器、VCO、混频器、N 分频器组成的混频锁相环,鉴频鉴相器的细分辨参考fR 由DDS通过混频滤波提供,环内混频本振fM 由细分辨参考电路中某一频率的谐波提供,在VCO压控端使用了电压预置和f/D变换电路,由M 分频器、FPGA、D/A等组成,电压相加器将预置电压和环路电压相加后送入VCO,控制系统由FPGA、数据存储芯片以及接口电路构成。

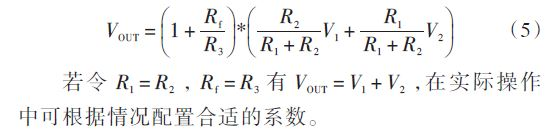

由于电压预置和环内混频,VCO 的前端电路需要特别的设计,如图3所示,包括加法电路和防失锁电路,防失锁的原理将在第5节中介绍。加法电路采用正相放大接法:

若令R1 = R2 ,Rf = R3 有VOUT = V1 + V2 ,在实际操作中可根据情况配置合适的系数。

4 方案锁定时间分析

利用锁定时间的计算公式对本方案不加预置的环路进行估算,VCO 输出10 GHz向20 GHz跳频,鉴相频率500 MHz跳到1 000 MHz,设定环路自然谐振频率为ωn = 2π × 10 × 106 rad /s ,相位余量仍然为48°,锁定频差100 kHz,近似计算的锁定时间为T ≈ 700 ns,若再使用电压预置,将起始频差直接送入快捕带内,不考虑环路器件延迟,则极限情况下可获得只有100 ns 的跳频时间。

由于方案中环路内使用的器件均工作在数个GHz的频率上,都只有数ns的延迟,所使用的运放也具有高的转换速率和高的增益带宽积,转换速率高达400 V/μs,在50 ns之内就可以上升20 V.环路内的器件总延时时间小于200 ns.电压预置及修正反馈电路引入了f/D变换时间、DAC和加法器响应时间,整个时间可在150 ns之内完成。

环路外围电路包括细分辨参考电路和混频谐波本振产生电路,通过选取高速并行DDS,高速开关等高速器件,可以实现快速配置。从跳频指令发出,到DDS提供细分辨参考给鉴相器时间小于400 ns,在鉴相参考频率完成配置的同时可实现混频谐波本振产生及电压预置的配置到位,即在400 ns时间内完成细分辨参考,混频谐波产生和预置电压的配置。

由上面的计算可以看到,采用电压预置后即使加上非理想情况以及电压修正时间,以及各部分的延时也可实现1μs左右的全频带跳频。

5 若干问题讨论

5.1 环内混频的失锁现象应对

在本方案的混频环中,VCO反馈频率频带较宽,参与谐波混频的频率较多。若预置控制输出与参与混频频率控制输出完全同步,即在预置电压给出控制VCO振荡并分频到达混频器的同时,谐波控制选择相应频率也同时到达混频器,则环路工作完全正常,不存在失锁现象,但是实际中二者不可能完全同步,这就存在以下两种情况。设从VCO到混频器的频率从f1 到f2 ,对应混频本振为fL1 和fL2 ,鉴相频率fR ,fVCO反馈> f混频本振为正确的锁相模式,如图4所示。

(1)混频本振控制先到混频器,即fL2 先与f1 混频。若 | f1 | - fL2 ≤ max( fR ) ,鉴相器正常工作,但是VCO输出频率被错误牵引,在f2 到达混频器时,进入正常捕获;若fL2 - f1 > max( fR ) ,鉴相器不能正常工作,信号不被识别,经比相后输出Vp 升高,f1 变大,fL2 - f1 变小,终重新进入鉴相区;若f1 - fL2 > max( fR ) ,f1 变大,f1 - fL2 继续变大,频率被越拉越远,VCO 达到频率,即使此时f2 到达,也无法重新拉回鉴相区,造成环路失锁。

(2)VCO 反馈频率先到,即f2 先与fL1 混频。当f2 - fL1 > max( fR ) 时,与上面类似,环路失锁。

为解决这个问题,采用了电压箝位电路,对VCO的压控电压进行限制,使得任意混频后的频率都位于鉴相频率范围内,这样环路才能够正确锁定。每个混频本振对应一个电压范围值,这个电压可用稳压二极管来实现,电压预置时同时切换开关选择对应的稳压二极管实现箝位。

5.2 f/D 变换

对于修正的要求是:修正时间要快,要比通过环路积分修正的速度快;修正小于5%.在实际计数操作时,采用等测量方法。它的闸门时间不是固定的,而是被测信号周期的整数倍,即与被测信号同步。在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号,此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才开始计数。然后预置闸门关闭信号到来时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成测量过程。其原理时序如图5 所示。设实际闸门时间为t ,标准信号频率为fs ,则测量频率的相对误差为δ ≤ 1/ (t - fs) .以fs = 200 MHz,被测信号为20 MHz为例,设定实际闸门时间为100 ns,则测量频率误差为δ ≤ /1 (t - fs) = 1 (100 ns × 200 MHz)=5%,满足要求。

6 结论

本文研究的捷变频方案,主环路采用了电压预置并反馈修正的方式,将锁相环的起始频差迅速拉入鉴频鉴相器的锁定带内,减小了锁定时间;锁相组件使用了高度运放、鉴频鉴相器等高速器件,外围电路中使用了并行DDS、高速D/A、高速开关等器件减小了系统延时,实现了快速锁定。从理论和分步实验结果来看,可以实现1 μs左右的跳频。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。