摘要:传统的微处理器由于内部有限的逻辑资源和外部固定的引脚封装,大大限制了应用范围。为此,在阐述微控制器的内部结构、存储器管理结构和指令集结构后,利用现场可编程门阵列丰富的逻辑资源,虚拟出传统微控制器的处理器,添加Wishbone总线,将处理器与通用外设连接构成一个虚拟的微控制器平台,并使用硬件描述语言Verilog和VHDL,自底向上设计AVR处理器,与通用外设互连组成系统,使用XILINX Virtex-Ⅱ Pro芯片进行板级验证。

0 引言

随着社会发展,工业控制及人们日常生活越来越追求精密控制,为满足这种需求,微控制器得到了快速发展。微控制器(Micro Control Unit,MCU)又称单片微型控制计算机或单片机。随着大规模集成电路(LargeScale Integration,LSI)发展,MCU将原本分散的中央处理器(Central Processor Unit,CPU)、随机存储器(Ran-dom Access Memory,RAM)、只读存储器(Read OnlyMemory,ROM)、输入/输出接口(In/Out Ports,I/O)等集中于一块单晶芯片内,形成一种芯片级计算系统。MCU主要用于控制,MCU构成的系统有实时、快速的外部响应,能迅速采集到大量数据,做出逻辑判断与推理后实现对被控制对象的参数调整与控制。但是随着对控制的要求增大,传统MCU也越来越显得捉襟见肘。为此使用专用应用集成电路(Application Specific IntegratedCircuit,ASIC)器件在片内实现与传统MCU相兼容的,选用合适的片内总线来连接外设,构成一个兼容传统MCU平台,这种方法必会延续传统MCU的生命力,使其获得更大的发展。

1 MCU 简介

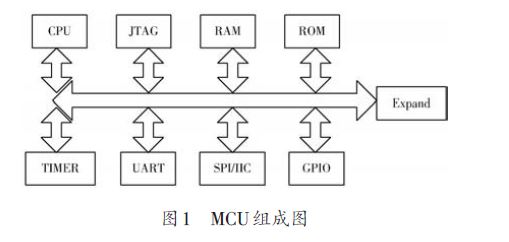

若将4位单片机的出现作为MCU的起点,MCU的发展大致可以分为如下阶段:初级阶段(1971年-1976年)、8 位低性能阶段(1976 年-1980 年)、8 位高性能阶段(1980年-1983年)、16位阶段(1983年至80年代末)、片上系统(System On-Chip,SoC)阶段(1990-)。一个通用的MCU 由ROM、RAM、GPIO、串行设备(UART/SPI/IIC)、计数器/定时器(TIMER)等组成,并通过总线连接,如图1所示。

传统MCU 都需要一套指令集结构(Instruction SetArchitecture,ISA)。从现阶段主流体系结构讲,主要分为复杂指令集(Complex Instruction Set Computer,CISC)和精简指令集(Reduced Instruction Set Computer,RISC)。

RISC增加了运行速度,大大减小了指令集数目,方便使用多级流水线结构,可增加寄存器数量。AVR单片机就是一款内置FLASH的增强型RISC处理器[4].

另外MCU需要将数据和指令存储于存储器中。目前使用多的两种存储器组织结构分别为冯·诺依曼结构(Von Neumann Architecture)和哈佛结构(Harvard Ar-chitecture)。冯·诺依曼结构将处理器指令和数据合并在一起存储,指向同一存储器的不同物理地址。哈佛结构将程序指令存储和数据存储分开,中央处理器先从程序指令存储器中获得指令译码后得到数据地址,再由此从数据存储器中取得数据,并进行下一步操作。哈佛结构的微处理器通常有很高的执行效率。Atmel公司的AVR系列就是采用的哈佛结构。

AVR单片机是由Atmel公司在1997年推出的高速8位MCU,内置FLASH的增强型RISC处理器,可广泛应用于计算机外部子系统、工业生产和控制、仪器仪表、通信设备、家用电器等各个领域。大部分AVR片上资源丰富:如E2PROM,PWM,RTC,SPI,USART,TWI,ISP,AD,Analog Comparator,WDT等。AVR单片机内嵌高质量的FLASH程序存储器,擦写方便,支持ISP和IAP,便于产品的调试、开发、生产、更新。内嵌长寿命的E2PROM可长期保存关键数据,避免断电丢失。片内大容量的RAM不仅能满足一般场合的使用,同时也更有效地支持使用语言开发系统程序,并可像8051单片机那样扩展外部RAM.

2 FPGA 简介

ASIC 是指依特定用途而设计的特殊规格逻辑电路。ASIC的显着特点是面向特定用户需求,与通用集成电路相比有更小的体积、更低的功耗、较高的可靠性、较强的保密性和低成本等优点,但因为开发较为复杂,所以研发周期较长。

随着电子工业技术的发展,ASIC的设计方法变得越简单,效率越高,可编程ASIC就是一个很有特色的设计分支,它主要利用可编程的集成电路如PLD(Program-mable Read Only Memory)等可编程逻辑电路来设计。

主要特点是直接提供软件设计编程,完成ASIC电路功能,而不再通过集成电路工艺加工后得到成品。这种方法大大降低了开发周期,且缩小了成本。

现场可编程门阵列(Field Programmable Gate Ar-ray,FPGA)就是众多PLD产品中应用为广泛的一种,它采用了逻辑单元阵列(Logic Cell Array,LCA),内部包含了可配置的逻辑模块(Configurable Logic Block,CLB)、输入/输出模块(Input Output Block,IOB)和内部连线(Interconnect)。FPGA采用的是小型查找表来实现组合逻辑的,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他的逻辑电路或者I/O,由此构成即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,通过内部连线互相连接。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O之间的联系方式,并且终决定了FPGA所实现的功能。由于FPGA采用查找表结构,而查找表本质是一个小RAM,所以FPGA内部信息掉电消失,上电需要重新进行配置。FPGA支持多次重复编程。相对于其他的可编程器件,FPGA是ASIC电路中设计风险、开发费用、周期短的器件之一。采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。同时FPGA 的内部逻辑和I/O 资源非常丰富,可以说用FPGA芯片进行小批量生产,对于提高系统集成度、可靠性是很有帮助的。

在众多PLD厂家中,XILINX公司的产品种类丰富,其开发工具ISE为业界公认的的开发工具之一,且其芯片的性价比很高。所以,这里主要使用XILINX公司的产品。XILINX 公司主要FPGA 产品为SPARTAN系列和VIRTEX系列。前者面向低成本应用,满足一般的逻辑设计要求,后者面向高性能应用,满足高端要求。文中选择Virtex-Ⅱ Pro 系列芯片作为开发平台。

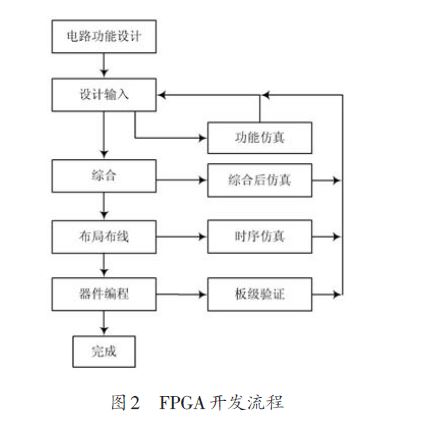

这款芯片含有可编程输入/输出块、可配置逻辑块、嵌入式RAM块、数字时钟管理模块、专用硬核以及丰富的布线资源。FPGA的设计过程是利用EDA工具将设计输入转化为FPGA芯片可运行的过程,开发的一般流程见图2.

3 Virtual AVR 实现

通过对FPGA和MCU的深入了解,可知使用FPGA的丰富资源来虚拟出MCU是完全可行的。首先,需设计一个总体结构,如图3所示。ROM用于存放被执行程序及二进制代码,RAM 为运行内存,用总线将VirtualMCU Core与各外设相连。使用该结构可简化设计,无需对外设重复设计,只要使Virtual MCU Core满足同一接口即可。

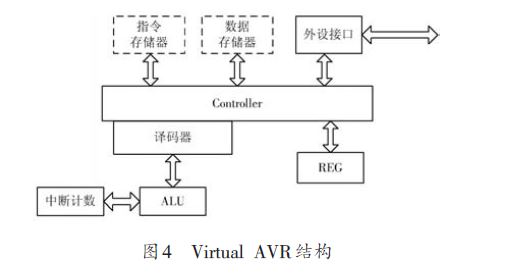

Virtual MCU Core由几部分构成:算术逻辑单元,运算的主要单元;译码器,由二进制文件判断指令类型并获得源操作数和目的操作数等;寄存器,用于参加运算和存储某些中间值等。

Virtual AVR Core 以ATmega103处理器为参考,采用RISC结构,3级流水线结构,因为是哈佛结构,所以分为数据存储器和指令存储器。它的处理器如图4所示。同时ATmega103共有130条指令,每条指令都是固定结构,为16 位。在该设计中,移植了Open-Cores开源组织的8位AVR核,它支持3级流水线,兼容标准AVR微处理器。

ALU的实现采用模块化设计,共分为控制模块、加减法模块和乘除法模块。3级流水线设计如下:

stage0:FETCH,给出指令地址,并读取相应的指令,主要由译码机构负责;stage1:ALU/MEM,ALU运算,或数据存储器操作,读数据存储器时,在地址总线上给出正确的值,当写数据存储器时,不仅需要提供正确的地址,还需要在数据总线上提供正确的数据,主要由运算机构和总线控制机构负责。

Stage2:LOAD,从数据线上获取数据,存至寄存器中,主要由寄存器机构负责。

在一个系统中光有处理器是不够的,需要有丰富的外设来满足各种控制要求或数据传输功能,而片内总线便是将处理器与总线连接的重要途径。文中采用Sili-core的Wishbone总线进行设计,具有简单、开放、高效和方便实现等特点,且完全开放并没有保护。Wish-bone有四种连接模式:点对点、数据流、共享总线和十字交叉互联。文中使用共享总线连接方式,其中充当Master为Virtual Core,而外设为Slaver.

为使Virtual Core能与外部器件进行通信,需要外设的支持。外设按数据流类型分为串行和并行,常用的串行外设有SPI、I2C、UART 等,常用的并行外设有GPIO等。

4 硬件支持与测试

硬件环境主要分为两部分:部分为板,用以支持Virtex-Ⅱ Pro的运行;第二部分为底板,主要为添加外设环境,丰富系统的功能。选用XC2VP50FFG1152芯片作为的FPGA,在外围又添加了DDR和SDRAM,方便自由选择存储器类型。FP-GA掉电后,内容自动消失,每上电需要重新配置,为让FPGA 上电后自动配置,需加一片PROM,使用XCF32P.FPGA采用并行主模式。底板上则是增加大量外设:UART、PS2、VGA、ETHERNET、VIDEO、A/D、D/A、SD、USB等。

Virtual Core执行的程序都是固化在ROM中,为达到测试要求,要多次更新ROM中内容,为此使用嵌入式开发套件(Embedded Development Kit,EDK)来开发一个测试工具。首先将BRAM配置为双端口RAM,一端口给Virtual Core来进行读取操作,一端口给EDK,来更新程序存储器。同时EDK也可提供简单的控制任务,如重启Virtual Core 等,EDK 使用UART 和计算机进行操作。为方便控制,设计一个较为简单的PC端串口程序,用于将EDK与PC交互,主要是将用户的命令或文件经串口发送至EDK,如图5所示。搭建一个简易测试系统,使用ISE工具,进行综合布局布线,其资源消耗如图6所示。编写一个跑马灯程序,代码如下:

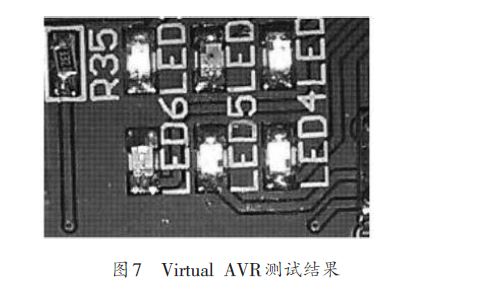

使用WINAVR-GCC 编译工具,编译生成HEX 文件,后再转化为BIN文件,将该BIN文件通过EDK组建更新ROM,观察硬件LED,如图7所示,其正常工作,Vir-tual AVR得到验证。

5 结语

随着MCU 应用范围越来越宽,对MCU 要求也提高,尤其目前MCU逐渐进入SoC时代,IP核复用将成为主流设计方法。为使老一代MCU延续生命力,开发其兼容IP核,不仅能将以往代码迅速移植到新系统,且可加快新系统开发,将以往很多分立器件用逻辑功能实现,集成于ASIC中,降低外围硬件电路的设计。文中从模拟MCU核开始,阐述了用FPGA来虚拟出传统MCU的设计原理和方法,适度改变内部结构,添加Wishbone总线,替代传统MCU片内总线,来完成MCU核与外设的连接,使传统MCU变的更灵活。结果表明,实现了既定目标,与标准的微控制器兼容,系统运行稳定。该方法延续了传统微控制器的生命力,能使其得到更大发展。由于Wishbone总线支持多主设备,今后可在一个FPGA 中集成多个MCU核,对于性能的提升将是质的飞跃。(作者:张益男,何菁,袁杰)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。