新型的高速ADC都具备高模拟输入带宽(约为采样频率的3到6倍),因此它们可以用于许多欠采样应用中。ADC设计的进展极大地扩展了可用输入范围,这样系统设计人员便可以去掉至少一个中间频率级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR)的主要原因。

本系列文章共有三部分,"第1部分"重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与ADC的孔径抖动组合。在"第2部分"中,该组合抖动将用于计算ADC的SRN,然后将其与实际测量结果对比。"第3部分"将介绍如何通过改善ADC的孔径抖动来进一步增加ADC的SNR,并会重点介绍时钟信号转换速率的优化。

采样过程回顾

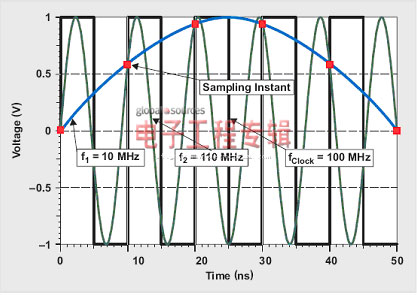

根据Nyquist-Shannon采样定理,如果以至少两倍于其频率的速率来对原始输入信号采样,则其可以得到完全重建。假设以100 MSPS的速率对高达10MHz的输入信号采样,则不管该信号是位于1到10MHz的基带(Nyquist区域),还是在100到110MHz的更高Nyquist区域内欠采样,都没关系(请参见图1)。在更高(第二个、第三个等)Nyquist区域中采样,一般被称作欠采样或次采样。然而,在ADC前面要求使用抗混叠过滤,以对理想 Nyquist 区域采样,同时避免重建原始信号过程中产生干扰。

图1:100MSPS采样的两个输入信号显示了混叠带来的相同采样点

时域抖动

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高Nyquist区域(例如,f1 = 10 MHz到f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。另外,图2表明时钟信号自身转换速率对采样时间的变化产生了影响。转换速率决定了时钟信号通过零交叉点的快慢。换句话说,转换速率直接影响ADC中时钟电路的触发阈值。

图2:时钟抖动形成更多快速输入信号振幅误差

如果ADC的内部时钟缓冲器上存在固定数量的热噪声,则转换速率也转换为计时不准,从而降低了ADC的固有窗口抖动。如图3所示,窗口抖动与时钟抖动(相位噪声)没有一点关系,但是这两种抖动分量在采样时间组合在一起。图3还表明窗口抖动随转换速率降低而增加。转换速率一般直接取决于时钟振幅。

图3

时钟抖动导致的SNR减弱

有几个因素会限制ADC的SNR,例如:量化噪声(管线式转换器中一般不明显)、热噪声(其在低输入频率下限制SNR),以及时钟抖动(SNRJitter)(请参见下面方程式1)。SNRJitter部分受到输入频率fIN(取决于Nyquist区域)的限制,同时受总时钟抖动量tJitter的限制,其计算方法如下:

正如我们预计的那样,利用固定数量的时钟抖动,SNR随输入频率上升而下降。图4描述了这种现象,其显示了400 fs固定时钟抖动时一个14位管线式转换器的SNR.如果输入频率增加十倍,例如:从 10MHz增加到100MHz,则时钟抖动带来的实际SNR降低20dB.

图4

如前所述,限制ADC SNR的另一个主要因素是ADC的热噪声,其不随输入频率变化。一个14位管线式转换器一般有~70到74 dB的热噪声,如图4所示。我们可以在产品说明书中找到 ADC的热噪声,其相当于指定输入频率(本例中为 10MHz)的SNR,其中时钟抖动还不是一个因素。

让我们来对一个具有400 fs抖动时钟电路和~73 dB热噪声的14位ADC进行分析。低输入频率(例如:10MHz 等)下,该ADC的SNR主要由其热噪声定义。由于输入频率增加,400-fs 时钟抖动越来越占据主导,直到~300 MHz 时完全接管。尽管相比10MHz的SNR,100MHz输入频率下时钟抖动带来的SNR每十倍频降低20dB,但是总SNR仅降低~3.5 dB(降至69.5dB),因为存在73-dB热噪声(请参见图5):

图5:产生的ADC SNR受热噪声和时钟抖动的限制

现在,很明显,如果ADC的热噪声增加,对高输入频率采样时时钟抖动便非常重要。例如,一个16位ADC具有~77到80 dB的热噪声层。根据图4所示曲线图,为了化100MHz输入频率SNR的时钟抖动影响,时钟抖动需为大约150 fs或更高。

确定采样时钟抖动

如前所述,采样时钟抖动由时钟的计时不准(相位噪声)和ADC的窗口抖动组成。这两个部分结合组成如下:

我们在产品说明书中可以找到ADC的孔径口抖动(aperture jitter)。这一值一般与时钟振幅或转换速率一起指定,记住这一点很重要。低时钟振幅带来低转换速率,从而增加窗口抖动。

时钟输入抖动

时钟链(振荡器、时钟缓冲器或PLL)中器件的输出抖动一般规定在某个频率范围内,该频率通常偏离于基本时钟频率10 kHz到20 MHz(单位也可以是微微秒或者绘制成相位噪声图),可以将其整合到一起获取抖动信息。但是,低端的10kHz和高端的20MHz有时并非正确的使用边界,因为它们调试依赖于其他系统参数,我们将在后面进行详细介绍。图6描述了设置正确整合限制的重要性,图中的相位噪声图以其每十倍频抖动内容覆盖。我们可以看到,如果将下限设定为100-Hz或10kHz偏移,则产生的抖动便极为不同。同样地,例如,设置上整合限制为10或20MHz,可得到相比100MHz设置极为不同的结果。

图6:每十倍频计算得到的时钟相位噪声抖动影响

确定正确的整合下限

在采样过程中,输入信号与采样时钟信号混频在一起,包括其相位噪声。当进行输入信号FFT分析时,主FFT容器(bin)集中于输入信号。采样信号周围的相位噪声(来自时钟或输入信号)决定了邻近主容器的一些容器的振幅,如图7所示。因此,小于1/2容器尺寸的偏频的所有相位噪声都集中于输入信号容器中,且未增加噪声。因此,相位噪声整合带宽下限应设定为1/2 FFT容器尺寸。 FFT容器尺寸计算方法如下:

图7:近区相位噪声决定主容器附近FFT容器的振幅

为了进一步描述该点,我们利用两个不同的FFT尺寸-131,072和1,048,576点,使用ADS54RF63进行实验。采样速率设定为 122.88MSPS,而图8则显示了时钟相位噪声。我们将一个 6-MHz、宽带通滤波器添加到时钟输入,以限制影响抖动的宽带噪声数量。选择1-GHz输入信号的目的是确保SNR减弱仅由于时钟抖动。图8表明两个FFT尺寸的1/2容器尺寸到 40MHz 相位噪声整合抖动结果都极为不同,而"表 1"的 SNR测量情况也反映这种现象。

图8

设置正确的整合上限

图6所示相位噪声图抖动贡献量为~360 fs,其频率偏移为10到100MHz之间。这比100Hz到10MHz之间偏移的所有~194 fs抖动贡献值要大得多。因此,所选整合上限可极大地影响计算得到的时钟抖动,以及预计SNR匹配实际测量的好坏程度。

要确定正确的限制,您必须记住采样过程中非常重要的事情是:来自其他尼奎斯特区域的时钟信号伪带内噪声和杂散,正如其出现在输入信号时表现的那样。因此,如果时钟输入的相位噪声不受频带限制,同时没有高频规律性衰减,则整合上限由变压器(如果使用的话)带宽和ADC自身的时钟输入设定。一些情况下,时钟输入带宽可以非常大;例如,ADS54RF63具有~2 GHz的时钟输入带宽,旨在允许高时钟转换速率的高阶谐波。

若想要验证时钟相位噪声是否需要整合至时钟输入带宽,则需建立另一个实验。ADS54RF63再次工作在122.88 MSPS,其输入信号为1GHz,以确保SNR抖动得到控制。我们利用一个 RF放大器,生成50MHz到1GHz的宽带白噪声,并将其添加至采样时钟,如图9所示。之后,我们使用几个不同低通滤波器 (LPF) 来限制添加至时钟信号的噪声量。

图9

ADS54RF63的时钟输入带宽为~2 GHz,但由于RF放大器和变压器都具有~1 GHz的3-dB带宽,因此有效3-dB时钟输入带宽被降低至~500 MHz."表 2"所示测得SNR结果证实,就本装置而言,实际时钟输入带宽约为500MHz.图10所示FFT对比图进一步证实了RF放大器的宽带噪声限制了噪声层,并降低了SNR.

图10

该实验表明,时钟相位噪声必需非常低或者带宽有限,较为理想的情况是通过一个很窄的带通滤波器。否则,由系统时钟带宽设定的整合上限会极大降低ADC的SNR.

结论

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。"第2部分"将会介绍如何使用这种估算方法来推导ADC的SNR,以及所得结果与实际测量结果的对比情况。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。