在科技发达的当今,各种信号出现在我们生活周围,当然我们看不到也摸不着。其实我们通常认为信号以三种模式沿电路传播:单端、差模或共模。

单模是我们熟悉的。它包括介于驱动器与接收器之间的单根导线或走线。信号沿走线传播并从地返回。

差模包括介于驱动器与接收器的一对走线(或导线)。我们一般认为其中一根走线传送正信号而另一根传送负信号,并且大小相等极性相反,没有通过地的返回信号;信号沿一根走线前进并从另外一根返回。

共模信号通常更难于理解。既可以包括单端走线也可以包括两个或更多差分走线。同样的信号沿走线以及返回路径地或者沿差分对中的两根走线流动。大部分人往往对共模信号不熟悉,因为我们自己从来不会故意产生它们。它们通常是由从其它源耦合进电路的噪声引起的。一般来讲,结果情况是中性的,坏情况是具有破坏性的。共模信号能够产生干扰电路正常运行的噪声,并且是常见的EMI 问题的来源。

优缺点

差分信号与传统的一根信号线一根地线(即单端信号)走线的做法相比,其优缺点分别是:

优点:

1、抗干扰能力强。干扰噪声一般会等值、同时的被加载到两根信号线上,而其差值为0,即,噪声对信号的逻辑意义不产生影响。

2、能有效抑制电磁干扰(EMI)。由于两根线靠得很近且信号幅值相等,这两根线与地线之间的耦合电磁场的幅值也相等,同时他们的信号极性相反,其电磁场将相互抵消。因此对外界的电磁干扰也小。

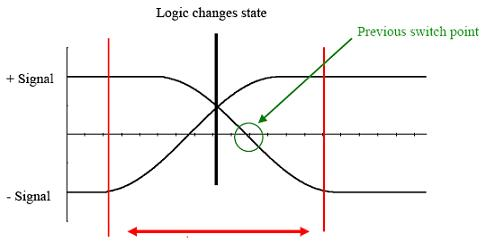

3、时序定位准确。差分信号的接受端是两根线上的信号幅值之差发生正负跳变的点,作为判断逻辑0/1跳变的点的。而普通单端信号以阈值电压作为信号逻辑0/1的跳变点,受阈值电压与信号幅值电压之比的影响较大,不适合低幅度的信号。

缺点:

若电路板的面积非常紧张,单端信号可以只有一根信号线,地线走地平面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。这样的情况常常发生在芯片的管脚间距很小,以至于只能穿过一根走线的情况下。

图1:逻辑电平在差分信号交叉点的位置改变状态

重要假设

差分信号的一个重要方面常常被工程师或者设计人员忽略,甚至有时被误解。我们从两条广为人知的规则开始:一条是电流在一个闭合的环路内流动,另一条是电流在环路内处处相等。

考虑差分对的“正”走线。电流沿走线流动并且必须在一个环路内流动,通常从地返回。另外一根走线中的负信号也必须在一个环路内流动,通常也从地返回。这很容易明白如果我们暂时想象一个差分对中的一根走线上的电流保持不变。另一根走线中的信号必须从某个地方返回,并且很清楚返回路径应该是单端信号的返回路径(地)。我们说差分对没有通过地的返回信号不是因为不能,而是因为返回信号的确存在并且大小相等且极性相反所以相互抵销了(和为零)。

这一点非常重要。如果从一个信号(+i)返回的信号严格等于,且符号相反,另一个信号(-i),那么它们的和(+i-i)为零,没有电流从任何地方流过(特别是地)。现在假定信号并非严格相等且极性相反。设一个为+i1 另一个为-i2。这里i1 和i2 的值近似但是不等。返回电流的和为(i1-i2)。因为不是零,这个增加的电流必须从某个地方返回,推测应该是地。

你说什么?那么让我们假定发送电路发送一对差分信号,严格相等且极性相反。再假定他们在路径的终点仍然如此。但是如果路径长度不等会如何呢?如果(差分对中的)一条路径比另外一条长,那么信号在传输到接收器的阶段就不再是严格相等且极性相反了(图2)。如果信号在它们从一个状态到另一个状态的转变过程中不再是严格相等且相反,没有电流流经地就不再是正确的了。如果有流经地的电流存在,那么电源完整性就一定成为一个问题,并且可能EMI也会成为一个问题。

图2:(-)走线比图1 中短,在红色箭头所标示出的范围内差分信号是大小相等且极性相反不再正确。从而在这个时间片内将有流经电源系统的电流。

设计规则1

我们处理差分信号的个规则是:走线必须等长。

有人激烈地反对这条规则。通常他们的争论的基础包括了信号时序。他们详尽地指出许多差分电路可以容忍差分信号两个部分相当的时序偏差而仍然能够可靠地进行翻转。根据使用的不同的逻辑门系列,可以容忍500 mil 的走线长度偏差。并且这些人们能够将这些情况用器件规范和信号时序图非常详尽地描绘出来。问题是,他们没有抓住要点!差分走线必须等长的原因与信号时序几乎没有任何关系。与之相关的仅仅是假定差分信号是大小相等且极性相反的以及如果这个假设不成立将会发生什么。将会发生的是:不受控的地电流开始流动,情况是良性的,坏情况将导致严重的共模EMI问题。

因此,如果你依赖这样的假定,即:差分信号是大小相等且极性相反,并且因此没有通过地的电流,那么这个假定的一个必要推论就是差分信号对的长度必须相等。

差分信号与环路面积:如果我们的差分电路处理的信号有着较慢的上升时间,高速设计规则不是问题。但是,假设我们正在处理的信号有着有较快的上升时间,什么样的额外的问题开始在差分线上发生呢?

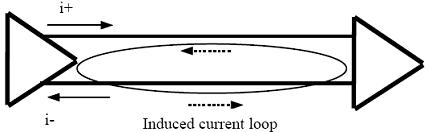

考虑一个设计,一对差分线从驱动器到接收器,跨越一个平面。同时假设走线长度完全相等,信号严格大小相等且极性相反。因此,没有通过地的返回电流。但是,尽管如此,平面层上存在一个感应电流!

任何高速信号都能够在相邻电路产生一个耦合信号。这种机制与串扰的机制完全相同。这是由电磁耦合,互感耦合与互容耦合的综合效果,引起的。因此,如同单端信号的返回电流倾向于在直接位于走线下方的平面上传播,差分线也会在其下方的平面上产生一个感应电流。但这不是返回电流。所有的返回电流已经抵消了。因此,这纯粹是平面上的耦合噪声。问题是,如果电流必须在一个环路中流动,剩下来的电流到哪里去了呢?

记住,我们有两根走线,其信号大小相等极性相反。其中一根走线在平面一个方向上耦合了一个信号,另一根在平面另一个方向上耦合了一个信号。平面上这两个耦合电流大小相等(假设其它方面设计得很好)。因此电流完全在差分走线下方的一个环路中流动(图3)。它们看上去就像是涡流。耦合电流在其中流动的环路由差分线自身和走线在每个端点之间的间隔来定义。

图3:即使差分信号严格大小相等且极性相反,因而没有流经电源系统的返回电流,仍然在走线下方的平面中存在在一个环路中流动的感应电流。

设计规则2

现在EMI 与环路面积已是广为人知了3。因此如果我们想控制EMI,就需要将环路面积化。并且做到这一点的方法引出了我们的第二条设计规则:将差分线彼此靠近布线。有人反对这条规则,事实上这条规则在上升时间较慢并且EMI 不是问题时并不是必须的。但是在高速环境中,差分线彼此靠得越近布线,走线下方所感应的电流的环路就越小,EMI 也可以得到更好的控制。

值得一提的是一些工程师要求设计人员去掉差分线下方的平面。原因之一是减小或消除走线下方的感应电流环路。另外一个原因是防止平面上已有的噪声耦合到(推测如此)走线上的低压信号4。

还有一个将差分线彼此靠近布线的理由。差分接收器设计为对输入信号的差敏感而对输入的共模偏移不敏感。也就是说即使(+)输入相对(-)输入仅有轻微的偏移,接收器也会检测到。但是如果(+)和(-)输入一起偏移(在同样的方向),相对而言接收器对这种偏移不敏感。因此如果任何外部噪声等同地耦合到差分线中,接收器将对此种噪声不敏感。差分线布得越彼此靠近,任何偶合噪声在每根走线上就越相近。因此电路的噪声抑制就越好。

规则2推论

再次假定高速环境中,如果差分线彼此紧挨着布线(为了使其下方的环路面积化)那么走线将彼此耦合。如果走线足够长以至于端接成为一个问题,这种耦合就会影响到确切的端接阻抗5的计算。原因是:

考虑一个差分线对,线1 和线2。假使它们分别携带信号V1 和V2。因为它们是差分线,V2=V1。V1 在线1 引起一个电流I1 而V2在线2 引起一个电流I2。电流必然是从欧姆定律导出,I=V/Z0,这里Z0 是走线的特征阻抗。现在线1(举例)携带的电流事实上由i1 和k*i2 组成,这里k 是线1 与线2 间的耦合比例。这表明这种耦合的终效果是线1 上的一个明显的阻抗,这个阻抗等于Z=Z0-Z12

这里Z12 由线1 与线2 间的互耦6引起。如果线1 和线2 分得很开,它们之间的耦合就很小,确切的端接阻抗就只是Z0,单端走线的特征阻抗。但是如果走线靠的更近,它们之间的耦合就会增加,这样走线的阻抗与这种耦合成比例地减小。这就是说确切的走线端接(为了防止反射)为Z0-Z12,或者某个小于Z0 的值。这对差分对的两根走线都适用。因为没有流经地的电流(大概这是个假设)那么端接电阻被连接在线1 和线2 之间,且确切的端接阻抗算得是2(Z0-Z12)。这个值经常被叫做“差分阻抗”7。

设计规则3

差分阻抗因互耦而变,而互耦因线距而变。因此在任何情况下,走线阻抗,也就是互耦,在全线为常数是很重要的。这就得到了我们的第三个规则:(差分对的)线距必须在全线为常数。

注意对差分阻抗的影响只是规则2 的推论。差分阻抗根本不是与生俱来的。我们要把差分线彼此靠近布线与EMI 和噪声免疫有关。它对“长”线确切端接以及线距一致性的影响的事实只不过是为了EMI 控制而将走线彼此靠近布线的一个推论8。

结论

差分信号有几个优点,它们中的三个是与电源系统有效隔离,对噪声免疫和增强信噪比。与电源系统隔离依赖于差分线上的信号真正地大小相等且极性相反。这个假定也许不成立,如果差分对中单个线长不完全匹配。对噪声的免疫经常依赖于走线的紧耦合。这将依次影响到为防止反射而对走线进行正确的端接的值,以及如果走线必须紧耦合,通常也是需要的,它们的间距必须全线为常数。

参考

1 事实上信号可以仅仅/同时从地或电源系统返回。在这篇文章中我通篇使用单个术语“地”完全是为了方便。

2 光耦器件是解决这类问题的另一种方法。

3 参见"Loop Areas: Close 'Em Tight", January, 1999

4 据我所知没有权威的研究支持或者反驳这个惯例。

5 阻抗控制走线在行业中有许多参考。比如,参见"PCB Impedance Control: Formulas and Resources", March, 1998; "Impedance Terminations: What's the Value?" March, 1999; 和"What Is Characteristic Impedance" by Eric Bogatin, January, 2000, 第18 页。

6 参见"Differential Impedance: What's the Difference", August, 1998

7 对线对的差模及共模成分的有趣讨论,参见"Terminating Differential Signals on PCBs",Steve Kaufer and Kellee Crisafalu, March, 1999, 第25 页。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。