线性稳压器通常被设计工程师作为辅助措施 ,并且经常被选用于产品开发的后期阶段。设计工程师比较关注的是如何使复杂的基频(BB) 或射频( RF )ASIC 发挥作用,而不是其所选线性稳压器的功率/性能。线性稳压器的选择依据通常性能列表中的主要规格,而不是位于数据表封面以内的非常关键的和性能参数。规格经常很容易令人误解 - 封面上所列的规格只代表主要参数,但如果不与其他连接参数相结合时,便失去了价值。

每种线性稳压器都有各自的优缺点,终得由设计师根据压差、接地电流和稳定性补偿方法等要求,确定某种类型稳压器是否适合设备使用。电压差和接地电流值主要由线性稳压器的旁路元件(pass element)确定,电压差和接地电流值定了后就可确定稳压器适用的设备类型。目前使用的五大主流线性稳压器每个都具有不同的旁路元件(pass element)和独特性能,分别适合不同的设备使用。标准NPN稳压器的优点是具有约等于PNP晶体管基极电流的稳定接地电流,即使没有输出电容也相当稳定。这种稳压器比较适合电压差较高的设备使用,但较高的压差使得这种稳压器不适合许多嵌入式设备使用。本文说明多种线性稳压器架构的基本运作原则,并摘要说明其中重要的参数,归结针对特定规格选用适当线性稳压器的要点。

基本线性稳压器运作

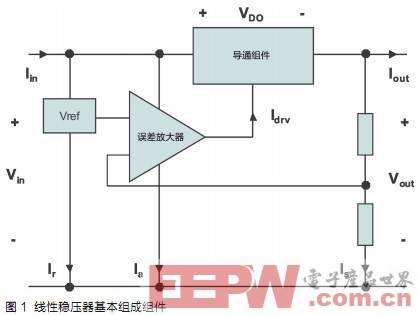

线性稳压器电路包含四个功能区块,分别是参考电压、导通组件(pass element)、取样电阻及误差放大器,如图 1 所示。

导通组件是由 芯片 的误差放大器所控制,误差放大器会监视反馈的状况,并且与内部固定的参考电压进行比较,然后会开启或限制导通组件,以便当输入电压产生变动时仍能维持恒定的输出电压,以及提供负载所需的输出电流。大多数的线性稳压器也具有用来保护稳压器的过电流及高温保护电路。

电压差及静态电流

电压差(Dropout Voltage)

稳压器若要正常的工作,输入端和输出端的电压差就必须超过某个值,这个值称为「电压差」。

电压差小于 1V 的线性稳压器通常被归类为低压降线性稳压器 (LDO),而电压差大于 1V 的线性稳压器则被归类为标准线性稳压器。如果输入电压接近输出电压,而且需将功耗降至,此时就需要使用 LDO.

静态电流

所谓静态电流就是在接上电源适配器在不上电池的情况下,主板所产生的电流。在维修的时候,我们用电源供应器来代替电源适配器,电源供应器有两个档位,一个是电压档另一个是电流档。静态电流就会在电流档上显示出来的。电压档显示的就是笔记本电脑的供电电压。静态电流包含偏移电流(例如带隙基准源、取样电阻及误差放大器电流)及串行导通组件的栅极/基极驱动电流,后者不会产生输出功率。静态电流值大部分是由串行导通组件和稳压器拓朴所决定。

线性电压稳压器的分类

更高的效率是设计工程师持续的要求。这个要求就转化为对Iq(静态工作电流) 和正向电压降的降低。随着制造商提高线性稳压器的标准性能,也为其它特性带来了负面影响。通用线性稳压器的设计可以提供的整体性能。彼此互相影响的性能指标会被折衷处理。封装选择则主要取决于成本和广泛的市场接受能力。

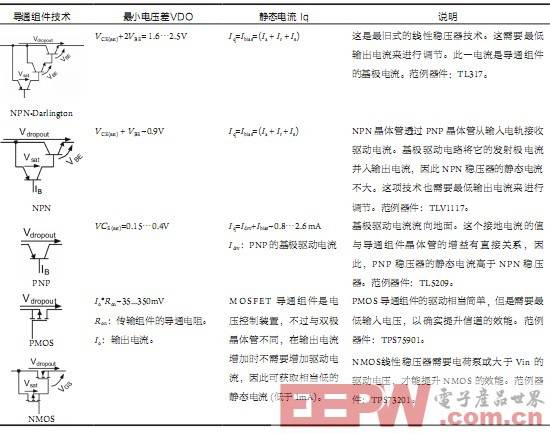

线性电压稳压器是按照导通组件技术进行分类,包括:NPN-Darlington、NPN、PNP、PMOS 及 NMOS 稳压器。表 1 显示不同的类型以及一般电压差与静态电流特性。

PNP双极体晶体管一般被运用于低压降的应用,主要是因为这类晶体管很容易就能够达到低压降,然而,它会产生高静态电流,而且效率不高,因此不适用于以发挥效率为首要考虑的应用。PMOS装置经过大力的开发,目前的效能已超越大多数的双极体装置。NMOS导通组件的优势是它的电阻不高,不过,栅极驱动的困难却使得这类导通组件在应用中显得并不理想。NMOS LDO(如TPS74901)能够在 3A 输出电流的情况下达到120mV电压差。

与PMOS拓朴装置不同的是,输出电容器对于回路稳定性的影响不大。不论是搭配多颗电容器或甚至不搭配电容器,德州仪器推出的多款NMOS LDO都能稳定的运作。NMOS的瞬时响应也优于PMOS拓朴,对于低输入电压的应用更是如此。

高效能线性电压稳压器的特殊功能

简易的电压稳压器只需要Vin、Vout及GND等三个终端,在线性稳压器的演进中,下一步则需要加入 ENABLE引脚,以便稳压器能够开关。

数字应用的稳定性需求使得稳压器必须整合电源电压监控(SVS) 的功能,这些功能能够将 RESET 或 POWER GOOD 输出提供给处理器。内部比较器会监视稳压器输出电压,并且使数字系统在出现欠压状况时启动复位。输出达到稳压状态时,会在经过一段时间后 (通常是 20 到 200ms) 停止复位。当输出电压低于要求输出电压的迟滞窗时,便会再度进行复位。

POWER GOOD指出 Vout的状态,而且通常用于启用其它电源以进行定序。当Vout超出POWER GOOD跳变阈值(通常是设定点电压的 97%) 时,POWER GOOD引脚会进入高阻抗状态,否则 POWER GOOD 会降低。

PLL 和 RF 电路的电源需要是低噪声的电源,才能发挥效能。过滤 LDO 的参考电压能够有效获得低噪声电源,支持此功能的 LDO 具有旁通引脚,能够在误差放大器的参考输出及输入之间连接一个滤波电容器。TPS79101 是这类 LDO 中很好的例子,它在 100Hz 至 100kHz 频率范围内只会产生 15mVRMS 的噪声。

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利 用锁相环路就可以实现这个目的。

FPGA 及处理器这类复杂的数字器件有时会在启动时出现高起动电流,当供电电压以缓慢上升的方式启动时,起动电流会降低。要做到这点,TPS74401这类的 LDO 必须具有整合的软启动功能,才能让使用者设定启动时电压上升的速度。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

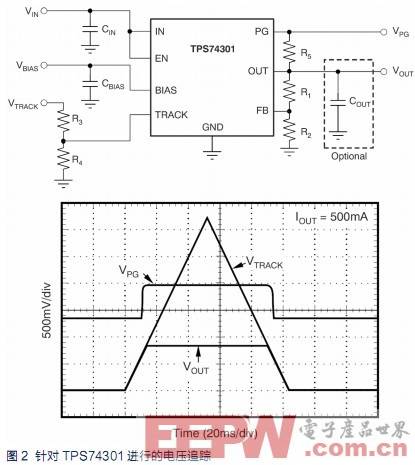

复杂数字系统需要的另一项功能是电压追踪,许多处理器在CORE和I/O电源引脚之间的静电放电架构往往有很大的压力,这项功能有助于降低这个压力。追踪功能使 LDO 输出电压能够追踪外部的电源(见图2)。

选用正确的线性稳压器

选用线性稳压器时,必须先考虑需要的输入电压范围、输出电压及电流。如果允许输入电压接近输出电压,务必确定的电压差不会限制需要的输入电压范围。另外,输出电压的准确性与应用所需的准确性相符也是很重要的。然后确认是否需要低噪声或特殊输出电容器 (若有必要) 等特定特性,,考虑 ENABLE、POWER GOOD 或定序等其它功能。考虑以上各点可将适用的线性稳压器范围缩小于特定的需求。

此外,选用线性稳压器时,也必须考虑通常会忽略的特定应用散热问题。大多数LDO稳压器都会指定给温度上限,以确保运作正常。此一上限限制了稳压器能够在任何特定应用中处理的功耗。首先计算实际功耗PD,用下式表示(不考虑静态电流):

PD = (Vin – Vout) ×Iout

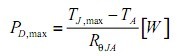

其次计算允许功耗上限PD(max),此上限是由下式决定:

其中TJ,max是允许温度上限 [℃],TA 是环境温度 [℃],RqJA 是封装的给处热阻抗 [℃/W]。

为确保给温度上限不超过可接受的限制范围,PD必须小于或等于 PD(max)。

功耗产生的热量是由线性稳压器的封装及外部散热器散出。影响散热能力的因素包括 PCB 设计、放置组件的位置、与电路板其它组件的互动情况、空气流通状况及海拔高度。如需线性稳压器设计的散热考虑详细信息,请参阅德州仪器应用说明事项 SLVA118《数字设计人员的线性电压稳压器及散热管理指南》。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。