测定水平角或竖直角的工作。水平角是一点到两个目标的方向线垂直投影在水平面上所成的夹角。竖直角是一点到目标的方向线和一特定方向之间在同一竖直面内的夹角。通常以水平方向或天顶方向作为特定方向。水平方向和目标间的夹角称为高度角。天顶方向和目标方向间的夹角称为天顶距 .角度的度量常用60分制和弧度制 .60分制即一周为360°、1°为60′、1′为60″。弧度制采用圆周角的2π分之一为1弧度。1弧度约等于57°17′45″。此外,军事上常用密位作量角的单位。为使1密位所对的弧长约略等于半径的1/1000,取圆周角的1/6000为1密位。角度测量主要使用经纬仪。测角时安置经纬仪,使仪器中心与测站标志中心在同一铅垂线上,利用照准部上的水准器整平仪器后,进行水平角或竖直角观测。本文提出的脉冲细分技术可以对测角脉冲进行细分,以获得更高的测角分辨率。

1 脉冲细分技术

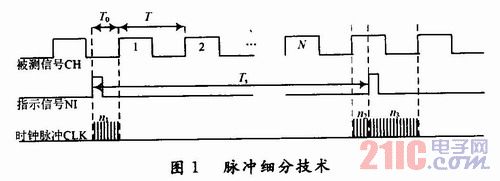

传统的对角度传感器数字脉冲的测量方法是在确定的采样时间内对脉冲数进行计数。如图1是在2个指示脉冲时间间隔Ts内对脉冲计数,计数值为N+1.

在时间间隔Ts内存在为±1个脉冲的计数误差,误差δN在区间[-1,1]上的概率密度分布为均匀分布,根据计算为δN=0.82.某型激光陀螺的标度因数约为1.8"/脉冲,则整脉冲计数方法的角度测量误差为0.82×1.8"=1.48",这并不能满足高测角的要求。

脉冲细分技术是根据转台伺服控制系统中数字化速度测量方法中的高速、高、连续测速方案来实现的。利用脉冲细分技术对测角脉冲进行细分,将脉冲数的小数部分测量出来,这样可以大大提高测角的分辨率。

如图1,假设在指示脉冲时间间隔Ts内,对测角脉冲上升沿进行计数,计得N+1个,认为这段时间内的整数脉冲数为N,将前一个指示脉冲上升沿与计得的个测角脉冲上升沿之间的头小数脉冲数n1加上第N+1个测角脉冲上升沿与后一个指示脉冲上升沿之间的尾小数脉冲数n2相加即为这段时间内的小数脉冲数。而下一段指示脉冲时间间隔的头小数脉冲n3加上这段的尾小数脉冲n2为1.因此只需测量每的头小数脉冲或尾小数脉冲即可。

假设测角脉冲周期为T,时间细分高频计数时钟脉冲周期为Tc,头小数脉冲时间为To,利用高频计数时钟可以地将T与To测量出。测角脉冲数可表示为:

式中:f为测角脉冲信号频率,fc为高频计数时钟频率。假设测角脉冲信号频率为1 MHz,高频计数时钟频率为50 MHz,代入式(2)得δNp =0.033脉冲。假设某型陀螺的标度因数为1.8"/脉冲,则角度测量误差为0.033×1.8"=0.059".可以看到误差很小。脉冲细分技术的运用对提高测角起到了关键作用。

2 基于FPGA的脉冲细分电路的设计

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA.因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(复杂可编程逻辑器件备)。

2.1 总体设计

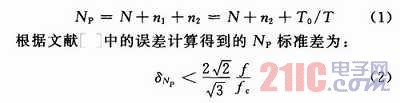

大部分的角度传感器输出信号都是由两路相位差90°的脉冲信号组成,设计电路时首先可以对两路信号进行鉴相解调与倍频,一方面完成转向的判断,另一方面将两路信号四倍频;接着设计整数脉冲计数器、小数脉冲计数器,对相应脉冲数进行计数;将计数值通过串口通信单元顺序发送至计算机,方便后期的数据处理。这里为关键的问题是利用脉冲细分技术计出被测脉冲的小数部分,另外指示脉冲对计数器的控制关系到计数值的准确与否,因此要利用性能良好的硬件并巧妙地设计程序。这里硬件选择了FPGA,程序则是利用HDL语言进行编写,脉冲细分电路总体设计如图2所示。

2.2 整数脉冲计数器

为了更准确地对倍频后的脉冲进行计数,在设计时,电路采用了2个计数器轮流计数,指示脉冲控制2个计数器交替工作。具体方法是将两个计数器的使能信号分别设置为1和0,由指示脉冲控制使能信号,在每一个指示脉冲到来时使能信号取反。另外,由于计数值很大,为了保证数值不会溢出,使用32位计数器。

2.3 小数脉冲计数单元

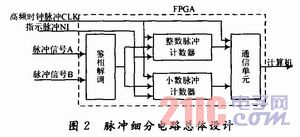

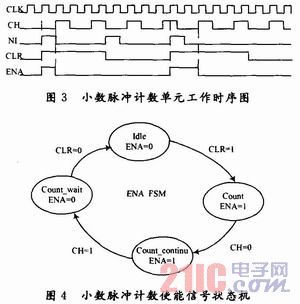

由脉冲细分技术可知,小数脉冲计数单元是要对指示脉冲上升沿与在其之后的个测角脉冲上升沿之间的高频计数时钟脉冲计数。测角脉冲信号是周期性的,而设计时要用到的只是指示脉冲之后的个陀螺信号的上升沿,这给小数脉冲计数的设计带来了困难,在设计时使用了有限状态机。这里主要利用整数脉冲计数单元中设计的整数计数器使能信号CLR与测角脉冲信号CH的状态组合来设计状态机,利用状态机输出小数脉冲计数器的工作使能信号ENA,这里状态都是在时钟CLK上升沿转换。图3与图4分别为小数计数器工作时序图与使能信号状态机。

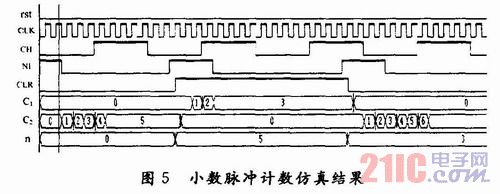

整数计数器是利用2个使能相反的计数器来设计实现的,为了同步地对每两个指示脉冲时间段内的整数与头小数脉冲进行计数,小数脉冲计数的设计也将采用两种对应于整数脉冲计数使能信号的计数方式。利用QuartusⅡ对小数脉冲计数单元进行仿真得到图5.

图中C1、C2分别是2个小数脉冲计数器计数值,轮流进行计数,并将计数值保持到下一个指示脉冲到来,将2个计数值或运算后输入寄存器,这样与上面的整数脉冲计数值同步保存,并方便了串口的读取。仿真结果表明,计数器工作正常,寄存器n记录数据正确。

2.4 通信单元

通信单元主要功能是倍频后测角脉冲的整数脉冲计数值,小数脉冲计数值顺序发送至计算机。这里使用UART串口方式将数值进行输出,UART对上述各个计数值的顺序读取则通过状态机来完成。编写程序将高频时钟信号进行分频得到UART传输时钟信号。

3 实验结果

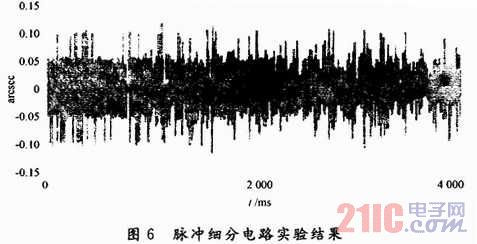

在转速较高的情况下,对上文提到的某型激光陀螺输出信号进行1毫秒的周期采样,实验结果如图6.结果表明,使用脉冲细分电路后陀螺输出角度标准差为0.079",有效提高了测量。与理论值0.059"有所偏差,这主要是由电路的计数误差与陀螺本身存在的随机游走等误差因素造成。

4 结语

对传统的基于脉冲计数的角度测量方法进行了误差分析,提出了一种脉冲细分技术并结合某型激光陀螺进行误差分析,并利用FPGA对该技术完成硬件实现,进行了实验验证。无论是理论分析还是实验结果都表明,该技术能够有效提高测角和角度分辨率,为满足高测量的需求打下基础。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。