波形发生器是一种数据信号发生器,在调试硬件时,常常需要加入一些信号,以观察电路工作是否正常。用一般的信号发生器,不但笨重,而且只发一些简单的波形,不能满足需要。例如用户要调试串口通信程序时,就要在计算机上写好一段程序,再用线连接计算机和用户实验板,如果不正常,不知道是通讯线有问题还是程序有问题。用E2000/L的波形发生器功能,就可以定义串口数据。通过逻辑探勾输出,调试起来简单快捷。将逻辑探勾接在J3插槽上,波形发生器通过J3可以输出8路自定义数字波形,每路可以单独加在用户板的任何输入端。波形发生器可以选择不同的时间基数,做为定义波形的短间。E2000/L可产生短时基为50ns.可自定义波形长度为 时基x 32767.波形发生器可自动返回, 循环产生波形。

DDS同 DSP(数字信号处理)一样,是一项关键的数字化技术。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。

1 DDS模块的设计

1.1 DDS在FPGA中的实现

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA.

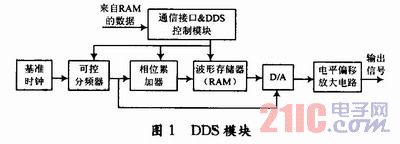

DDS由相位累加器,波形存储器,D/A转换器,低通滤波器等部分组成。该系统的DDS模块根据需要做了适当的修改。其结构框图如图1所示。

(1)增加了通信接口电路和DD8控制模块用于接收用户数据和控制DDS的运行状态。

(2)基准时钟采用5 MHz,经过可控分频器分频后作为DDS的时钟信号,周期分辨率可达200 ns(即分频为1)。

(3)相位累加器的频率控制字固定为1,相位控制字固定为0.

(4)波形存储器采用RAM,可以写入用户自定义的波形数据以产生任意波形,其地址宽度设置为11 b,这样存储深度可达2K点。

(5)电平偏移电路用于消除D/A输出信号中叠加的无效直流分量,对于有效的直流分量会保留。

1.2 通信接口及控制寄存器的设计

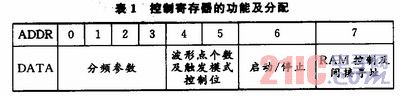

DDS控制寄存器控制整个DDS模块的运行参数和状态,并通过通信接口接收来自ARM的数据。根据需要共设置了8个寄存器,地址从O~7.其功能和分配如表1所示。

表1其中:

(1)0~3 B存储分频参数,占用32位,因此分频范围为1~232.

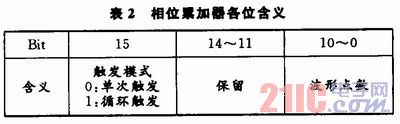

(2)4~5 B存储相位累加器的参数,用于控制波形点数和触发模式,其各位的含义如表2所示。

(3)6 B只使用了位,为1启动DDS,为0则停止DDS.

(4)地址7是一个虚地址,并不对应着实际的物理寄存器,而是与相位累加器组合指向RAM的某一个单元,通过对地址7的写操作就间接的实现了对整个RAM的操作,这样大大简化了对DDS的控制操作。

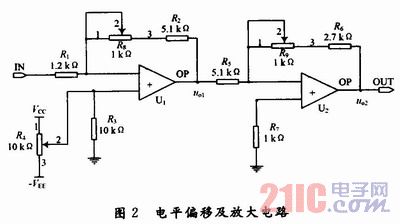

1.3 电平偏移及放大电路

电平偏移及放大电路用于消除输出信号中叠加的无效直流分量(允许有效直流量输出)和调整信号增益,其电路图如图2所示。

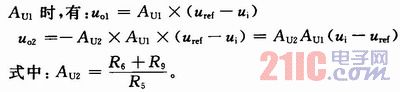

根据图2电路有:

![]()

式中:Rv是R4两部分的并联电阻,当

![]()

2 Qt程序设计

2.1 GUI设计

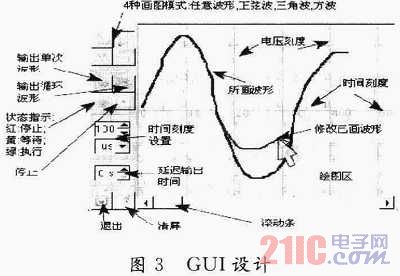

图形用户界面(Graphical User Interface,简称 GUI,又称图形用户接口)是指采用图形方式显示的计算机操作用户界面。与早期计算机使用的命令行界面相比,图形界面对于用户来说在视觉上更易于接受。GUI 是 Graphical User Interface 的简称,即图形用户界面,通常人机交互图形化用户界面设计经常读做"goo-ee",准确来说 GUI 就是屏幕产品的视觉体验和互动操作部分。GUI 是一种结合计算机科学、美学、心理学、行为学,及各商业领域需求分析的人机系统工程,强调人-机-环境三者作为一个系统进行总体设计。该系统的GUI设计见图3.

左侧为工具栏,右侧黄色区域为绘图区。绘图区提供了滚动条,用于绘制超出屏幕范围的波形。可以绘制较长的序列信号。工具栏从上到下分为绘图模式选择区,波形输出设定区,时间设定区及清屏和退出按钮。波形的绘制只允许从左向右进行,一个时刻只对应一个数据点;已绘制波形允许修改,修改过程中自动变成红色,修改完毕自动变成默认颜色。

2.2 Qt编程原理和方法

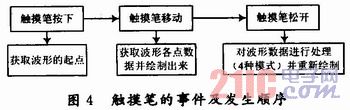

Qt程序设计采用面向对象和事件驱动的方法,整个GUI程序划分为两个类,其中主窗口为一个类,类名为MainWindow,继承自Qt的QMa-inWindow类,它提供了工具条(toolbar)和一个主窗口(mainwindow);另一个类是DrawWidget,提供了一个绘图区域,有4种事件,分别为触摸笔按下(mousePressEvent),移动(mouseMoveEvent),松开(mouseReleaseEvent)和绘图区重绘事件(paintEvent)。同时提供了处理波形的函数waveProcess和调用底层驱动的接口。滚动条是通过QScrollView类提供的视图功能来实现的。延迟输出功能通过Qtimer类来实现,延迟范围0~999 s.触摸笔的3个事件的发生顺序和处理过程见图4.

信号/槽机制是Qt的一个中心特征,用于对象间的通讯。绘图事件(paintEvent)采用双缓冲机制。双缓冲技术是一种GUI编程技术,它指的是在一个不在屏幕上的位图上渲染一个物件并把此位图拷贝到屏幕上,常用于消除闪烁和提供一个快速用户界面。该程序采用了Qpixmap类来实现双缓冲。

2.3 驱动程序设计

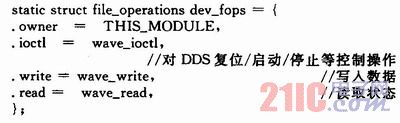

Linux设备驱动程序是系统内核的一部分,运行于内核态。其可以以两种方式被编译和加载:直接编译进Linux内核和编译成一个可加载和删除的模块,通过modprobe/insmod和rmmod来加载和卸载驱动模块。该系统即采用字符设备驱动。在系统内部,I/O设备的存/取通过一组固定的入口点来进行,具体到Linux系统,设备驱动程序所提供的这组入口点由一个文件操作结构file_operation来向系统进行说明。该系统的驱动函数需要提供3个函数调用,read函数用于读取DDS运行状态,write函数用于向DDS写入参数和波形数据,ioctl函数用于复位/启动/停止DDS.另外还需要打开(open)和关闭设备函数(close)。File_operatio的定义如下:

驱动程序在wave_ioctl,wave_wirte,wave-read等几个函数中具体实现。所需的波形参数和数据通过Qt程序打包,调用write函数(对应驱动程序中的wave_wrtie函数)性写入DDS模块。终将驱动程序编译为模块文件(*.ko),通过命令modprobe和rmmod来加载和卸载驱动模块。

3 系统操作及测试

(1)设置波形参数,包括绘图模式,时间轴刻度,输出延时等。

(2)绘制波形,并作相应的修改,终完成波形绘制。在松开触摸笔之后Qt程序根据所选择的波形绘制模式对波形进行处理和优化并重新显示出来。

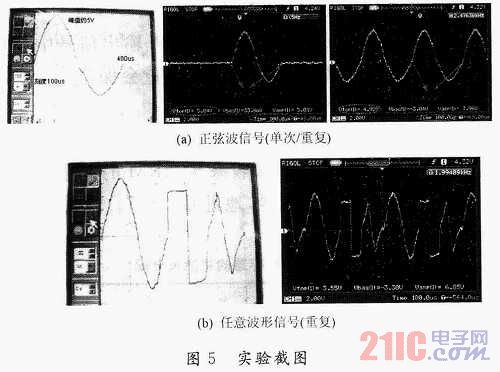

(3)点击单次触发模式或重复(循环)触发模式,此时Qt程序提取时间轴刻度参数,转换为DDS中可控分频器的分频参数,并将这些参数和处理后的波形数据打包传输给DDS模块,输出延时完毕则启动DDS,即产生与所绘波形相同的实际电信号,达到"所见即所得"的效果,如图5所示(时间刻度为100μs)。

4 结语

任意波形发生器是现代电子技术的一个新发展,本文给出了一种基于DDS和Qt的任意波形发生器的整体设计方案,分析了DDS在FPGA中的实现和Linux下Qt程序的设计。该设计的特点是"所见即所得",即绘制何种波形就可立即产生何种波形,非常直观,从而以满足各种电路测试,通信等领域快速产生任意波形信号的要求。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。