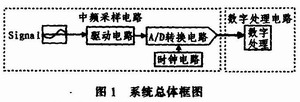

1 系统总体设计

图1为中频采样系统总体设计框图。由图1可知,该系统主要由驱动电路、A/D转换电路、时钟电路3部分组成。

1.1 驱动电路

信号A/D转换前往往需要进行以下处理:1)放大或衰减,使输入信号的电平与A/D转换器的所需电平相吻合;2)直流补偿或电平转换,通过补偿提高或降低直流电平使之符合A/D转换器的工作电平;3)滤波。

使用运算放大器作A/D转换器的接口还可作为缓存。这样可以解决以下问题:1)阻抗匹配,信号源往往并不是该系统设计所需的低阻抗,A/D转换器的输入将影响信号源。通常运算放大器缓存具有高输入阻抗,因此它不会对信号源产生影响。另外其低输出阻抗有益于A/D转换器的驱动;2)减小容性负载的影响。大多数的A/D转换器除在输入端具有电阻特性外,还具有电容效应;3)将单端信号转换为差分信号,许多A/D转换器使用差分输入,而大多数信号是单端的。

1.2 A/D转换电路

A/D转换器的性能指标主要分为静态参数和动态参数2种。静态参数是指A/D转换电路在低频或直流下的性能参数,而动态参数则是指中频或射频信号输入时的性能参数。重要的动态特性指标包括:信噪比RSN、无杂散动态范围SFDR、有效比特位ENOB、积分非线性INL、微分非线性DNL等。

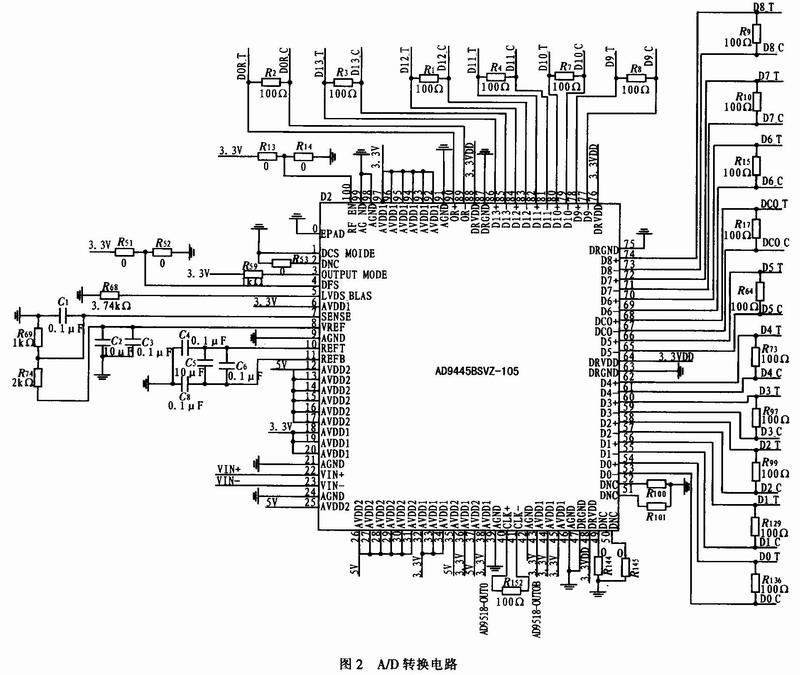

一个高性能的中频采样系统对噪声性能的要求很高,A/D转换器的噪声来源通常有:A/D转换器失真和量化噪声,A/D转换器等价输入噪声,内部抽样保持电路的孔径抖动,不良的接地和退耦设计,外部驱动放大器的噪声,不良的布局和信号走线设计,采样时钟噪声,外部电源噪声。针对以上噪声来源,该系统设计采用以下方法,力求减小噪声的引入:所有芯片的电源部分都采用钽电解电容与大面积,低阻抗的地层相退耦,用于去除低频噪声;使用铁氧体磁珠去除电源的高频噪声;模拟地与数字地分离。A/D转换电路如图2所示。

1.3 时钟电路

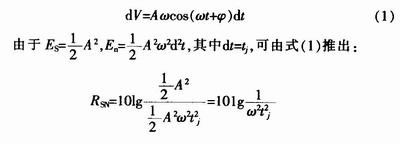

中频采样系统的时钟抖动会对系统性能产生很大影响,并且随着输入信号频率的增加,这种影响越来越明显。设输入信号V=Asin(ωt+ψ),采样时钟抖动为dt,信号能量为Es,噪声能量为En,则有:

式(2)是在假设信号为正弦信号输入的基础上推导出来的。而对于任意信号,都可以看成是单频(正弦)信号的组合,所以,式(2)具有通用性。

2 系统硬件设计

2.1 A/D转换电路设计

采用AD9445作为A/D转换电路的器件。该器件是一款适用于中频采样的14位,单片集成A/D转换器。它采用3.3 V和5.0 V双电源供电,支持差分信号的时钟输入,支持CMOS、LVDS 2种数据输出格式。其重要引脚功能如下:DCS MODE:时钟占空周期稳定器控制引脚,该引脚为低电平时可以起到稳定时钟周期占空比的作用。

OUTPUT MODE:将输出数据电平选择为CMOS电平,或者LVDS电平,为了获取更高的性能,采用LVDS电平。

DFS:数据格式选择。可以将输出数据格式设置为二进制补码或者偏置二级制格式。

VREF:配置该引脚可设置其内部参考电压。

SENCE:配合VREF引脚完成内部参考电压的设置。

REFT,REFB:差分参考输出引脚。

VIN+,VIN-:输入电压引脚。

CLK+,CLK-:采样时钟输入引脚。

D0~D13:输出引脚。

DC0:数据时钟输出引脚。

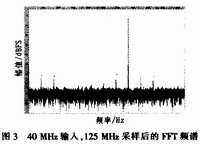

目前,主流中频采样A/D转换器都采用差分信号输入。本系统在输入中频单频信号频率为40 MHz的情况下。信噪比可达77.4 dB,,其频谱如图3所示。

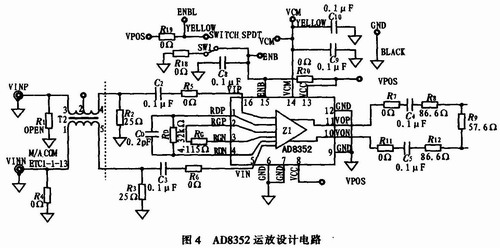

2.2 A/D转换器前端运放电路

该系统设计采用AD8352型超低失真差分中频放大器作为A/D转换器的驱动器件。其电路设计如图4所示。

通过设置电阻RG的大小,可调节AD8352的放大倍数,其范围为:3~25 dB。CD和RD用于消除失真。

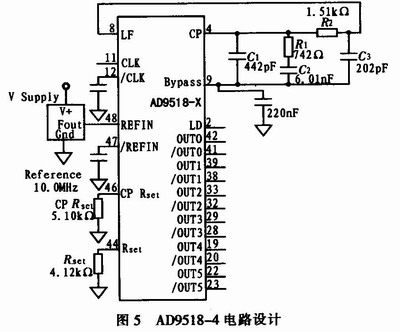

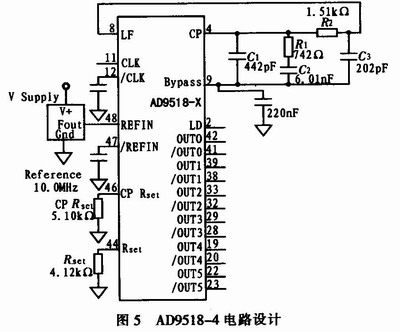

2.3 采样时钟电路

AD9445的采样时钟必须是一个高质量,超低相位噪声的时钟源。根据上述理论分析可知,时钟抖动会对A/D转换器的性能造成很大影响:

假设一个中频输入信号的频率为70 MHz。采样时钟的抖动为1 ps,则RSN=-201g(2πx70x106x10-12)=67.13 dB。结果说明,时钟的抖动已经将A/D转换器的信噪比限制在67.13 dB以下。这里采用高性能时钟分配芯片AD9518-4作为采样时钟,电路设计如图5所示。

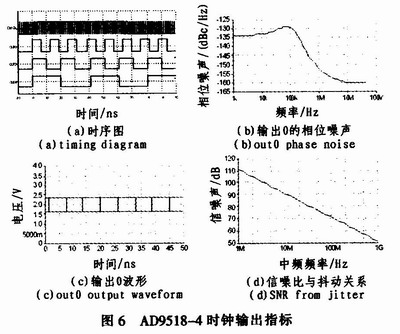

AD9518具有6路时钟输出,可分为3组,即同时可输出3种不同频率,并且每路的频率输出都可以通过软件进行配置调节。AD9518具有内部锁相环和压控振荡器电路,时钟输出范围宽,时钟抖动小,输出频率灵活。AD9518,我们可以获得高性能的采样时钟,同时,通过对AD9518内部寄存器的操作,改变采样时钟的频率,从而方便地进行中频欠采样或过采样等信号处理工作。图6显示了本设计中时钟采样电路的主要性能指标。

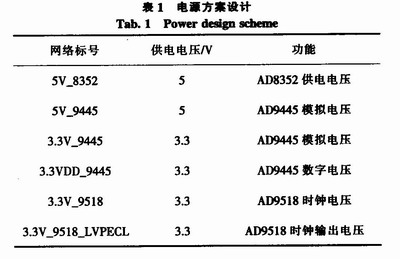

2.4 系统电源电路

电源噪声是板级设计中的主要噪声来源。为了尽量减小电源噪声,使用低压差线性稳压器LT1763作为电源器件。针对运放、A/D转换器以及时钟电路都要严格满足模拟与数字电源分离的要求。

3 系统软件设计

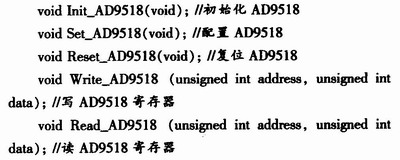

本系统软件设计是采样系统的时钟芯片AD9518的软件配置,AD9518是一款可调时钟输出频率的多路时钟输出芯片。配置软件中的主要功能函数包括:

4 结束语

中频采样系统应用广泛,但由于前端驱动设计问题或采样时钟抖动过大而限制采样系统的整体性能。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。