摘 要: 给出了基于Nios II的通用数字调制器的实现方法,具体说明了系统的基本原理、总体结构、硬件设计,以及软件流程等。该系统把可编程逻辑的固有优势集成到嵌入处理器的开发流程中,具有高度的灵活性、可重配置功能,便于升级和扩展,适于软件无线电的应用。

在软件无线电(SDR)的研究过程中,调制解调技术是无线通信系统空中接口的重要组成部分。目前常用的数字调制方式有多种,如果按照传统的硬件实现方法,要使一部通信机产生多种调制信号,其系统就会非常庞大复杂。

Altera公司的Nios II处理器是用于可编程逻辑器件的可配置的软核处理器。基于Nios II处理器系统的通用数字调制器是一种软件化硬件的解决方案,可以产生多种模式的数字调制信号,具有多功能性、通用性、集成度高、易于升级等优点,满足软件无线电系统的要求。

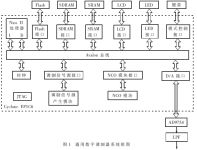

1 总体系统结构

本系统在一个调制器中灵活多变地实现了多种调制功能。Nios II处理器完成人机交互和控制工作,FPGA逻辑从Nios II处理器接收控制信号和数据后完成相应的硬件功能。数控振荡器(NCO)的各子模块必须在Nios II处理器的控制下,不断接收实时数据才能完成各种不同的数字信号调制。在某些情况下,这些数据传输是复杂的,好在Nios II处理系统有Avalon总线,它规定了控制器与从属组件间的端口连接以及组件间通信的时序。NCO通过Avalon总线与Nios II处理器连接,可以简单地看成外围设备,很方便完成控制和数据传输。

本系统采用Nios II和CycloneEP1C6嵌入式系统开发板,选用AD9754作为DAC芯片,并用LC电路搭建了9阶的椭圆低通滤波器,总体实现了一个可以产生多种调制信号的通用数字调制器。提供以下几种调制方式:移频键控调制(FSK)、二进制移相键控调制(BPSK)、四进制移频键控(QFSK)、四相相移键控调制(QPSK)、标准载波输出(Sin)。

调制方式和载波频率可以通过拨码开关和按键自由选择,LED和LCD的显示便于用户直观了解当前的状态信息。系统工作过程中,当再次按下"启动/停止"键时,可以对调制方式和频率重新进行设置。

2 Nios II嵌入式软核处理器简介

能够满足任何应用32位嵌入式微处理器的需要,客户可以将代Nios处理器设计移植到某种Nios II处理器上,Altera将长期支持现有FPGA系列上的代Nios处理器。另外,Altera提供了一键式移植选项,可以升级至Nios II系列。Nios II处理器也能够在HardCopy器件中实现,Altera还为基于Nios II处理器的系统提供ASIC的移植方式。

Nios II处理器具有完善的软件开发套件,包括编译器、集成开发环境(IDE)、JTAG调试器、实时操作系统(RTOS)和TCP/IP协议栈。设计者能够用Altera Quartus II开发软件中的SOPC Builder系统开发工具很容易地创建专用的处理器系统,并能够根据系统的需求添加Nios II处理器核的数量。

使用Nios II软件开发工具能够为Nios II系统构建软件,即一键式自动生成适用于系统硬件的专用C/C++运行环境。Nios II集成开发环境(IDE)提供了许多软件模板,简化了项目设置。此外,Nios II开发套件包括两个第三方实时操作系统(RTOS)--MicroC/OS-II(Micrium),Nucleus Plus(ATI/Mentor)以及供网络应用使用的TCP/IP协议栈。

长期以来,Altera一直推行嵌入式处理器战略的原因是,随着应用的ASIC开发日益受到成本的困扰,OEM日渐转向FPGA来构建自己的系统。这些系统中绝大多数需要一个处理器,而Altera正是为设计者提供了为FPGA优化的灵活的嵌入式处理器方案,可以满足16位和32位嵌入式处理器市场的需求。估计到2007年,该市场价值将到达110亿美元。

在FPGA中使用软核处理器比硬核的优势在于,硬核实现没有灵活性,通常无法使用的技术。随着系统日益先进,基于标准处理器的方案会被淘汰,而基于Nios II处理器的方案是基于HDL源码构建的,能够修改以满足新的系统需求,避免了被淘汰的命运。将处理器实现为HDL的IP核,开发者能够完全定制CPU和外设,获得恰好满足需求的处理器。

Nios II嵌入式处理器是Altera公司推出的第二代用于可编程逻辑器件的可配置软核处理器,性能超过200 DMIPS.Nios II是基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合,编程至Altera的FPGA中。处理器具有32位指令集、32位数据通道和可配置的指令以及数据缓冲。它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统(SOPC)设计了一套综合解决方案。Nios II处理器系列包括三种内核:高性能内核(Nios II/f)、低成本内核(Nios II/e)、性能/成本折中的标准内核(Nios II/s)。本系统采用标准内核。

Nios II 处理器支持256 个具有固定或可变时钟周期操作的定制指令;允许Nios II设计人员利用扩展CPU指令集,通过提升那些对时间敏感的应用软件的运行速度来提高系统性能。

3 系统硬件设计

3.1 调制信号源

调制信号源可以来自外部,通过串口、并口等送入,也可以由调制器内部产生。本系统由调制信号源产生模块产生了伪随机序列及其同步时钟信号。

3.2 数字调制的实现

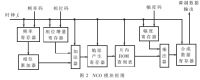

数字调制部分根据调制信号和来自CPU的控制信号产生可控模式、可控载频的已调信号。NCO模块包括频率控制字寄存器、32位的相位累加器、相位控制字寄存器、相位-幅度变换电路、控制逻辑电路,以及相位抖动补偿模块,如图2所示。NCO中各部件在参考频率源的作用下同步工作。相位累加器在每一个时钟上升沿与频率控制字K累加。当累加器计数大于232时,相位累加器相当于做模余运算。正弦查询表在每个时钟周期内,根据送给ROM的地址(相位累加器的12个MSB相位值)取出ROM中已存储的与该地址相对应的正弦幅值,将该值送给DAC和LPF实现量化幅值到一个纯净信号的转换。

由于资源和成本的原因,通常相位累加器输出的32位不会全部用来寻址ROM,本系统取其高12位寻址 ROM,其余LSB位被舍去,这样就不可避免地产生相位误差,该误差是NCO输出杂散的主要原因。用于相位-幅度转换的存储器用片内ROM来实现,主要完成信号的相位序列到幅度序列之间的转化。幅度量化误差与波形存储器数据总线位数相关,本系统中为14位。

为了减小相位截断误差,要求在NCO的波形查表过程中保留更多的相位有效位;为了减小幅度量化误差,要求波形存储器保留更多的输出数据位并选择位数高的DAC.由于波形存储器的容量受限,因此在低杂散设计中,可以通过改变传统结构中的相位到正弦波形的线性映射关系,采用新的结构体系来降低波形存储容量,以使在不增加波形存储器容量的情况下,保留更多的相位有效位和数据总线位数。单象限正弦波存储结构是一种有效的方法。在这种结构中,利用正弦波形的四分之一对称性,将ROM表减至初的1/4,波形存储器只存储一个象限[0,π/2]的波形。相位累加器用于波形寻址的有效位输出中,两位被用作映射四个象限,其余低位用来寻址波形存储器。这样,通过一个正/余弦表的前1/4周期就可以变换得到正/余弦的整个周期码表。这种实现方法对存储器的要求很小,节省了大量资源。

由相位截断的分析理论,相位舍位序列是具有周期性的,如果能破坏其周期性,就能将DDS输出频谱中有规律的杂散分量变成随机的相位噪声,从而抑制相位截断引起的杂散。因此本系统在ROM表之前加入了相位抖动注入模块,通过随机加扰的方法抑制DDS的相位截断杂散。

本系统NCO输出信号频率fout与参考时钟频率fclk为 及频率控制字K之间的关系为,在96MHz参考时钟的情况下,频率分辨率为0.022 35Hz.

及频率控制字K之间的关系为,在96MHz参考时钟的情况下,频率分辨率为0.022 35Hz.

3.3 D/A转换与低通滤波

FPGA输出的14位二进制数需要送到DAC进行D/A变换,得到量化的阶梯波形输出,经低通滤波器滤除高频分量,平滑后得到模拟的已调信号。DAC 非理想特性带来的转换误差是影响输出信号频谱的又一因素,主要取决于DAC器件的性能。本设计选用AD9754作为DAC芯片。

用LC电路搭建了9阶的椭圆低通滤波器,截止频率为25MHz.其频谱如图3所示。

4 系统软件设计

本系统的设计是根据调制信号的信息对载波频率、相位和振幅进行控制。通过Nios II处理器来改变上述三个参数中的一个或几个,以完成各种不同类型的调制。Nios II处理器的主要工作有:,针对不同的调制模式,输出对应的控制码;第二,对某一具体的控制码来说,要根据其控制信号的值、时钟速率、相位累加器、ROM以及DAC位数等计算出具体的码值。软件流程如图4所示。

通用数字调制器是实现软件无线电的关键技术之一,现有文献中的实现方法是通过"DSP+FPGA"来设计的,其外围电路和控制逻辑复杂,成本较高。本文提出了一种基于Nios II嵌入式处理器软核的通用数字调制器实现方法,使用Altera的低成本Cyclone FPGA,且具有开发周期短、成本低等特点。

本系统所实现的各种调制方式均已通过硬件测试,证明了方案的可行性和正确性。

此外,在设计过程中使用SignalTap II嵌入式逻辑分析仪可以方便调试,采用增量编译可以缩短漫长的编译等待时间。图5是用SignalTap II对FSK分析时的截屏图。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。