引言

目前国际上已有的中频解调器一般只能够处理某几种定制的数据率,并采用如下的电路结构:①采用模拟Costas环提取相干载波;②针对每一种遥感卫星的特征设计一个特定的比特同步器,包括特定的基带滤波、时钟提取、取样判决再生、差分译码和串并变换等功能单元,用开关选择所需的比特同步器的数据和时钟输出,多可容纳6个特定的比特同步器。

上述设备具有以下缺点:首先,高中频、宽频带下的模拟Costas解调处理环路对电路的功能和性能要求高,电路稳定性差,引进设备在运行过程中的多次故障记录已证实存在这一问题;其次,需要多个专门定制的比特同步器,系统可扩展性差,其应用范围受到限制;再次是重复设置的设备和元器件使用量大,使设备成本高,价格昂贵,特别是连接电缆的数量达到上百根,可靠性也受到影响。

针对上述存在的问题,本文介绍了一种新型的中频解调器。由于设计了一个通用的比特同步器,在100~340Mbit/s数据率范围内可任意选择工作速率,具有良好的可扩展性,同时采用了数字化的Costas载波恢复环路,提高了设备的可靠性。

1 多速率中频QPSK解调器的组成与工作原理

多速率中频解调器主要由以下几部分组成(如图1所示)。

1.1 中频滤波器单元

中频滤波器单元完成中频输入匹配、中频滤波成形功能,由8路中频切换开关和若干中频滤波器组成。中频滤波器采用高Q电容加载梳状滤波器,带外抑制大于35dB,过渡带近似满足奈奎斯特滚降。

1.2 AGC放大单元

AGC放大单元由压控增益放大器和AGC控制电路组成。为了保证输入信号有50dB以上的电平动态范围,需要由自动增益控制(AGC)电路,以保证输出到解调单元的信号电平稳定。

1.3 解调单元

解调单元组成框图如图2所示,由包含分路器、相乘器、移相器的中频正交解调电路、相干载波误差提取电路、环路滤波器以及压控振荡器等组成。中频正交解调电路将中频调制信号变换成两路正交的基带信号,基带放大滤波电路具有良好的阻抗匹配,压控振荡器(VCO)要有尽量低的相位噪声。为了保证中频正交解调电路具有优良的幅度不平衡度和相位不平衡的,需要设计性能优异的90°移相电路、模拟相乘器电路和分路电路,并且在电路结构上保证整个电路具有完美的对称性,另外还需要在相互连接的电路模块之间设计匹配电路,以保证正交支路和同相支路在很高的频率、很宽的频带内都具有优良的不平衡度指标。相干载波误差提取电路采用了数字处理Costas解调环路的逻辑,它由一系列判决器和模二和组件构成,电路简单,具有非常好的一致性。假设x、y分别表示解调得到的两路基带信号,对于QPSK调制方式,数字处理Costas解调环路的基带数字处理函数为:

1.4 比特同步单元

比特同步单元由可编程时钟恢复电路、差分译码电路等组成。可编程时钟恢复电路完成符号率范围50~170Mbps的基带信号的定时恢复和数据再生,可编程时钟恢复电路的基本组成框图见图3。该电路输入一个NRZ码,时钟的提取由一个数字锁相环和一个数字锁频环完成,一个定时抽样电路完成时钟和输出数据的同步。锁相环(PLL)由鉴相器、分频器和电流振荡器组成,电流振荡器的频率范围由参数L[0-3]进行控制,并完全覆盖50~170MHz。为了使频率同步快速收敛,设计了一个包括鉴频器、控制电路、频率寄存器和数模变换器的FLL环路。

2 误码率性能测试系统组成与测试结果

本设备在遥感卫星地面实际的接收信道上进行误码率性能测试,其测试系统框图见图4。图中虚线框内所示的是接收站的上行测试信道和实际使用的下行接收信道的示意图,中频频率为720MHz,LNA(低噪声放大器)可工作于X波段,本测试系统利用了LNA产生的热噪声作为系统的噪声来源。频综为误码仪提供外时钟,误码仪产生出两路不相关的223-1序列,这两路数据分别送到中频调制器的I和Q数据输入端,上变频器将中频调制器产生的中频调制信号通过两级上变频器变换到X波段,通过一个射频耦合器将信号注入到下行信道,两级下变频器将X波段的RF信号和接收信道本身的热噪声变换到中频,中频信号经过一个带匹配器的分路器,分成两路中频信号,一路送到滤波器、功率计支路,进行信号和噪声的功率计量,另一路送到中频解调器,中频解调器恢复出并行的数据和时钟,取出I和Q路中的一路送到误码仪,分别测试I路和Q路的误码率,求出平均误码率。

将中频调制器的输出功率调整至A1使误码仪指示约1×10-7,记录误码仪的指示B1,这时测试的是I路数据误码率,然后测试Q路的误码率B2,取出平均误码率Ba。同时将下变频器的输出通过带宽为BW1的带通滤波器连接到功率计,带通滤波器的带宽为334MHz,读出的数值为信号加噪声的功率值P1。然后A1依次减小1dB,直到误码率到1×10-3左右,将测试调制器的输出功率调整到-63dBm,此时只有噪声功率,记录此时的功率值P2。 根据图5及以上的步骤,可以求出实际信号的归一化信噪比:

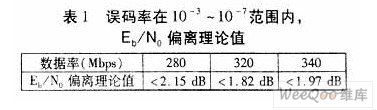

测试结果见图5,数据率为320Mbps时,系统误码率在10-3~10-7范围内,Eb/N0偏离理论值为1.82dB。同样的方法得到280Mbps和340 Mbps时的误码率指标,见表1。

3 结论

本文实现了一种新型的多速率中频解调器,可以完成100~340Mbps速率范围的解调和比特功能,并对该设备的误码率指标进行了测试,测试结果表明其误码率性能在10-3~10-7范围内均达到了较好的指标,该设备的部分功能和指标均超过了同期进口设备的水平。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。