摘 要:直接数字频率合成技术是一种新型的信号产生方法,是现代信号源的发展方向。该系统由FPGA 控制模块、键盘、LED 显示组成,结合DDS 的结构和原理,采用SOPC 和DDS 技术,设计出具有频率设置功能的多波形信号发生器。以Altera 公司的CycloneⅡ的器件EP2C35 为例,NIOS ⅡCPU 通过读取按键的值,实现任意步进、不同波形的输出显示功能。

0 引 言

直接数字频率合成( Dir ect Dig ital Frequency Synthesis,DDS) 是一种新型的频率合成技术,它把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。在现代通信领域中,DDS 的应用极其广泛。实现DDS 常用的方法是采用专用的DDS 芯片,控制部分采用独立的MCU ,这样设计出来的系统的集成度和扩展性不尽人意。随着大规模现场可编程门阵列的推出,SOPC 的不断发展,设计人员可以在FPGA 的嵌入式软核处理器上设计各种系统,满足用户需求。本文基于SOPC 技术设计直接数字频率合成器,选用A ltera公司的新一代FPGA( Cyclone Ⅱ) 为,利用FPGA的逻辑单元实现相位累加等数字逻辑功能,在ROM 中分别放入正弦表、方波表、三角波表、锯齿波表,用软核CPU 做控制,实现频率、相位、波形选择等。这样可以大大减小处理器外围扩展电路数目,还提高了系统的稳定性和抗干扰能力,节省了内部资源。

1 系统方案设计

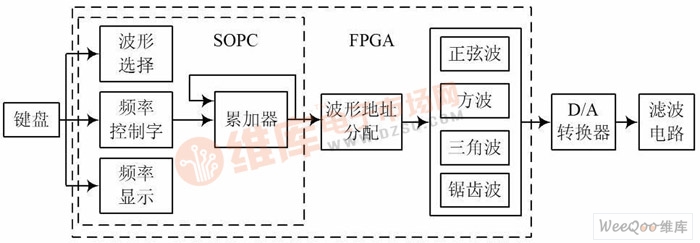

系统采用SOPC 设计方案。整体系统框图如图1所示,它由频率预置电路、波形选择、波形频率控制、累加器、存储波形数据的存储器和D/ A 转换电路、滤波电路组成。累加器模块由10 位加法器与10 位寄存器级联而成。波形存储器中放入正弦波、方波、三角波、锯齿波的数据。

图1 整体系统框图

1. 1 DDS 基本工作原理

DDS 的基本原理是利用采样定理,通过查表法产生波形。一个完整DDS 结构图如图2 所示。

图2 DDS 结构图

相位累加器在每一个时钟上升沿与频率控制字K累加,当累加器计数大于2N 时,相位累加器相当于进行取模运算。在每一个时钟周期内,根据送给ROM 的地址,取出ROM 中与该地址相对应的波形的数据,读取出ROM 中的数据后通过D/ A 转换器,将数字量转换成模拟量,通过低通滤波电路,可输出一个平滑的波形。

假设频率为f c 的载波,它的时域表达式为:

其相位表达式为:

输出频率f 0 与时钟频率f clk之间的关系满足:

当K = 1 时,DDS 有频率输出,因此DDS 的步长为f clk / 2N ,输出频率为f clk / 2。在本设计中,将N 设定为10 位,M 设定为12 位,相位累加器在时钟的控制下,以步长K 进行累加,输出N 位二进制码,并以其作为波形ROM 的地址,对波形存储器ROM 寻址,波形存储器ROM 输出的数据经过D/ A 转换成阶梯波后,经过低通滤波器平滑后,便得到合成后的波形了,合成后的波形形状取决于波形选取和ROM 中的数据。

1. 2 D/ A 转换器

从DDS 核输出的是一个数字信号,需要将数字信号转换成模拟信号,才能便于观察。DAC 有电压和电流输出两种,其输出的信号并不能真正连续可变,而是以其分辨率为单位,所以它的输出实际上是一个阶梯模拟信号,所以需要将D/ A 输出的信号通过低通滤波器平滑后得到纯净的模拟信号。在该设计中用到型号为AD9742 的D/ A 转换器,AD9742 是具有12 位、低功耗、转换速度可达到100 Mb/ s 的D/ A 转换器。

1. 3 基于SOPC 的硬件架构

系统开发包括硬件部分和软件部分,而硬件部分是由SOPC 开发工具搭建而成。SOPC Builder 生成NIOS 嵌入式处理器,NIOS 嵌入式处理器开发工具允许用户配置多个CPU ,在标准库中添加外围电路,也可以由用户自定义外设,综合处理自定义系统,这样使设计变得更加灵活。

打开SOPC Builder 后分别添加CPU,PIO 输入( 10 个按键用作频率字的输入、1 个按键用作确认、4 个按键用作波形的选择) ,存储器( FLASH,SRAM 和SDRAM) ,PIO 输出( 10 位作为ROM 的地址、2 位作为ROM 块的选择、7 位为LED 段码、1 位为LED 的选通端) 和定时器。所有组件添加完后的硬件架构图如图3 所示。

图3 SOPC 硬件架构图

SOPC Builder 生成之后,在Quartus 软件中可以添加生成之后的CPU 模块,而DDS 模块是用VHDL 语言编写而成,DDS 模块图如图4 所示。其中的ROM 大小为12 1 024,共设置4 块ROM 分别存储正弦波、方波、三角波、锯齿波。波形数据是由Mat lab软件计算出来的,并将数据以. mif 文件格式存储。累加器的输出为波形存储器的地址,进行波形的相位 幅值转换后,作为输出的波形的幅值。10 位的寻址ROM 相当于将一个周期的信号进行离散化,形成具有1 024 个样值的序列。累加器产生的地址通过波形的地址分配读取不同存储器中的数据,然后将读出来的数据经过D/ A 转换器,转换成模拟信号输出。

图4 DDS 模块图

2 软件设计

NIOS 完整的开发环境是NIOS 处理器与用户的接口界面。使用NIOS IDE 可以完成所有的软件开发任务,包括程序的编辑,编译和调试。硬件提取层( HAL) 支持通用I/ O 器件,可以通过编写标准C 程序访问硬件,HA L 减少了对硬件寄存器的访问,直接与外围器件进行通信或控制。不同的外围硬件需要不同程度的HAL 的支持,需要运行HAL 的软件驱动器。DDS 系统控制在NIOS IDE 环境下用标准C 语言实现,通过编写代码、编译、链接、调试、几个步骤完成整个设计。

打开IDE 开发环境后,步需要做的就是新建一个工程,将SOPC Builder 生成的. ptf 添加之后,系统根据该硬件的地址分配情况自动生成相应的头文件,该头文件定义了各个组件的基地址。当SOPC 系统发生变化,IDE 将在用户编译和运行应用程序时重新对HAL 进行编译。整个软件编写的流程图如图5 所示。

图5 软件流程图

3 系统调试过程与结果

系统时钟为50 MHz,当波形选择键选为正弦波,频率字设置为5 时,数码管上显示5,按下确认键后,数码管显示”-“,通过示波器,可以观察到输出波形如图6所示,横轴为时间档,纵轴为幅值。当波形选择键选为方波,频率字设置为10 时,数码管上先显示1,后显示0,按下确认键之后,数码管显示“-”,这样在示波器上观察到的波形如图7 所示。按照上面的操作过程,三角波和锯齿波的波形分别如图8,图9 所示。

图6 正弦波波形

图7 方波波形

图8 三角波波形

图9 锯齿波波形

4 结 论

本文所设计的是频率字的预置与波形的选择,是通过键盘输入的,因此能够得到规定范围内的任意频率的波形,这样可以很好地满足变频信号的情况,实用性较强。实验所调试出的波形清晰,干扰小。采用SOPC 方法实现,使设计变得非常灵活。该设计只实现了任意频率的波形输入,还需要实现相位累加,设计才会变得更加完美。

[1]. EP2C35 datasheet https://www.dzsc.com/datasheet/EP2C35+_1438348.html.

[2]. ROM datasheet https://www.dzsc.com/datasheet/ROM+_1188413.html.

[3]. AD9742 datasheet https://www.dzsc.com/datasheet/AD9742+_251589.html.

[4]. mif datasheet https://www.dzsc.com/datasheet/mif+_2043409.html.

[5]. ptf datasheet https://www.dzsc.com/datasheet/ptf+_2043378.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。