随着各种便携式电子设备的快速发展, 对单片开关电源控制芯片的需求越来越大, 相应地, 对于芯片的性能要求也越来越高, 为了避免在芯片正常工作时电源电压的波动对芯片内部电路产生不利的影响, 通常需要欠压锁存电路对电源电压进行监控, 一旦检测到低于所设置的欠压阈值, 芯片停止工作。

传统的欠压锁存电路要求简单实用, 但忽略了功耗的问题, 当芯片在正常工作时, 欠压锁存电路仍然具有一定的功耗, 这样就降低整个芯片的转换效率, 基于这样的考量, 本文设计了一种低功耗的欠压锁存电路, 并在CSMC 0. 5 m CMOS工艺库下使用Cadence Spectre进行了仿真验证, 结果表明基本满足设计要求。

1 电路设计

1. 1 传统的欠压锁存电路及原理

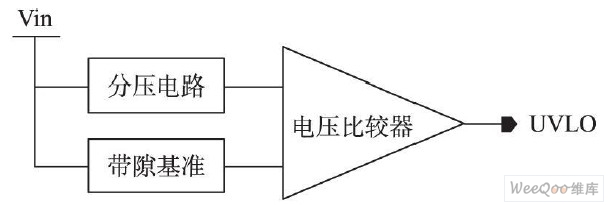

传统的欠压锁存电路如图1所示, 供电电源Vin提供偏置使带隙基准电压源工作, 分压电路采样Vin的变化, 通过电压比较器与基准电压进行比较, 产生一个UVLO信号。当采样值高于基准值时, 输出一个高电平, 启动芯片工作; 当供电电源Vin发生波动, 致使采样值低于基准值时, 输出低电平信号, 禁止芯片其他部分电路工作, 直到解除欠压状况。这种电路需要带隙基准源和比较器, 电路结构比较复杂, 而且电路的功耗比较大, 响应速度较慢。基于这种情况, 本文设计了一种新型欠压锁存电路, 以降低欠压锁存电路自身功耗, 提高响应速度。

图1 传统的欠压锁存电路示意图

1. 2 新型欠压锁存电路

新型欠压锁存电路由采样模块、先导控制模块、加速响应电路、迟滞反馈电路、缓冲电路等组成, 如图2所示。R 1, R 2, R3, R 4 电阻分压网络实现对Vdd电压的采样,M 1, R5 与Inv1(M12, M13组成)构成先导控制电路, 控制比较器的灌电流; M2, M3, R6 构成比较器, 实现采样电压与Vth的比较; M 5, R8, 与门AND1构成另外一路充电回路, 只在Vdd电压下降过程中有效; M0 实现迟滞反馈的功能; C0 为储能电容, 实现充放电的功能; M6, M7, M8, M9, M10, M11构成施密特触发器, 与Inv3 (M14, M15组成)一起实现整形滤波的功能。本电路通过先导控制电路控制电流较大的比较器的灌电流, 使比较器只有在状态发生翻转时有微弱的电流流过M3, 在其余时间内, 无论比较器输出高电平还是低电平, 都没有电流流过M3, 也就是说电路无论是处在正常工作状态还是欠压状态, 比较器总是关断, 这样就可以把电路的功耗降到, 满足了低功耗设计的要求。

图2 一种新型欠压锁存电路

具体的工作过程叙述如下:

在Vdd电压上升的过程中, 当电压较低时, 由于M1 截止, C 点处于高电位, 可以通过先导控制电路使M2 导通, 同时M4 也导通, 给电容C0 充电, 使E点充电至Vdd, 输出端为高电平, 电路处于欠压锁存状态; 随着Vdd电压升高, 由于A 点电压高于B 点电压, 使得M1 比M3 先行导通, 先导控制电路使M2 截止, 此时比较器的灌电流消失, 由于电容C0 还没有放电回路, E 点仍然保持高电位, 电路还是处于欠压锁存状态; 当Vdd进一步上升使得B 点的电压高于阈值Vth时, M3 导通, C0 通过该支路迅速放电, E 点电压降至0, 电路解除欠压状态, 进入正常工作状态, 并且使得M0 导通, R1 被短路。整个过程如图3所示。

图3 工作原理示意图

因此在Vdd上升过程中, 其阈值为:

随着Vdd电压下降, 电路从正常工作状态转为欠压状态的过程中, M3 先截止, 此时B, E 点都为低电平, 导致F 点为低电平, M6 导通, 给C0 充电, 但不会充到Vdd电压, 随着Vdd的持续下降, M1 截止, 使得M2 导通, 继而通过M4, R7 给C0 继续充电, 此时会充至Vdd电压, 输出高电平, 即电路处于欠压锁存状态,由于M3 一直处于截止状态, 没有灌电流流过, 所以基本上没有功耗。

因此在Vdd下降过程中, 其阈值为:

由上述两式可得出Vdd的迟滞量为:

另外, 为了实现先导控制电路的低功耗, R5 和M1 需要仔细设计, R5 不宜太小, M1 尺寸适当减小,使流过M1 的电流变小。

2 电路仿真与分析

在CSMC 0. 5 m CMOS 工艺模型下, 利用C adence Spectre仿真工具对欠压锁存电路进行仿真。

由于开关电源启动时为控制芯片提供的电源电压是逐渐上升的, 并且为了观察电路是否实现滞回功能,所以将Vdd电压设置成随时间变化的三角波形, 进行瞬态仿真, 仿真波形如图4所示。

仿真结果表明, 在Vdd上升的过程中, 当Vdd电压超过5. 29 V时, 电路退出欠压状态; 随着Vdd从7 V开始减小, 并低于4. 47 V (欠压阈值典型值), 电路又重新进入欠压状态, 输出高电平禁止芯片其他部分电路工作; 欠压阈值的滞回电压范围为0. 80 V,滞回特性使得电路避免干扰信号的影响, 提高抗干扰能力。此外, 比较器的翻转速度很快, 满足了对电路的响应速度的要求。

图4 输出信号波形

同时, 对流过比较器的电流进行瞬态仿真, 仿真波形如图5所示。由图5可知, 只有在比较器状态发生翻转的瞬间才有微弱的电流流过M3, 在其余时间内, 无论比较器输出高电平还是低电平, 都没有电流流过M3, 也就是说电路无论是处在正常工作状态还是欠压状态, 比较器都不消耗功率, 这样就可以把电路的功耗降到, 实现了低功耗的设计。

图5 流过比较器的电流波形

, 对整个电路的工作电流进行瞬态仿真, 仿真波形如图6所示。仿真结果表明, 芯片正常工作时, 即从芯片退出欠压到Vdd下降后重新进入欠压状态, 欠压锁存电路的平均功耗为7. 6 mW, 低于10mW, 实现了低功耗设计的要求。

图6 整个电路的工作电流波形

3 结论

随着各种便携式电子设备的快速发展, 对单片开关电源控制芯片的需求越来越大, 相应地, 对于芯片的性能要求也越来越高, 所以欠压锁存电路就成了开关电源控制芯片的基本需要, 它可以保证芯片在电源电压波动的情况下工作的稳定性。本文基于CMOS工艺设计了一种新型欠压锁存电路, 仿真结果表明, 该电路具有功耗低, 响应速度快等优点, 并且电路结构简单, 可以做成IP核, 易于移植到其他的开关电源控制芯片中去。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。