简介

ADI公司拥有种类齐全的高性能差分放大器产品(包括ADL5561、ADL5562、AD8375、AD8376和AD8352等),是以低失真、低噪声和低功耗为的通用IF和宽带应用的放大器。除了宽带宽、低失真外,这些放大器还具有增益调整能力,非常适合驱动模数转换器(ADC)。

通过在驱动放大器与目标ADC之间设计一个窄带通抗混叠滤波器,目标奈奎斯特频率区域外的放大器输出噪声得以衰减,有助于保持ADC的可用SNR性能。一般而言,若用一个恰当阶数的抗混叠滤波器时,SNR性能会提高数个dB.

此应用笔记介绍了一种接口设计方法,利用它可以实现高性能驱动放大器与ADC(包括采用开关电容输入的ADC)之间的更有效接口。本应用笔记所述的窄带接口方法针对驱动一些颇受欢迎的无缓冲输入ADC进行了优化,如AD9246、AD9640和AD6655等。

接口元件简介

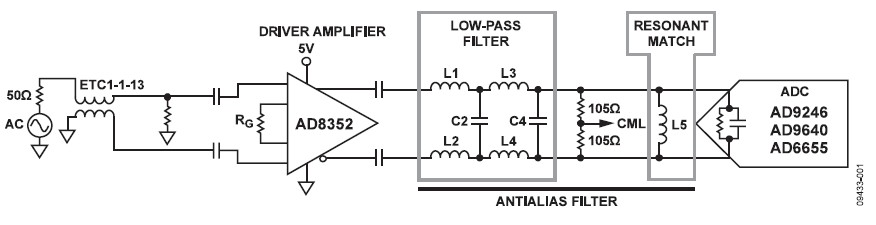

窄带接口用来提供带通滤波,同时提供足够的阻抗变换。图1、2和3所示为不同放大器ADC接口窄带方案的功能框图。这四种主要元件模块,即驱动放大器、低通滤波器、共振匹配和ADC,在接口定义中起到了关键作用,每一种都需要审慎对待。下列章节介绍每一种元件的具体要求。

图1. AD8352的ADC接口窄带解决方案

图2. ADL8375和ADL8376的ADC接口窄带解决方案

图3. ADL5561和ADL5562的ADC接口窄带解决方案

表1. 差分放大器和阻抗概述

差分驱动放大器

ADI公司差分放大器产品齐全,其中包括AD8352、AD8375、AD8376、ADL5561和ADL5562,提供三种基本的增益控制类型:电阻设定增益、并联数字控制和引脚绑定增益。为优化性能,这些增益控制类型各具有自己的输出阻抗集和所需阻抗负载,具体如表1所概述。

AD8352

AD8352使用增益设置电阻RG来设置增益,该电阻具有将器件与信号输入隔离的缓冲器。因此,对于3 dB至25 dB的增益,AD8352可保持恒定的3 kΩ输入电阻,从而降低了匹配和输入驱动要求。有关增益调节的详情,请参见AD8352的数据手册。

建议在输入和输出上连接交流耦合电容以隔离VCC/2偏压与源和平衡负载。

AD8352具有100 Ω的标称差分输出电阻,在负载阻抗等于200 Ω时可实现交流性能。这需要2:1的RL/RS滤波器比,其中RS为滤波器源阻抗,RL为负载阻抗。

AD8375和AD8376

AD8375是一款单通道、数字控制、可变增益放大器,而AD8376是其双通道版本。各通道通过独立的5位二进制代码来编程,以1 dB步进改变各衰减器的设置,使得各放大器通道的增益设置范围为+20 dB(代码0)至?4 dB(代码24及更高)。

AD8375和AD8376提供150Ω输入阻抗,经调谐驱动150 Ω负载阻抗,以获得性能。开集输出结构要求通过外部偏置网络实现直流偏置。每个通道输出端均采用一组1 μH扼流圈电感,用来向开集输出引脚提供偏置,这些引脚具有16 kΩ的差分输出阻抗。由于差分输出偏置为正电源,需要连接交流耦合电容,是0.1 μF.同样,输入引脚处于高于地约2 V的偏置电压下,也应进行交流耦合。

在没有任何输出匹配的情况下,如果RL/RS滤波器比很小,构成滤波器可能需要不切实际的大电感值和极小的电容值。阻抗比越大,对元件Q值和布局寄生就越要谨慎。建议采用大约300 Ω的分流输入和输出电阻来端接抗混叠滤波器。在图2示例中,滤波器两端的分流电阻在输入端为301 Ω,在输出端为330 Ω(通过两个165 Ω偏置设置电阻),两者一起为AD8375或AD8376提供形成标称150 Ω负载阻抗,并产生更有利的RL/RS滤波器比1:1.

ADL5561和ADL5562

ADL5561和ADL5562通过引脚绑定输入配置来设置增益。对VIP1施加输入A、对VIN1施加输入B时,增益为6 dB(增益)。对VIP2施加输入A、对VIN2施加输入B时,增益为12 dB(增益)。对VIP1和VIP2施加输入A、对VIN1和VIN2施加输入B时,增益为15.5 dB(增益)。注意,差分输入阻抗随增益绑定选择而变化:、中等和增益设置分别对应400 Ω、200 Ω和133 Ω。有关输入匹配的详情,请参见ADL5561或ADL5562数据手册。

建议在输入和输出上连接交流耦合电容以隔离VCC/2偏压与源和平衡负载。

该负载应等于200 Ω以提供交流性能。ADL5561和ADL5562的差分输入阻抗为12 Ω。阻抗比越大,对元件Q值和布局寄生就越要谨慎。为了简化滤波器设计,可在每个差分输出端增加约15 Ω的额外串联填充,以采用更有利的RL/RS滤波器比4:1.注意,添加的串联元件将衰减驱动器放大器输出。

ADC特性

在现代无线接收器设计中,高采样率的模数转换器(ADC)通常被用作中频复合调制信号的采样。基于CMOS开关电容的ADC因其低成本和低功耗而成为这类设计的。这类ADC的前端为非缓冲型,直接耦合至采样网络,所以ADC的输入阻抗会随时间(跟踪和保持模式切换时)变化,这就对驱动ADC的放大器提出了挑战。为了在驱动ADC的同时获得极小的噪声和信号失真,有必要设计一种无源网络接口,实现宽带噪声抑制和采样保持阻抗的变换,从而为驱动放大器提供一个更匹配的负载阻抗。建议在多个常用IF频率下采用谐振法将采样保持阻抗变换为可预测性的负载,从而更地设计抗混叠滤波器。

抗混叠滤波器

抗混叠滤波器由四阶巴特沃兹低通滤波器和谐振电路组成。谐振电路通过谐振消除ADC负载的容性部分,有助于确保ADC输入在目标中心频率看起来像一个真正的电阻(参见应用笔记AN-742和AN-827)。整体频率响应呈现出带通特性,有助于抑制目标奈奎斯特频率区域外的噪声。一般而言,若用一个恰当阶数的抗混叠滤波器,SNR性能会提高数个dB.

低通滤波器

用作抗混叠滤波器的低通滤波器往往采用LC网络设计,必须完好定义源阻抗和负载阻抗以获得所需阻带。为设计滤波器网络,可使用各种滤波器合成的手册。通常用切比雪夫(Chebyshev)或巴特沃兹(Butterworth)多项式来定义滤波器传递函数。有几种基于软件的滤波器设计程序有助于简化这一问题,如来自Nuhertz Technologies的Filter Free 4.0或Agilent Technologies推出的Advanced Design System(ADS,设计系统)。

RL/RS滤波器比和滤波器阶数必须小心对待,其中RS为滤波器源阻抗,RL为负载阻抗。增加阶次会增加不必要的复杂度,递减效益,所以本应用笔记建议采用差分四阶巴特沃兹滤波器。

谐振匹配

谐振匹配或储能电路有助于确保ADC输入在目标中心频率处看起来像一个真实电阻(详情见AN-742和AN-827应用笔记)。分流电感L5与片内ADC输入电容和低通滤波器C4所提供电容的一部分并联,形成一个谐振电路。

谐振电路的窄谐振频带可为抗混叠滤波器提供整体带通频率响应,从而有助于抑制目标奈奎斯特频率区域外的噪声。

抗混叠滤波器设计步骤

第1步-确定接口特性

此推荐方法的步是充分收集ADC接口所涉及所有元件的要求信息。基本要求清单包括

滤波器规格-中心频率和带宽等要求?

抗混叠来源及负载阻抗-定义为差分驱动器输出和?性能所需的负载(见表1)

ADC(跟踪模式)输入阻抗-Excel格式的S参数,可?从器件网站的评估板部分获得。

第2步-查找标准归一化原型值

可通过滤波器设计手册查找单位标准归一化原型滤波器值,然后按照比例求出所需截止频率和负载阻抗的相应值。表2所示为相关原型值的一些近似值。

表2. 四阶巴特沃兹原型元件值

为了补偿谐振电路匹配的额外衰减,截止频率应为所需通带高端的125%.例如,如果需要一个20 MHz带宽、中心频率为140 MHz的滤波器,截止频率应设为(140 MHz + 20 MHz ÷ 2)× 125% = 188 MHz.

图4(a)显示单端四阶单位标准归一化原型滤波器的一个示例。所示巴特沃兹滤波器在2:1负载-源阻抗比下提供平坦响应,无纹波。

第3步-按频率和负载比例调整标准归一化原型值。

现在可以将单端单位标准归一化原型滤波器值Cn或Ln按比例调整到所需截止频率fcut和负载阻抗R.变换公式如下:

图4(b)显示的是截止频率为188 MHz、负载阻抗为200Ω的单端等效网络。

第4步-通过分割串联电抗将单端等效网络转换为差分网络。

具有高动态范围IF采样功能的多数高速ADC都采用差分输入接口。因此,有必要将单端网络转换为差分网络,如图4 (c)所示。转换为差分网络时,串联阻抗值减半。

图4. 原型滤波器设计步骤。

第5步-消除ADC输入端的原始开关电容。

在谐振匹配或储能电路中的分流电感有助于消除片内ADC输入电容(以及在低通滤波器外增加的任何额外电容)。电感值必须以谐振方式抵消虚部导纳,仅剩下复合阻抗的导电部分。

例如,AD9640差分输入阻抗在140 MHz下为4.7kΩ,与3.9pF并联。

因此所需电感L为331 nH.

注意,L/C比是决定Q和选择性的因素之一。对于并联谐振电路而言,电感越高,电容越低,通带滤波器带宽越大。为了获得更大的窄带响应,可通过并联添加额外电容来获得更高Q值(除低通巴特沃兹滤波器的电容级外)。在下列公式中,添加了一个额外10 pF,将所需电感L降低至93 nH:

因此,Q值越低,响应带宽也就越低。

第6步-装配。

计算好每个接口元件后,可将电路装配在一起进行仿真。通常情况下,为获得滤波器要求的组合,需要借助一些仿真试验和误差来优化网络接口。利用可准确体现实际L值和C值寄生效应的真实元件模型(s参数)来模拟网络响应是有利的。

采用理想L值和C值的实施方案如图7所示。注意,考虑电路板走线的寄生串联感应,终实施可以选用电感值稍低的电感。还需要注意的是,图4(c)中的负载被图7中的ADC接口取代,包括一个并联电感和多个共模偏置电阻。偏置电阻给各差分输入端提供所需的直流偏置,并与ADC输入阻抗和谐振并联电感为滤波器组成一个负载。

图7. AD8352和AD9640的ADC接口示例,理想元件

第7步-电路板级经验调谐。

采用的实际L值和C值的终实施方案如图8 所示。在使用终仿真值填充电路板后,可能需要一些板级经验优化方法来帮助补偿实际PCB寄生效应。

图8. AD8352和AD9640的ADC接口示例,实际元件

为此,建议使用优良软件和s参数在工艺早期进行详细的仿真。这样,可以减轻更耗时的板级调谐工作。在一些实例中,可能需要为印刷电路板寄生电容建模以选择的L值和C值。

图5和6显示AD8352和AD9640间接口的性能。

图 5. AD8352和AD9640接口示例的滤波器响应

图 6. AD8352和AD9640接口示例的通带平坦度

布局布线考虑

如果滤波器元件值较小,额外的寄生电容会导致大比例的变化,此时降低电路板杂散寄生电容非常重要。为了使本文所讨论的电路达到理想的性能,必须采用出色的布局、接地和去耦技术。至少应采用四层PCB:一层为接地层,一层为电源层,另两层为信号层。有关具体电路板建议,请参看各个器件的驱动器放大器和ADC数据手册。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。