摘要:针对专用SoC芯片的安全问题,在描述芯片威胁模型与部署模型的基础上,规划了芯片资源的安全等级,设计了芯片的工作状态及状态转移之间的约束条件和实现机制,给出了芯片运行时的安全工作流程。对芯片的安全性分析表明,所设计的芯片系统能够满足机密性、完整性和可信性的应用要求。

引言

为了满足智能卡和可信计算应用需求,设计实现了一款专用SoC芯片。该芯片由微处理器、程序和数据存储器及管理模块、安全逻辑模块、密码服务模块、辅助功能模块、I/0接口组成,能为各种安全应用提供机密性、完整性和身份等多种密码服务,以及数据存储、访问控制、安全计算等应用。

专用SoC芯片的安全控制架构设计,首先应对芯片的应用环境进行分析,得到芯片的威胁模型与部署模型,即芯片的潜在攻击者和可能的攻击方式,以及芯片的生产、运输、研发和使用等环节存在的风险问题;其次是根据芯片安全要求与功能规范,通过软硬件协同设计方式,设置相关硬件逻辑、状态寄存器和参数存储区,并实现相关安全策略的软件控制流程;对所设计的系统进行安全性分析、仿真验证与FPGA测试。

1 芯片系统安全体系结构设计

基于芯片系统的生产与应用实际,根据受保护资产对芯片安全性影响重要程度和信息技术安全性*估准则,芯片的受保护资产可设计为如下3种安全级别。

0级资产:O层代码的完整性与可信性,0层数据(LEVEL0)的机密性、完整性和可信性,以及芯片各模块功能正确性。0级资产是芯片系统的安全基础,对任一项的保护失败均将导致整个芯片系统拒绝提供任何服务。

1级资产:1层代码的完整性与可信性,1层数据(LEVEL1)的机密性、完整性和可信性。1级资产是系统运行的控制态和2级资产的安全基础,对1级资产的保护失败将禁止本层代码及2层代码的执行。

2级资产:2层代码完整性与可信性,2层数据(LEVEL2)的机密性、完整性和可信性。2级资产是芯片系统上层的受保护资产,对本级资产的保护失败会导致本层代码被禁止运行。2级资产在芯片系统中可以同时存在多个,但每一时刻只有1个投入运行。

1.1 芯片系统安全状态设计

芯片加电运行后,通过执行一系列的命令,获得不同的安全权限,从而也处于某一特定的安全状态。

ST1:出厂初始状态。在信任制造商前提下,芯片在出厂初始状态是可以信赖的。初始状态是芯片的可信基。

ST2:芯片使能状态。首次加电时,上电自检及传输安全通过后,芯片所处的状态。芯片在验证各功能模块正确,且。层代码、数据完整性校验通过后,接收传输过程安全命令,并利用开发商与制造商的共享秘密,在允许的次数范围内对芯片进行真实性。

ST3:芯片激活状态。处于使能状态下的芯片,允许开发商通过用户创建命令完成用户创建。在这一过程中,芯片对开发商身份的合法性依赖于传输安全时的共享秘密。用户创建完成后,置位芯片激活状态标识与所有权获得标识。再次启动时,对开发商的身份合法性依赖于输入的共享秘密,以及开发商创建的用户密钥。

ST4:1层代码允许状态。为满足芯片使用灵活性的要求,芯片的1层代码可由开发商进行配置。代码需对命令的发起者进行身份,在允许次数范围内,若身份正确,则置位1层代码允许标识,芯片进入1层代码(芯片操作系统)允许状态。

ST5:1层代码完成状态。在控制程序的控制下,完成1层代码。完成后,控制程序调用SHA1模块,对1层代码进行完整性度量与存储,并与输入的代码完整性信息进行比较。若完整性验证正确,则置位1层代码使能标识位。

ST6:1层代码运行状态。芯片系统可以由ST3和ST5转入1层代码运行状态。在进入此状态前,需判断1层代码使能标识是否有效,并在验证1层代码及数据完整性正确后进入代码运行状态,执行相应程序完成预定功能。

ST7:2层代码(用户应用程序)允许状态。2层代码的与调用均在1层代码监控下完成。在1层代码运行状态下,若用户输入2层代码命令,1层代码首先代码命令发起者身份。在允许的次数范围内,若身份正确,则置位本层敏感信息存储器中的2层代码允许标识位,芯片进入2层代码允许状态。

ST8:2层代码完成状态。与1层代码的过程相同,通过调用控制程序,完成2层代码的。完成后,1层代码对2层代码进行完整性度量与存储,对比验证输入的完整性信息。若完整性验证正确,置位LEVEL1中的2层代码使能标识位。

ST9:2层代码运行状态。当2层代码和数据完整性验证正确后,芯片系统可以由ST6和ST8转入2层代码运行状态。当2层代码使能标识有效时,芯片系统可以在ST6或ST8下,通过层次跳转指令,进入2层代码运行状态。在ST6状态下,芯片系统还可通过调用2层代码来完成其相应运算与控制功能。与层次跳转进入ST9不同的是,通过调用2层代码来完成其相应功能时,在2层代码执行完毕后,芯片系统可以返回到ST6。而通过层次跳转命令进入ST9时,完成规定的功能后,芯片系统保持在ST9,或者通过系统复位返回ST3,不允许其返回ST6。

1.2 状态位与控制参数设置

为实现上述各状态之间的正常跳转,芯片系统需要设置相应的状态位与控制参数,以寄存芯片运行时的控制信息和工作状态。状态位与控制参数设置是芯片安全体系结构建立的基础,基于芯片的权限状态划分,参照TPM与ATMELSC系列安全芯片对状态位与控制参数的配置,将LEVEL0作为专用SoC芯片状态位与控制参数的存储区,其具体设置如表1所列。

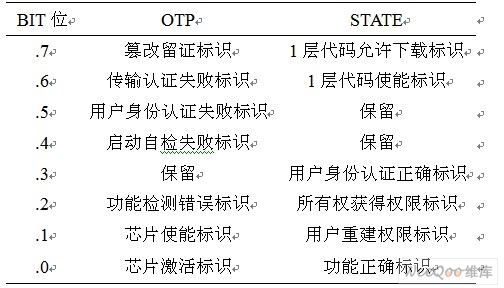

表1 LEVEL0状态位与控制参数配置表

在表1中,OTP(One Time Programmer)区是性编程区,用于芯片性设置的权限标识与状态留证。STATE为系统状态标识,用于标识芯片当前的权限状态信息。OTP与STATE中各位的作用与位的对应关系如表2所示,其中各位均为高电平有效。

表2 OTP与STATE中状态位功能表

M_AUTH为制造商与开发商的共享秘密,M_PUBKEY为制造商公钥,SN为产品序列号,它们共同用于芯片的传输过程安全。EK(Endors- ement Key)为芯片系统的身份密钥对,在实际应用过程中,芯片通过调用EK私钥对数据进行签名,以表明自身的合法身份。AIK(Attes-tation Identity Key)为开发商身份密钥对,在用户身份创建过程中由片内随机数与RSA算法IP核生成,用于用户的身份。PCR(Pla-tform. Configuration Register)是平台配置完整性寄存区。为满足专用SoC芯片在进行FPGA测试时对芯片系统的硬件规模限制,暂时为芯片系统配置了8个PCR,每个 PCR寄存器为20个字节。除PCR6和PCR7外,其余各PCR寄存器存储信息的表达式如下所示。

PCR0 = SHA1(DOWNLOAD)

PCR1 = SHA1(LEVEL0)

PCR2 = SHA1(COS)

PCR3 = SHA1(APPLI)

PCR4 = SHA1(LEVEL1)

PCR5 = SHA1(LEVEL2)

DIR(Data Integrity Register)是芯片系统的数据完整性寄存器,寄存芯片内部数据与代码的完整性信息,具体设计时,为芯片系统配置了3个DIR,分别存储三个层次的数据与代码的完整性,各DIR寄存器存储信息的表达式如下。

DIR0 = SHA1(PCR0||PCR1)

DIR1 = SHA1(DIR1||PCR2||PCR4)

DIR2 = SHA1(DIR1||DIR2||PCR3||PCR5)

USER_AUTH为用户与芯片系统的共享秘密,在用户创建时通过相应命令输入,完成用户的身份合法性验证。ERROR_SIG为错误次数寄存器,用于芯片系统对字典攻击的防护。ATTACK_EVI是攻击留证寄存器,对芯片系统所遭受的物理攻击次数与方式进行寄存。

2 芯片工作流程分析

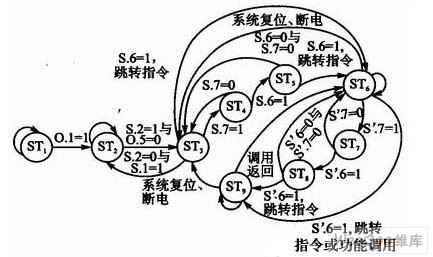

专用SoC芯片在其整个生命周期中,总处于某种特定的安全状态。基于芯片运行时的安全策略,结合状态位与控制参数设置,专用SoC芯片的状态转移流程如图1所示。

图1 芯片状态转移流程图

在上图中,S.n表示STATE的第n位,S’.n表示STATE’的第n位(位于LEVEL1中),0.n表示0TP的第n位。高电平表示对应条件成立,低电平表示对应条件不成立。

2.1 状态转移约束条件

专用SoC芯片按照其工作流程共有16种不同的状态转移路径,限于篇幅在此只介绍其中的一种状态转移路径。为简化书写记A=TDESENC(KEY_TDES,DATA_T),B=RSAENC(PUB EK,DATA R)。

当专用SoC芯片从ST3状态通过ST6状态转移到ST9状态时,应满足如下约束条件:

在正常启动时,芯片系统由ST3经过上电白检,完成对1层代码与数据、2层代码与数据的完整性验证。置位STATE.6,通过层次跳转命令,进入ST6,进而在ST6下,通过判断STATE’.6是否有效,决定可否进入ST9。在ST6下,也可通过功能调用命令进入ST9,执行部分2层代码的功能,并在执行完成后,正确返回到ST6。

2.2 专用SoC芯片的工作流程

①在开发商初次获得芯片后,系统处于初始状态ST1。加电后,系统首先对自身O层代码和数据区进行完整性检验,调用各功能模块IP核进行自检,若白检正确,则芯片可继续完成传输过程安全命令的接收与执行,否则置位OTP.4,芯片系统进入锁死状态,不提供任何功能服务。

②当OTP.1=0时,芯片系统仅允许传输过程安全命令的输入与执行。开发商通过传输安全命令,在允许的次数范围内,对芯片的真实性进行。若正确,芯片由初始状态ST1转移至使能状态ST2,并置位芯片使能标识OTP.1,等待用户创建命令的输入。若芯片真实性错误,芯片系统保持在初始状态。当次数超出允许次数时,OTP.6被置位,芯片被锁死。

③当OTP.1=1时,芯片系统仅允许用户创建命令的输入与执行。初次启动时,开发商通过用户创建命令,完成AIK与USER_AUTH的创建。用户创建完成后,置位OTP.O与STATE.2,进入芯片激活状态ST3。在允许的次数范围内,若用户创建失败,芯片保持在ST2。当STAT-E.1=1 时,开发商可以通过用户创建命令,更新AIK和USER_AUTH,完成用户身份的重建。当次数超出允许范围时,0TP.5被置位,芯片被锁死。

④当OTP.O=1时,开发商可以获得低层代码和系统资源所提供的服务功能,如SHA1杂凑值计算、对称数据加解密、RSA数据签名与、以及随机数生成等一系列密码服务功能等。当需要对芯片系统进行1层代码时,用户输入代码命令,芯片系统首先验证命令发起者身份,若身份验证正确,置位 STATE.7,进入ST4。

⑤当STATE.7=1时,芯片在控制程序控制下,将1层代码到对应存储器COS区。系统调用SHA1模块度量代码的完整性,存储于 LELVE0存储器的PCR2中,并与输入的完整性信息进行对比验证。若完整性验证通过,置位STATE.6,并复位STATE.7,进入ST5,否则返回ST3。此外,因突发因素导致过程中断,也会使芯片系统返回ST3。在系统返回ST3时,复位STATE.7。

⑥当STATE.6=1时,通过层次跳转命令,芯片系统进入ST6,用户可以获得1层代码的相应功能。由ST6返回到ST3只有断电或者系统复位两种方式。

⑦在1层代码运行状态下,若需要进行2层代码,则用户输入符合1层代码编码格式的代码命令。1层代码验证命令发起者身份,验证通过后,置位STATE’.7,进入ST7。若不需要代码,则在ST6运行。

⑧完成2层代码过程同⑤,对2层代码进行完整性度量与验证,若验证通过,置位STATE’.6,进入ST8,否则返回ST6。

⑨通过层次跳转命令或功能调用命令,芯片系统可进入ST9,获得2层代码相应功能。当采用层次跳转命令进入ST9时,芯片系统保持在ST9状态,仅能够通过系统复位,返回ST3。当采用功能调用命令进入ST9时,只能执行2层代码中部分功能且执行完毕后,将返回到ST6状态。

3 专用SoC芯片安全性分析

3.1 攻击防护分析

在芯片的硬件安全结构设计中,篡改响应机制能够对既定攻击模型中的物理攻击进行安全防护;结合安全逻辑模块中的越界检测部件,信息交互机制能够防止攻击者对芯片的缓冲区溢出攻击;此外,信息交互机制还能够对语义攻击、字典攻击以及重放攻击进行防护;芯片系统的单向分级启动模式、以及代码时的身份,各安全级别之间的“防火墙”设计,使得芯片系统能够抵抗恶意代码的攻击。

3.2 工作过程安全性分析

①代码的可信性:首先,由于制造商被无条件信任,芯片在出厂初始状态真实可信,因而内嵌代码是可信的。在经过传输过程被开发商获得后,芯片的使用需要通过对芯片的传输过程进行验证,在验证正确后,芯片的来源被确认,此时,内嵌代码保持了其可信性。以内嵌代码为可信基,在对1层代码与2层代码进行时,均需要命令发起者的身份。因而,的1层代码与2层代码均能够保证其来源真实性。

②代码的完整性:在信赖制造商前提下,内嵌代码可作为整个芯片系统的可信基。基于这一信任基础,通过启动过程中对内嵌代码、芯片操作系统、用户应用程序的完整性验证,使得芯片系统仅在代码完整性正确情况下,才能够正常运行,从而保证了代码的完整性。

③数据可信性:由于LEVEL0的数据仅能够由制造商与Q层代码操作,传输安全机制保证了芯片的可信性,从而可知LEVEL0的数据是可信的。1层与2层敏感数据与运行临时数据的可信性由本层的代码可信性保证。当本层代码可信时,数据的来源被认为是可信的。

④数据完整性:由完整性机制可知,其被数据对象在每次合法改变时,均将及时修改相应的数据完整性检验信息,且每次启动时,均需进行完整性,因而数据完整性可得到保证。

⑤功能部件的正确性:功能部件的正确性通过芯片系统每次启动时的功能自检,以及根据应用需要每次调用功能部件执行相应检测功能来保证。

结语

提供密码服务和数据存储功能的专用SoC芯片设计的关键是,在芯片功能正确的前提下,确保芯片内部敏感信息的机密性与完整性,以及运行状态的可信性。本文为专用SoC的安全设计提供了一个可供参考的模型,也为进一步研究动态数据完整性度量和可信应用服务提供了一个基础平台。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。