1 引言

随着通信系统和网络的快速发展,要求数据的通信、处理和存储的安全性和可靠性越来越高。开发安全加密机器,要求具备实时加密,可改变密钥,使用多种算法等性能,因此可重用、参数化的加密核成为一种理想的安全加密设计。

目前加密算法有单密钥和公用密钥2种体制。单密钥体制中的是DES加密算法,它是目前应用广泛的分组对称加密算法,广泛应用于卫星通信、网关服务器、视频传输、数字电视接收等方面。文献指出,尽管软件实现的DES加密算法容易改变,但是其数据处理速率低;专用集成电路ASIC可提供高性能算法但灵活性差;而FPGA实现的加密算法具有对同一个FPGA使用不同算法的重新编程可增加其灵活性,使用同一个算法的不同版本和改变结构参数实现系统升级。因此利用FPGA实现DES加密算法是一种理想选择并具有实际的应用价值。

为了克服传统DES加密算法流水线的FPGA实现的子密钥需先后串级计算,密钥不能动态刷新的缺点,提出一种新的加密算法,提高DES FPGA实现系统的处理速度,增加系统的密钥动态刷新功能,提高系统的可重用性。

2 DES加密算法原理

DES加密算法是将64位的明文输入块变为64位的密文输出块,其密钥是64位,其中8位是奇偶校验位。整个算法的处理流程如图1所示。

从整体结构来看,DES加密算法可分为3个阶段:

(1)对于给定的明文m,通过一个(固定的)初始置换IP重新排列m中的所有比特,从而构造比特串m0。把64位比特串m0拆分成左右2个部分,即m0=IP(m0)=L0R0,这里L0由m0的后32位组成。

(2)计算16次迭代变换,所有16次迭代具有相同结构。第i次迭代运算是以前迭代的结果和由用户密钥扩展的子密钥Ki作为输入;每迭代运算只对数据的右半部分Ri-1进行变换,并根据以下规则得到LiRi作为下一轮迭代的输入 表示2个比特串的异或(按位模2加)。其中每一轮次运算的子密钥Ki是将56位密钥分成2个部分,每部分按循环移位次数表移位并按置换选择表置换得到。轮函数f的处理过程:先将Ri-1进行E置换,再与本轮的子密钥相异或,将S盒字替换和P置换。图2是DES算法的一轮处理框图。

表示2个比特串的异或(按位模2加)。其中每一轮次运算的子密钥Ki是将56位密钥分成2个部分,每部分按循环移位次数表移位并按置换选择表置换得到。轮函数f的处理过程:先将Ri-1进行E置换,再与本轮的子密钥相异或,将S盒字替换和P置换。图2是DES算法的一轮处理框图。

(3)对16次迭代变换的结果使用IP置换的逆置换IP-1,所得到的输出即为加密后的密文。

3 DES加密算法的FPGA实现

3.1 系统总体设计

DES加密算法是以多轮的密钥变换轮函数和密钥+数据运算轮函数为特征,与之相对应的硬件实现.既可以通过轮函数的16份硬件拷贝,达到深度细化的流水线处理,实现性能优化,即性能优先方案;也可通过分时复用,重复调用一份轮函数的硬件拷贝,以时间换空间,从而得到硬件资源占用上的化,即资源优先方案。考虑到加密系统首先需满足实时处理要求,因此选用速度性能优先方案。

DES算法的迭代特征使其适用于采用循环全部打开和流水线结构设计。由于提前生成子密钥,并且用逻辑电路完成S盒设计,就可以解开DES算法的16次循环迭代为16级流水线数据块加密,实现16个数据块同时加密。这样,从第1个数据块开始加密,经16轮次延时后,每一轮次延时都会有一个数据块编码完成输出一个密文块。这样它的加密速度是循环式加密的16倍,而代价是面积增加16倍,但考虑到每个轮次都是组合逻辑运算,占用面积小,这样的代价完够接受。图3是基于子密钥预计算的DES算法流水线处理原理图。

3.2 子密钥的生成

DES算法每一轮次迭代都需要一个子密钥,采用流水线实现DES算法,就需要提前生成子密钥,随流水线进程发送给各个模块。输入密钥分别经置换选择1、第n轮的循环左移和置换选择2这3个步骤后得到第n轮的子密钥。如果用VHDL按照每一轮次循环移位的位数一步步得到16轮次迭代的子密钥,那么16轮次子密钥的生成需要做56x28次移位运算,同时需要56个寄存器存放每一轮子密钥的中间结果,这样不仅语言描述复杂,占有较多的硬件资源,而且每轮次密钥移位次数不同,需要的运算时间不同,会给算法的迭代运算带来更大的等待延迟。因此,通过分析得到生成每一轮子密钥时,相对输入密钥所需移位的数目,直接将各个子密钥提前生成。这样不仅降低了资源消耗,提高算法的执行速度,也消除了各个圈子密钥之问的相关性。

3.3 S盒的设计

S盒的设计是DES算法关键部分,S盒设计的优劣将影响整个算法性能。在采用FPGA实现时,应从资源和速度的角度出发,有效利用FPGA可配置属性,充分考虑器件内部结构,尽可能使两者都达到。S盒是一个4x16的二维数组,根据输入的6位地址数据确定输出,中间4位数据确定列,两边2位确定行,所产生的行列数据对应的地址空间中存放的就是输出的4位数据。为了利用FPGA内部的4输入查找表结构,可重新设计S盒的逻辑描述,即先固定2个变量,而使另外4个变量发生变化。实现时使用双重case语句,外层使用2个变量,对应S盒输入的第1、6位。内层使用4个变量,对应S盒输入的第2、3、4、5位。形成一个6输入、4输出的查找表。这样就可以充分利用FPGA的内部资源,提高综合效率,加快算法执行速度。

3.4 子密钥延迟控制

图3中的子密钥延迟控制单元可完成子密钥的延迟控制,它由一系列寄存器构成。通过时钟触发数据块依次向下传输给各级流水线,子密钥依次存入下寄存器,在相应数据块加密时从寄存器读取,便实现16个不同数据块同时加密。在新更换密钥时,各个子密钥分别存入寄存器(i,1),随时钟触发依次在流水线寄存器中流动,以前在流水线上继续使用的子密钥也同时在流水线寄存器中随数据块流动,通过合理使用寄存器,完成数据块和子密钥的同步,准确快速分发子密钥,实现密钥的动态更换。

4 仿真结果

采用VHDL作为设计逻辑描述.以OuartusⅡ作为设计开发工具,以Ahera公司Cyclone EPlCl2F324C6为目标器件,逻辑综合结果表明系统共占用4 368个逻辑单元(LE),系统的时钟频率为222.77 MHz,对信息的加密速度为222.77x64 Mb/s=14.26 Gb/s。由表1给出的DES算法有关硬件和软件实现性能对比结果表明,该系统的数据加密速度是快的,是软件实现的112倍.同时其资源消耗指标也较理想。

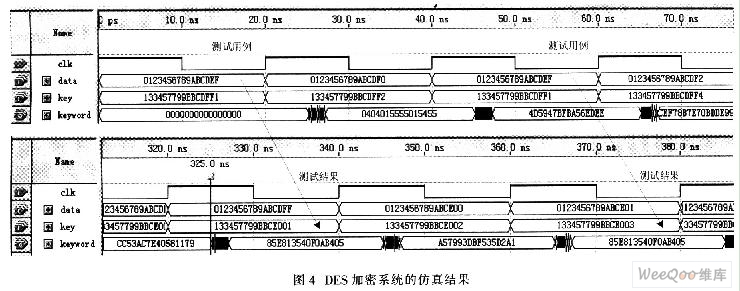

假设需要加密的明文M=0123456789ABCDEF H,密钥K=133457799BBCDFFl H,经过初始置换,16轮迭代加密,逆初始置换,终的加密密文应为:85E813540FOA8405H,其时序仿真结果如图4所示,仿真结果表明,系统完全实现DES算法的流水加密功能。

5 结语

在分析DES算法原理的基础上,详细阐述了一个基于VHDL描述、FPGA实现的DES加密算法系统的设计和仿真结果。该系统与传统软件加密系统相比,设计灵活,处理速度快,密钥可动态刷新,抗解密强度高,稳定性好,重用性强,升级方便。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。