摘 要:H.264作为的视频编码标准具有很高的压缩性能,对它的研究具有重要的意义。根据H.264的变换量化算法设计一种基于FPGA的高性能变换量化处理结构,该结构采用流水线操作和分时复用技术。结果显示,该设计既节省了资源,又保证了效率;能够同时处理整个4× 4块的全部16个残差输入数据,并在236个时钟内完成对1个宏块的残差数据从输入到反变换输出重建值的完整变换量化过程。它的处理速度和性能大大提高,可用于硬件加速。

0 引 言

H.264高效的编码效率是以其高复杂性为代价的,因此制约了它在高分辨率、实时处理等方面的应用。而FPGA器件采用流水控制策略和并行处理方式,可为H.264复杂的编码模块提供硬件加速引擎。变换量化模块在H.264编码算法中被频繁调用。因此研究在尽量合理控制其资源消耗的前提下,提高变换量化模块的工作频率及处理数据的吞吐量,并完成变换量化一系列完整功能的变换量化结构具有重要的实际意义,也成为当前研究的首要问题。H.264.变换是基于DCT的,其全部采用整数DCT变换,这样就避免了正变换和反变换的失配问题,既不丢失解码,也适合于FPGA硬件实现。

1 算法原理及分析

1.1 变换算法及分析

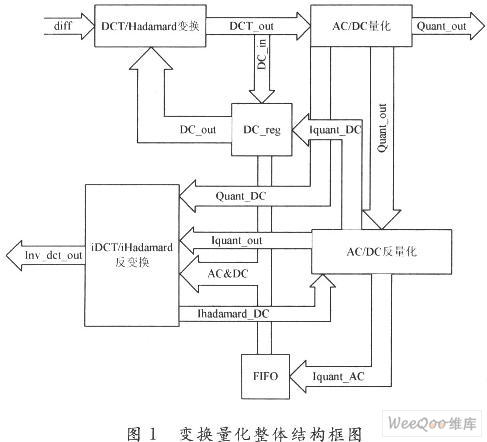

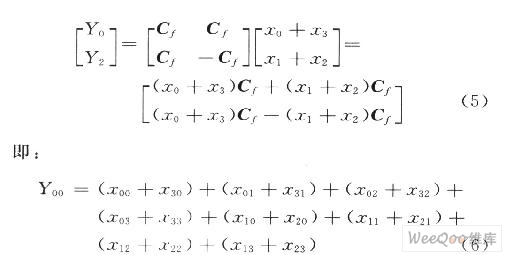

H.264变换是整数DCT变换,该算法实现了编码端和解码端反变换之间的零匹配,从而减少了解码的丢失。通常H.264变换编码以4×4块为单位,变换矩阵如下:

当变换矩阵中a=1时,为DCT正向变换矩阵Cf,;若将DCT正向变换矩阵Cf,中所有的2变为1,并保持所有符号不变,则变成Hadamard变换矩阵Hi;若将以上矩阵中所有的2变为1,并使a=1/2,保持所有符号不变,则为DCT反向变换矩阵CTi。

1.2 量化算法及分析

H.264的分级标量量化器支持多达52个量化步长QSTep,用量化参数QP进行索引。范围广阔的量化步长能够灵活准确地控制比特速率和质量之间的平衡。

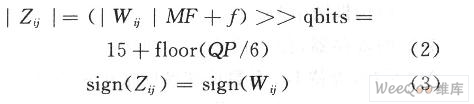

在整数算法中,量化过程可以用以下运算来实现:

式中:W为残差系数;>>表示二进制右移;帧内块和帧间块f分别为2qbits/3,2qbits/6;MF为乘法因子,其值可根据W(i,j)在矩阵中不同的位置和量化参数QP的不同,查乘法因子表得到。

系数z的反量化方式如下:

式中:尺度因子V可根据Z(i,j)在矩阵中不同的位置和量化参数QP的不同,查尺度因子表得到。

2 FPGA硬件设计及实现

2.1 变换量化硬件整体结构

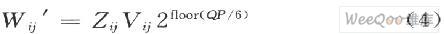

在H.264编码器中经过预测后得到的残差数据经过变换T、量化Q后的数据分为两路:一路经过重排序Recoder后用于熵编码;另一路为重建通路,经过反量化Q-1、反变换T-1后与预测值P相加得到重建值,用于后面的宏块的预测编码。

H.264编码标准中,在帧内预测方式下,首先对16×16宏块(亮度分量)的1*×4块进行DCT变换,然后提取出DC系数组成一个4×4 DC块;对于这个4×4 Dc块要先进行Hadamard变换,然后量化。在重建通路中需要注意:对于4×4 DC块,要先进行反Hadamard变换,再进行反量化,目的是使反变换的动态范围;再依据这个4×4 DC块中16个数值对反量化后的16×16宏块进行反DCT变换。对于色度分量的DC系数也是一样需要经过进一步变换。H.264变换量化整体结构主要分为4大模块,其框图如图1所示。

结构框图中DC_reg是一组用于存储所有的DC系数值的寄存器,使用两个同步FIFO存储反量化后的AC系数,等待DC系数反变换反量化完毕以后,再一起送人的反DCT变换模块中进行处理。两个同步FIFO在时钟控制下先后进行写操作,其中一个存储4×4块反量化输出的其中两行数据,另一个在下一时钟存储这个4×4块反量化输出的另两行数据。读取时,则同时对两个FIFO进行读操作,即一个时钟内这个4×4块的反量化后的全部16个数值同时出现在反变换模块的输入端。

2.2 变换模块(DCT/Hadamard变换)及反变换模块

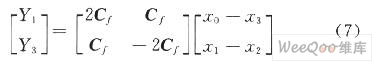

(iDCT/iHadamard反变换)设计由DCT变换矩阵可以推导得出:

同样:Y01~Y03以及Y20~Y23也可将式(5)展开得到。同理可得:

由前述的变换算法分析可知,Hadamard变换和DCT变换的变换矩阵只存在是否乘以2的差别,因此将式(5)和(7)中的cr换成Hi,且2变为1,由此可得到Hadamard变换。

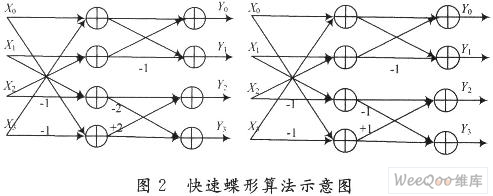

在实际的硬件电路中,乘以2和除以2的操作都可以通过移位来实现。此外,DCT正向变换与Hadamard变换在整个变换过程中不是同时进行操作,因此将 DCT正向变换与Hadamard变换结合到一起,并分时复用,以是否乘2来区分当前是哪种变换。同时采用16个残差数据同时输入,输出8位变换数据,每 2个时钟输出一个4×4块的变换结果。这样既充分利用了硬件资源,又能性处理一个4×4残差块的全部16个数据,确保了效率。DCT变换和 Hadamard变换的变换均可用快速蝶形算法实现,如图2所示。

对iDCT反向变换和iHadamard反变换的变换进行分析,原理与上述相似。

2.3 量化及反量化模块设计

整个量化及反量化模块全部采用乘法器、加法器和移位操作来实现,并采用FPGA内部的两个ROM来分别存放正反量化的乘法因子MF和尺度因子V。

由于变换模块输出是8位,因此量化模块采用8数据输入,每2个时钟输出一个4×4块的量化结果。反量化模块也是采用8数据输入,且每2个时钟输出一个4×4块的反量化结果。

3 时序分析及硬件调试验证

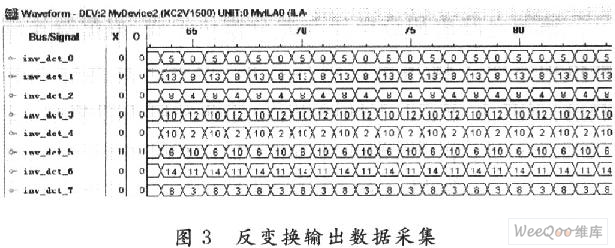

该结构设计全部采用VHDL编写程序,使用ISE环境下的XST进行综合,综合频率达到112 MHz。该设计采用的FPGA是Xilinx公司生产的XC2V1500,并使用在线逻辑分析仪Chipscope来观察量化输出数据 (quant_out_i)和反变换后的残差输出数据(inv_dct_i);图3所示为反变换后的残差输出数据(inv_dct_i)。输入数据采用数值相同的4×4块,因此输出数据也完全相同。波形显示:每次输出8个数据;对于一个宏块的16个亮度4×4块进行处理时,可在45个时钟内完成变换量化 (包括AC/DC)用于编码,在91个时钟内完成变换量化反变换反量化一系列操作得到用于重建的残差,在236个时钟内完成对一个宏块的残差数据从输入到反变换输出重建值的完整过程。

4 结 语

提出的这种H.264变换量化结构完全基于FPGA实现,每一个时钟输出8个数据,每2个时钟得出对一个4×4块处理的终结果。一方面采用流水线操作,对16个数据并行处理提高了数据的处理速度,另一方面分时复用技术又在一定程度上节省了硬件资源。相比文献中只实现了部分功能,本文实现了从残差输入经变换量化、反变换反量化得到用于重建的残差值这一系列完整的操作,并保证了在一定的数据处理速度下对资源的优化处理,适合用于H.264.编码器硬件加速。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。