摘要:为满足雷达中频数字化接收机通用性设计要求,给出基于可编程的四通道数字下变频器ISL5416结合高速A/D器件AD*5实现通用中频数字接收机的设计方案。利用AD*5实现直接中频采样,在ISL5416中完成频谱搬移,数字滤波和抽取,实现数字下变频到基带;用FPGA实时控制,给ISL5416配置参数和系统时序控制。详细讨论了数字滤波器的设计和仿真。测试结果显示,系统动态范围大,镜像抑制比高,这是模拟中频接收机不具有的。整个系统集成度高,可靠性好,使用灵活,已在多个雷达产品中运用。

0 引 言

数字化接收机是软件无线电的重要内容,软件无线电的主要思想是将数字化推向前端,即将模数/数模转换器(ADC/DAC)尽量设在射频端,它是理想的软件无线电实现方法,也是数字化接收机的发展方向。早期的数字化接收机受模数转换器件(ADC)水平的制约,采用正交双通道零中频方案,即通过变频将射频变换到零中频(基带),正交解调得到模拟的正交信号,再进行数字化。由于该方案的主体变换都在模拟部分实现,数字化工作较少,不是真正意义上的数字化接收机。实现起来设备量较大,而且该方案中的正交混频器是模拟器件,得到的正交I,Q信号很难保证幅相正交。目前理论和实现上较成熟的数字化接收机方案是中频数字化接收机,即将射频信号经低噪声放大,经或二次下变频后,在中频(或高中频)直接采样,在数字下变频到基带得到正交的I,Q信号。目前,中频数字化接收机已在通讯、雷达上普遍使用。为适应灵活多样的模式,建立一个通用的中频数字化处理平台是十分必要的,现在有较高性价比的专用DSP芯片也为中频数字化接收机的实现提供了有力的硬件支持。ISL5416以其强大的可编程能力,使得中频数字化接收机的设计变得更为灵活和方便。本文即是采用专用DDC芯片ISL5416实现雷达中频数字化接收机的一例。该设计非常方便地在信号中频实现了数字化,而且可通过配置不同参数,实现不同模式、不同频率的接收和解调。

1 设计原理

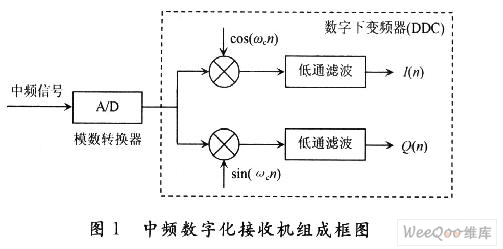

中频数字化接收机主要由模数转换器(ADC)、数字下变频器(DDC)组成,如图1所示。其中,A/D主要完成对模拟中频信号进行采样,得到数字化的中频信号,DDC将感兴趣的信号转换至基带,同时做抽样率变换及滤波处理,得到正交的I,Q信号送后续的数字信号处理器(DSP)进行基带信号处理。DDC是整个中频数字化接收机的,DDC由数控振荡器(NCO)、混频器、低通滤波器和抽取器组成。

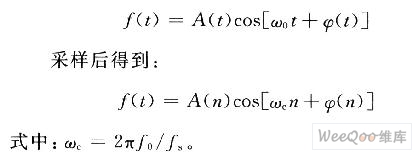

设输入模拟中频信号为:

本地数字振荡器(NCO)产生的正交信号为:cos(ωcn)和sin(ωcn),与中频信号在混频器相乘后得:

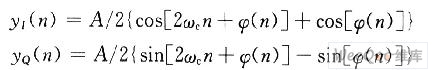

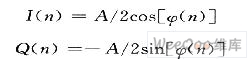

通过低通滤波器滤除倍频分量后,可以得到有用的正交I,Q信号:

由于信号的采样频率较高,也就是上式的I(n),Q(n)速率很高,一般远大于窄带信号的带宽,这时可对其进行速率转换(抽取),以降低此时的输出数据率。不过,抽取后的数据率应不小于信号带宽。在此之前,需经抗混叠滤波器滤波,以保证信号可靠完整地恢复。

图1中的中频信号是中频带限信号,如果此时中频信号的中心频率较低,可取高采样时钟过采样,依Nyquist采样定理,取采样率fs>2fH采样(fH为信号的高端),能够不混叠地恢复原信号。如果此时中频信号的中心频率较高,采样率与信号中心频率的关系不满足Nyquist采样定理条件,这时考虑是否满足带通信号的采样定理。这个定理是中频信号采样的理论依据,而Nyquist采样定理是带通信号采样定理的特例。带通采样定理:如果一个中心频率为fo频率带限信号,其频率限制在(fL,fH)内。

fo=(fL+fH)/2,当采样时钟fs与fo满足关系:

式中:n取能满足fs≥2B的正整数,B=fH-fL,则用fs进行等间隔采样,所得到的信号采样值能准确地确定原信号。

满足式(1)的中心频率为fo的信号经采样时钟fs采样后,f(t) 展开项中 cos(2 πfon/fs) 与sin(2πfon/fs)交替取值为零,当它们不为零时,取±1。可交替得到I,Q样值,不过这时的I,Q值已是经二分之一抽取,时域相差半个采样点,这时的I,Q值要在时间上对齐,符号修正,这样就很方便地实现了下变频。之后,只要将处理后的数据经数字滤波器滤波,按合适的抽取因子抽取就可得到所需的I,Q值。这种方法特别适合用FPGA设计的数字下变频器,不需要NCO,节省了设计数字混频器的逻辑资源,而且早期的商用数字下变频器件也是这种数字混频器,要求fo,fs满足式(1)的关系,如HARIS公司(现为Intersil公司)的HSP43216。

当信号中心频率fo较高,即是高中频信号时,用fs对信号采样属欠采样。当然fo,fs不一定严格满足式(1)的关系。fo,fs选用的总原则是从频谱上分析,采样后的信号经混频、滤波和适当抽取后,基带频谱没有混叠。本设计只是构建一个通用平台,以下的设计用采样率80 MSPS时钟采样,中频信号为中心频率10 MHz,带宽2 MHz,输出数据率2.5 MSPS。采样率和信号的频率满足过采样关系。

2 器件选用及参数设计

设计中的主要器件:模数转换器和数字下变频器分别选用AD公司的AD*5和Intersil公司的ISL5416,这两款器件都是具有较高性价比的器件。AD*5是高速、高性能的模数转换器,具有14 b,105 MSPS采样率。该芯片是目前用于直接中频采样的性能较好的一款芯片,片内包括采保和参考时钟,提供CMOS兼容的输出,输入信号带宽可到270 MHz。

AD*5的采样时钟要求质量高且相位噪声低,如果时钟信号抖动大,信噪比容易恶化,很难保证。为了优化性能,AD*5的采样时钟采用差分形式。时钟信号可通过一个变压器或ECL的差分芯片交流耦合到A/D的时钟输入引脚。

数字下变频器ISL5416是四通道宽带可编程下变频器,专为大动态范围应用而设计,输人数据率可达95 MSPS,片内包含数控振荡器(NCO)、数字混频器(Mixer)、数字滤波器(CIC和FIR)、自动增益控制AGC和重采样滤波器等。四个并行16 b定点或17 b浮点输入通道,NCO控制字是32 b可编程的、无杂散动态范围SFDR>110 dB。数字滤波器包括可编程级联的CIC滤波器,两个可编程的FIR滤波器级联,个FIR滤波器为32阶,第二个FIR滤波器是64阶,每个数字滤波器后接一个可编程抽取计数器,整个器件的总抽取比可从1~4 096。数字AGC增益范围可达96 dB,,内部数据通道是20 b宽度。

时序控制和信号预处理芯片采用Altera公司的A-PEX系列的一款器件。该芯片包括典型的200 000个逻辑门,片内带有逻辑存储单元,具有10*96 b RAM。运算速度和内部资源能满足时序控制和一般信号处理的要求。这个系统的时序控制电路采用Verilog硬件描述语言编程实现。

本系统采用AD*5实现模数变换,用ISL5416完成数字下变频,用FPGA进行时序控制,再配以外围电路构成中频数字接收机电路。用AD*5结合ISL5416是灵活设计中频数字接收机具有较高性价比的组合。

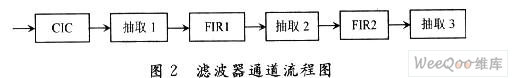

本设计的主要工作是ISL5416的参数选取,主要是数字下变频器芯片ISL5416的NCO和数字滤波器的参数设计和设置。NCO的频率设置范围为-109~+109Hz,本设计NCO选用10 MHz。中频信号经Mixer混频后,需经抗混叠滤波,首先是CIC滤波器,其后是2级FIR滤波器。CIC一般采取5级级联,5级级联可满足杂波抑制的一般要求。其后级FIR滤波器主要是进一步降低CIC后数据率,化FIR2的效能,FIR2提供终的滤波效果。中间包括三次抽取。一般抽取器放在滤波器之后,这样即可滤除高频分量,又可确保输出不混叠。图2是滤波器通道流程图。

FIR滤波器可借用专门的滤波器设计软件或Mat-lab软件设计。抽取因子的选取根据不同采样率或数据率进行选取,总抽取因子为各因子相乘,三个抽取器抽取比的选取,一般考虑将大抽取比放在CIC处,因为CIC只做位和加法运算,不做乘法运算,适合实时处理,灵活方便。经过大抽取后降低了后面FIR滤波器设计的压力。经滤波,抽取后总效果应做到心中有数,用Matlab进行仿真,以检验各滤波器设计是否合理。

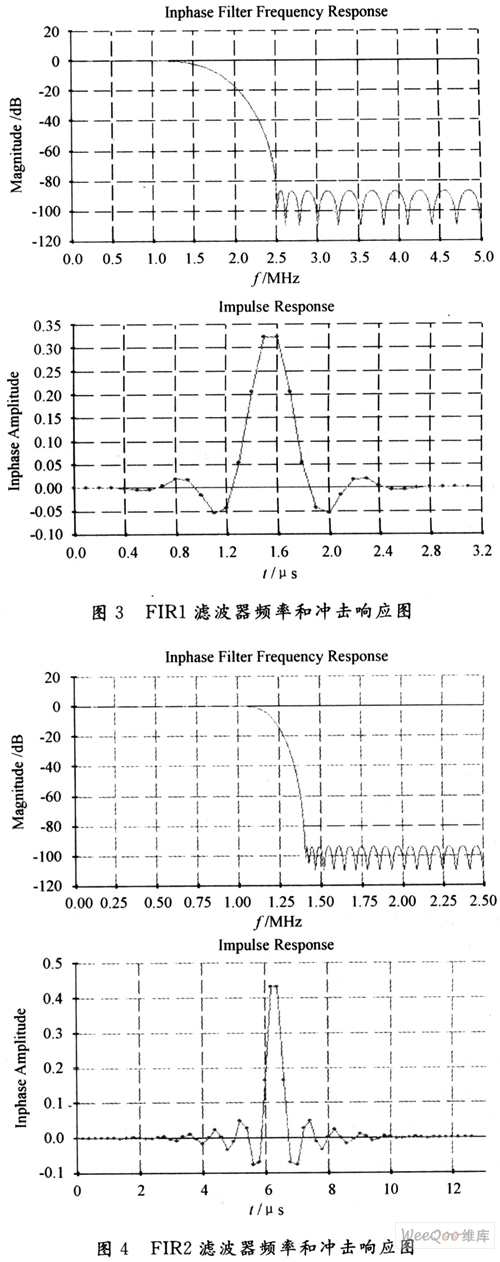

本设计滤波器考虑用5级CIC级联后8级抽取;32阶FIR滤波器后2级抽取;64阶FIR滤波器后2级抽取。这样的总抽取也实现了2.5 MSPS输出数据率。对于FIR1滤波器的设计参数:经8级CIC抽取后,其数据率为10 MHz。选定32阶的FIR滤波器的参数是:采样率10 MHz,通带1 MHz,止带2.5 MHz,通带起伏0.01 dB,阻带衰减80 dB,设计结果如图3所示。

对于FIR2滤波器设计参数:经2级FIR1抽取后,其数据率为5 MHz。选定64阶FIR滤波器的参数是:采样率5 MHz,通带1 MHz,止带1.4 MHz,通带起伏O.01 dB,阻带衰减80 dB,设计结果如图4所示。

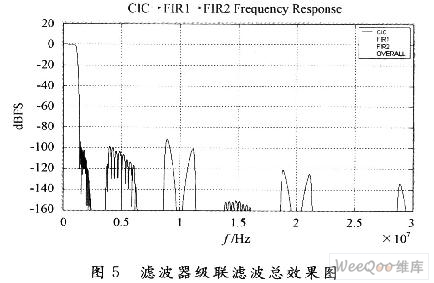

ISL5416经8级CIC滤波抽取,2级32阶FIR滤波抽取,2级64阶FIR滤波抽取后总效果用Matlab软件仿真如图5所示。图中显示了3个辛格函数(sinc)的旁瓣。从图5可以看出,带外抑制在90 dBFS以下能够满足实际要求。

3 测试结果和分析

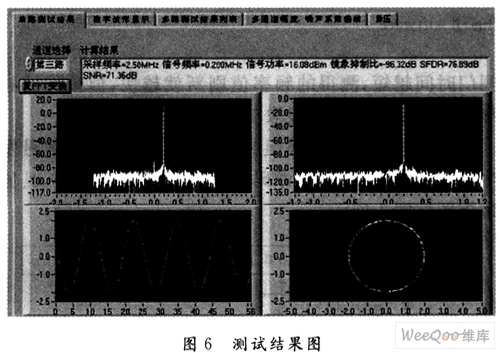

利用图形化编程软件LabVIEW设计一套系统指标测试程序,用该程序对采集的数据分析后结果如图6所示。图6所示的是80 MHz系统采样时钟,输入信号是10.2 MHz的单点频信号,输出为2.5 MSPS数据率。可以看出,信噪比(SNR)为71 dB,无杂散动态范围(SDFR)为77 dB,镜像抑制比为96 dB。这说明I,Q的正交度高,这一点是模拟中频接收机无法比拟的。

该中频数字接收机可处理信号带宽达到20 MHz以上,因此能够满足通讯和雷达系统的一般要求,虽然现在流行用FPGA设计数字接收机,但大容量、高速的FPGA价格昂贵。另外,软件设计也较复杂,而ISL5416功能强大,设计灵活,价格适中,因此ISL5416相对FPGA设计具有较大的性价比优势。但在使用时,要注意的是,ISL5416输出数据具有不可恢复性,若工作时钟受干扰或中途切换,输出数据将出错。

ISL5416提供的两个信号RESET是复位信号,SYNCin是全局同步信号,RESET有效使整个芯片停止工作,所有寄存器置默认值,而SYNCin有效则刷新NCO控制字,抽取计数器,则重新启动滤波器。输出数据计数器时钟和混频滤波通道时钟是两个支路时钟。因此,系统电路的时钟和同步信号受干扰或中途切换,用RESET复位,再重新加载数据工作,不能简单用SYNCin来复位。

4 结 语

目前,中频数字化接收机已在通讯和雷达产品中普遍运用,产品的通用性、可靠性、可移植性代表了产品的生命力,也符合软件无线电的思想。本设计的电路能够较好地实现中频数字接收机的总体指标,已在多个雷达产品中实现中频直接采样,而且也实现了米波段射频直接采样数字下变频,性能稳定可靠,实时处理性强。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。