0 引 言

超宽带(Ultra Wide Band,UWB)技术在通信时,不使用载波电路,而是通过发送纳秒级脉冲传输数据的,因此具有发射和接收电路简单,功耗低,多径分辨能力强,穿透力强,隐蔽性好,系统容量大,定位高,对现存通信系统影响小,传输速率快等优势。由于UWB技术具有这些优良独特的技术特性,该技术已普遍受到各国政府的高度重视。

UWB通信系统中必不可少的关键之一是如何产生高带宽信号。由于极窄脉冲含有丰富的频谱,因而产生足够窄的脉冲和适于信道传输的脉冲形状是UWB技术的研究热点和关键所在。从国内外对UWB技术的研究来看,目前已有的UWB脉冲信号实现方式基本上可分为两大类:一类是利用模拟器件来产生所需的极窄脉冲信号;另一类是利用半导体器件的开关特性实现。利用模拟器件产生的窄脉冲通常需要较高的偏置电压并且寄生效应较大,脉冲波形不理想,脉冲功率较大,容易对其他的通信系统产生影响。为了克服模拟器件产生窄脉冲的缺陷,并考虑到UWB通信系统的特殊性,利用开关速度极快的ECL门电路产生窄脉冲相比用模拟器件具有诸多优势,如脉冲波形好,电路简单,便于产品的集成,调试容易,信号功率谱密度低,不会对别的通信系统产生明显影响等。

1 UWB信号的发生

1.1 发生信号形式的选择

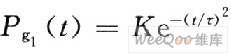

冲激无线电超宽带技术中不使用载波,是直接发送和接收极窄脉冲信号的,所以脉冲信号波形的选择对于UWB通信系统来说至关重要。不管是采用模拟器件,还是数字器件,终发生信号的形式必须适合在无线信道中传输。UWB技术中基本的信号单元是高斯脉冲(Gaussian Pulse),其时域表达式为:

式中:K表示脉冲信号幅度;t为时间;τ是脉冲持续时间,它不仅决定了脉冲宽度,还决定了信号频谱的中心频率和带宽。与其对应的频域表达式为:

式中:f为频率;fc=1/τ是脉冲的中心频率。其时域、频域波形如图1和图2所示。

由高斯脉冲的频谱图可知,该脉冲含有丰富的低频和直流分量,不适宜天线辐射。为了有效传输,UWB信号应含有尽可能多的高频分量。高斯脉冲的导数具备把直流和低频分量转换成高频分量的能力。

高斯单脉冲(Gaussian Monocycle)即一阶高斯脉冲,它是由高斯方程的一阶倒数得出的,其时域表达式为:

与上式对应的频域表达式为:

由高斯单脉冲的频域波形可知,该信号波形含有的直流和低频分量很小,适合在无线信道中传输,且中心频率随脉冲宽度变窄而升高,带宽也随之增加。

1.2 信号发生器的方案研究

基于1.1节的分析,信号发生器的终输出信号形式应为高斯单脉冲。为实现该信号,UWB信号发生器设计成数字模拟混合电路。ECL门电路是半导体器件中速度快的开关电路,也是整个电路的,它的主要作用是产生脉冲宽度极窄的高斯脉冲,但ECL门电路直接输出的信号不适于信道传输,因而在其后接上模拟电路,以对ECL门电路的输出信号进行变换,从而获得UWB通信所需要的高斯单脉冲。图5是UWB信号发生器的逻辑原理框图。

该原理框图由标准时钟、电平转换电路、延时器、延时控制电路、ECL门电路、发送滤波器和脉冲功率放大电路组成。标准时钟产生器产生一定重复周期的矩形脉冲序列。电平转换电路把时钟的TTL电平转换成ECL电平。为了延时,延时器采用ECL电平的延时芯片,控制电路控制延时芯片的迟延时间,使两路信号的延时有一个极短的时间差,这样有时间差的两路信号通过ECL门电路之后便可产生一个宽度与时间差相等的极窄脉冲。ECL门电路是ECL电平的异或门或者与门,它们的反应速度要足够快,通常要求其反应时间不能大于250 ps,且外围电路和传输线都应满足匹配的要求,否则难以得到宽度极窄的理想脉冲。由于ECL门电路的输入信号都是矩形脉冲,因而通过ECL门电路产生的窄脉冲也是矩形脉冲,又因为输出脉冲的低电平为3.2 V,该脉冲必定含有丰富的直流和低频分量,不适于无线传输。为了有效传输信号,通过发送滤波器对脉冲形式进行变换,变成需要的高斯单脉冲。由于ECL高低电平的差值不过800 mV,通过ECL门电路得来的脉冲功率很小,如果要扩大传输距离,则需增大发射功率,这时把已经成形了的高斯单脉冲通过放大电路即可增大发射功率。

1.3 信号发生器的电路设计

UWB信号发生器的实际电路完全按照1.2节中的方案设计。即整体电路主要分为3大部分。部分主要功能是产生极窄脉冲。该部分电路对制作PCB板的要求很高,ECL门电路的两路输入信号要尽可能对称,才会地减少误差,也即输出的脉冲宽度才会接近两路信号的理论延时差。此外,ECL门电路对输出阻抗有特殊要求,都是50 Ω的特殊阻抗,因而在设计传输线时要用微带线理论去设计,以保证输出特性阻抗是50 Ω,这样才不会出现波形较大的失真。

第二部分主要是对部分输出的脉冲进行成形滤波。该部分需要注意的是,运算放大器的速度要足够快,才能对极窄脉冲进行较好的成形,同时相应的匹配电路要尽可能,此外传输线都采用微带线,以保持输入输出阻抗匹配,这里的输入输出阻抗都是标准的50 Ω。

第三部分是对成形后的高斯单脉冲进行放大。该部分的是MMIC(单片微波集成电路),放大电路是可调的,通过改变VCC达到改变放大电流的目的,传输线也都采用微带线,特性阻抗设计成50 Ω,目的是要和第二部分的输出阻抗以及发射天线的特性阻抗匹配,限度地提高发射效率。图6是UWB信号发生器的实际电路图。

2 UWB信号的测试

用Agilent公司的示波器和频谱仪对与图6相对应的印刷电路板测试。示波器的采样率为16 GHz,频谱仪能扫描10 GHz的频谱,测试时两块延时芯片设置的延时差为960 ps,输出端接口采用标准50 Ω阻抗的SMA接头,示波器和频谱仪也设置为50 Ω输入阻抗,测试时采用特性阻抗为50 Ω的传输线,测得的脉冲波形及其频谱如图7,图8所示。

3 结 语

从终输出的脉冲波形可知,脉冲波形较理想,脉冲宽度为1 ns,略大于预设延时差,这主要是制作PCB板时有误差所致,因此要想获得的脉宽,在制作工艺上还有待提高。由于延时差是可控的,因而通过该电路可获得更窄或更宽的脉冲,这是本电路的优势所在。从频谱图可知,该信号的中心频率为1 GHz,-3 dB带宽高达500 MHz,也即分数带宽为50%,符合超宽带信号的要求。此外该信号虽然带宽很宽,但功率谱密度很低,根本不会对其他通信系统产生任何影响,这利于本电路在实际中的应用。

UWB通信系统在短距离通信中应用越来越广泛,但如果要扩大传输距离,则必须增大发射功率,这样就会对其他通信系统,甚至对人体造成影响,这是不允许的,因而如何解决这对矛盾是当今面临的难题。

[1]. ECL datasheet https://www.dzsc.com/datasheet/ECL_2043152.html.

[2]. TTL datasheet https://www.dzsc.com/datasheet/TTL_1174409.html.

[3]. PCB datasheet https://www.dzsc.com/datasheet/PCB_1201640.html.

[4]. SMA datasheet https://www.dzsc.com/datasheet/SMA_1054310.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。