关键词:输出级;运放电路;数模转换器;电流型DAC

引言

近年来,电子通讯市场的发展极其迅速,这给系统中重要的模块—数模转换器(DAC)带来了发展机遇,同时也对DAC设计者提出了同时兼顾高和高速度的挑战。

电流型DAC是基于一系列相互匹配的电流镜,由输入数据控制电流开关对,将电流导向输出端或者互补输出端,因此它具有可以直接驱动负载、速度快、功耗低、面积小等优点,被认为是一个解决高速度要求的较佳方案。为了提高转换,通常可以采用过采样(Oversampling)和sigma-delta(ΣΔ)调制技术。

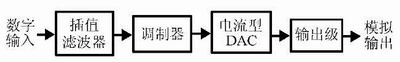

在电流型DAC设计中,输出级设计很重要,它的优劣将直接影响到系统性能指标。如图1所示,典型的ΣΔ电流型DAC中包含了一个数字插值滤波器、一个ΣΔ调制器、一个内嵌的电流型DAC以及输出级电路。常用的输出电路由开关电容(SC)滤波器实现,但从电路设计成本的角度,它有很明显的缺点。这是因为SC滤波器的噪声主要由热噪声(kT)/C决定,所以要提高信噪比就意味着需要更大的片内电容,这不仅大大增加了设计成本,而且在某些应用场合,根本无法实现。而采用连续输出级的ΣΔDAC,就可以避免SC电路热噪声的影响。

本文在对电流型DAC输出级稳定性详细分析的基础上,设计了一种低失真的运放电路,由于避免了采用大容量电容,芯片实现面积减小,同时又提高了系统信噪比,可广泛应用于电流型DAC输出电路中。

输出级原理及稳定性分析

由图1可知,为了将电流型DAC的输出电流转换成电压信号输出,输出级要能实现电流到电压的转换(IVC)。在实际应用中,电流型DAC常采用全差分电流归零(RTZ)电路,以减小码间干扰和降低对时钟上升延和下降延的匹配要求。相应地,输出电路也需要采用差分结构。

为了简化分析,图2给出了能实现IVC的输出级原理图。图2中,虚线框内是电流型DAC的等效电路,其中,Ro、Co分别是电流型DAC的输出电阻和输出电容,Rf、Cf分别是反馈电阻和反馈电容,Vref是外接基准电压。假设电流型DAC的输出阻抗为无穷大,运放为理想情况,那么输出级转移函数为: (1)

(1)

由式(1)可见,电流转换到电压可以由Rf实现。

图2中加入了反馈电容Cf,这是为了使输出级电路稳定,下面给予证明。在无反馈电容Cf时,从图3给出的开环小信号等效电路可得到,电路的输入输出关系为: (2)

(2)

图3无Cf时图2对应的开环小信号电路

从式(2)可看出,由于Rf的加入,结合DAC的输出电容Co,将会引入新的极点: (3)

(3)

这将会引起电路不稳定。当在回路中加入Cf时,输入输出关系变为: (4)

(4)

式中,零、极点分别为: (5)

(5)

从式(5)可以看出,如果加入Cf,并保证: RfCf=RoCo(6)时,零点z可以和极点px2相互抵消,电路稳定性提高。此外,Cf还能和Rf实现简单的滤波。如果需要进一步的滤波,则可以在芯片外部实现。

运放设计

结构设计

图2所示的输出级中,关键的是运放设计,图4是运放电路图。运放的一端接基准电压Vref,以提供共模电压,另一端接电流型DAC的输出。设计中运放必须具有足够高的增益,这样才能保证其同相和反相输入端电压差小,也就是使DAC中电流源的漏源极电压Vds和Vref几乎相等,电流源偏置电路的电流就可以被复制,从而使内部DAC获得较高的。另外考虑到宽输出摆幅的要求,运放采用了两级结构,为了实现高于100dB的增益,并且在5V电源下,获得较好的信噪比,级采用了Folded Cascode结构。

运放的输出级采用了共源放大器,以获得较高的输出摆幅,但其缺点是当负载电阻较小时,M12的偏置电流有可能下降。因此,在运放中加入了一个由M3~M10构成的gm稳定电路。当M12的偏置电流下降时,M3和M12的栅电压下降,使得流过M3的电流降低,由于M9的电流保持恒定,所以此时流过M6的电流增大,再通过M11的镜像,使M12的电流上升,从而起到了补偿作用。设计中为了减小失真,gm稳定环路的跨导需要精心设计。

小信号分析

图4所示的运放是两级结构,为了提高稳定性,加入Miller电容Cc进行频率补偿。为排除由Miller补偿所产生右半平面零点的影响,加入了电阻Rz。为了确定运放的直流增益、单位增益带宽以及Cc和Rz的取值,图5给出了运放的小信号等效图。由图5可计算出运放的直流增益为:A(0)=gm1gmmultR1RL (7)

图5运放的小信号等效图

其中gm1为运放级中M1跨导, ,k、m、h如图4中所示,有

,k、m、h如图4中所示,有

其中W和L为相应MOS管的宽和长。并得到运放的单位增益带宽为:

GB=gm1/Cc (8)

为了消除Cc造成的右半平面零点的影响,可令: (9)

(9)

即将零点推至无穷远处,保证了电路的稳定。此时,运放的转移特性可以表示为: (10)

(10)

为了获得60度的相位裕量,并且A(0)很大时,由式(10)可以得到: (11)

(11)

设p3~pn>>GB,则有: (12)

(12)

由式(12)得,|p2|>1.73GB。设计时取|p2|>2GB,所以Cc取值应满足: (13)

(13)

应该指出,上述分析并没考虑运放级和输出级的镜像零极点。如果考虑级的镜像零极点: (14)

(14)

式中,C3为图4中A点的寄生电容。从式(14)可知,z3部分抵消了p3的影响。设计时需要使p3和z3的值大于GB。

再考虑到运放输出级的镜像零极点。由如图6所示的小信号原理图可知,输入和输出关系为: (15)

(15)

其中gmo为输出级跨导,并有: (16)

(16)

由式(16)可知,运放输出级中电流镜的镜像极点将影响gmo,从而影响运放的带宽和相位裕量,设计时需要通过模拟进行调整。

噪声分析

运放结构中,来自第二级的噪声在除以级增益后可以忽略,主要考虑级噪声,总噪声则为: (17)

(17)

其中,k为玻尔兹曼常数,T为温度,µ为器件载流子迁移率,Cox为单位面积氧化层电容,ID为MOS管的漏源极电流,K为与工艺有关的常数。式(17)中,前一部分为热噪声,而后一部分为闪烁噪声。为了尽可能地降低运放噪声,设计时可根据式(17),来选择输入级M1和M2的宽长比,并且进一步确定M14、M15以及M20、M21管的尺寸。

模拟结果

采用0.6μm工艺进行Hspice模拟验证,根据应用要求,模拟时采用电源电压为5V,负载电阻为1kΩ。图7为运放的环路频率特性。由上图可见,运放的直流增益为108dB,环路带宽为30MHz,环路相位裕量为60度,这表明电路是稳定的。

图8为输出噪声电压(模拟时积分到100GHz),其值为29µVrms。此外,在输出摆幅为±1.4V时,模拟得到运放的谐波失真电压(至9次谐波)为3.62µVrms。因此,本文所设计的运放的THD+N高达104.8dB。

图7 环路频率特性

图8 运放的输出噪声电压

结论

设计了一种应用于电流型DAC的输出电路。在详细分析输出级稳定性的基础上,对其中的运放电路进行了重点设计,模拟结果表明运放在输出为1rms时,THD+N为104.8dB;直流增益为108dB,环路带宽为30MHz,环路相位裕量为60度。此电路具有占用芯片面积小、噪声低等优点,适用于高电流型DAC的输出级中。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。